# Implementation Agreement For Generation 2.0 100G Long-Haul DWDM Transmission Module – Electromechanical (Gen.2 MSA-100GLH)

Premininaly Draft IA # OIF-MSA-100GLH-EM-02.0

Date Approved August 27, 2013

Implementation Agreement created and approved by the Optical Internetworking Forum www.oiforum.com

Working Group: Physical and Link Layer (PLL) Working Group

TITLE: Implementation Agreement for Generation 2.0 100G Long-Haul DWDM

**Transmission Module – Electromechanical (MSA-100GLH)**

SOURCE: TECHNICAL EDITOR

Atul Srivastava, Ph. D. NEL America, Inc.

250 Pehie Ave., Suite 706 Saddle Brook, NJ 07663 Phone: +1-201-556-1770

Email: <u>Srivastava@nel-america.com</u>

**WORKING GROUP VICE CHAIR**

Karl Gass

TriQuint Semiconductor

Phone: +1-505-844-8849

Email: iamthedonutking@mac.com

**WORKING GROUP CHAIR**

David R. Stauffer, Ph. D.

**IBM** Corporation

1000 River Road, MC 862J Essex Jct., VT 05452 Phone: +1-802-769-6914 Email: dstauffe@us.ibm.com

**ABSTRACT:** This Implementation Agreement specifies key electromechanical aspects of a 100G Long-Haul DWDM Transmission Module, for applications such as 100G PM-QPSK long-haul DWDM transmission. Key aspects include: module mechanical dimensions, electrical connector and pin assignment, module hardware signaling pins, high-speed electrical characteristics, power supply, power dissipation, and management interface.

The OIF is an international non profit organization with over 90 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements.

With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with IEEE 802.1, IEEE 802.3, IETF, IP-MPLS Forum, IPv6 Forum, ITU-T SG13, ITU-T SG15, MEF, ATIS-OPTXS, ATIS-TMOC, TMF and the CFP MSA Group.

For additional information contact: The Optical Internetworking Forum, 48377 Fremont Blvd., Suite 117, Fremont, CA 94538 510-492-4040 Φ info@oiforum.com

www.oiforum.com

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

#### © 2011 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

# 1 Table of Contents

| 1          | Ta           | ible of Contents                                            | 4            |

|------------|--------------|-------------------------------------------------------------|--------------|

| 2          | Li           | st of Figures                                               | 5            |

| <u>3</u>   |              | st of Tables                                                |              |

| 4          | D            | ocument Revision History                                    | 6            |

| <u>5</u>   |              | troduction                                                  |              |

| 6          | Fu           | unctional Description                                       | 7            |

| 7          | M            | odule Management Interface Description                      | 10           |

| 8          | El           | ectrical Specifications                                     | 10           |

|            | <u>8.1</u>   | Operating Case Temperature                                  | 10           |

|            | 8.2          | Electrical Power Supply and Power Dissipation               | 10           |

|            | <b>8.3</b>   | High Speed Pin Electrical Specifications                    |              |

|            | 8.4          | Control Pins (non-MDIO) Functional Description              | 13           |

|            | <u>8.5</u>   | Alarm Pins (non-MDIO) Functional Description                |              |

|            | <b>8.6</b>   | Module Management Interface Pins (MDIO) Description         | 19           |

|            | 8.7          | Hardware Signaling Pin Electrical Specifications            |              |

|            | <u>8.8</u>   | Hardware Signaling Pin Timing Specifications                | 23           |

| <u>9</u>   | $\mathbf{M}$ | echanical Specifications                                    | 25           |

|            | <u>9.1</u>   | Mechanical Overview                                         | 25           |

|            | <u>9.2</u>   | Electrical Connector                                        | 25           |

|            | <u>9.3</u>   | Module Dimensions                                           | 28           |

|            | <u>9.4</u>   | Host System Dimensions                                      | 33           |

|            | <u>9.5</u>   | Module Optical Fiber Ports                                  | 34           |

|            | <u>9.6</u>   | Pin Assignment                                              | 35           |

| <u>1(</u>  | <u>0</u>     | References                                                  | 39           |

|            | <u>10.1</u>  | Normative references                                        | 39           |

|            | <u>10.2</u>  | Informative references                                      | 39           |

| <u>1</u> : | <u>1</u>     | Appendix A: Glossary                                        | 39           |

| <u>12</u>  | 2            | Appendix B: Open Issues / current work items                | 40           |

| 13         | <u>3</u>     | Appendix C: List of companies belonging to OIF when documen | <u>ıt is</u> |

| aı         | org          | ved                                                         | 41           |

# 2 <u>List of Figures</u>

| FIGURE 1: 100G LONG-HAUL DWDM TRANSMISSION MODULE (MSA-100GLH) FUNCTION  |    |

|--------------------------------------------------------------------------|----|

| DIAGRAM                                                                  |    |

| FIGURE 2: HIGH SPEED I/O FOR DATA AND CLOCKS                             | 12 |

| FIGURE 3: TRANSMITTER DISABLE (TX DIS) TIMING DIAGRAM                    | 15 |

| FIGURE 4: MODULE LOW POWER (MOD LOPWR) TIMING DIAGRAM                    | 16 |

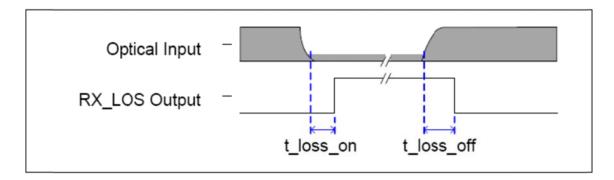

| FIGURE 5: RECEIVER LOSS OF SIGNAL (RX_LOS) TIMING DIAGRAM                | 18 |

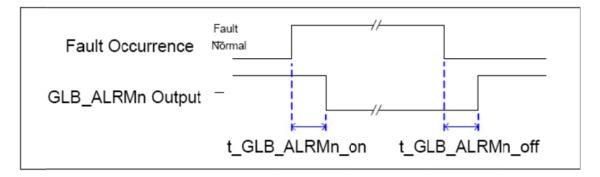

| FIGURE 6: GLOBAL ALARM (GLB ALRMN) TIMING DIAGRAM                        | 19 |

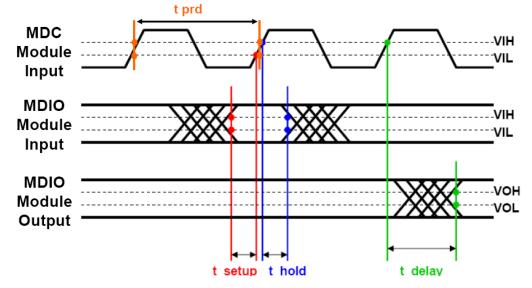

| FIGURE 7: MODULE MDIO & MDC TIMING DIAGRAM                               | 21 |

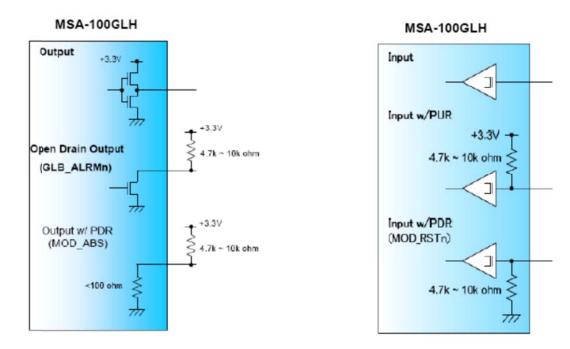

| FIGURE 8: REFERENCE +3.3V LVCMOS INPUT/OUTPUT TERMINATIONS               | 22 |

| FIGURE 9: REFERENCE MDIO INTERFACE TERMINATION                           | 23 |

| FIGURE 10: MSA-100GLH SIMPLIFIED START-UP FLOW DIAGRAM                   |    |

| FIGURE 11: HIROSE FX10A-168S-SV(83) RECEPTACLE CONNECTOR ASSEMBLY        | 26 |

| FIGURE 12: HIROSE FX10A-168P-SV(83) HEADER CONNECTOR ASSEMBLY            | 27 |

| FIGURE 13: FX10 CONNECTOR ALIGNMENT                                      |    |

| FIGURE 14: MSA-100GLH NON-CONDUCTIVE SHEET DIMENSIONS                    |    |

| FIGURE 15: MSA-100GLH FLATTOP MECHANICAL DIMENSIONS - BOTTOM/SIDE VIEWS  | 30 |

| FIGURE 16: MSA-100GLH FLATTOP MECHANICAL DIMENSIONS - TOP VIEW           | 31 |

| FIGURE 17: MECHANICAL DIMENSIONS OF MSA-100GLH WITH INTEGRATED HEAT SINK |    |

| FIGURE 18: MSA-100GLH WITH INTEGRATED HEAT SINK - TOP VIEW               | 33 |

| FIGURE 19: RECOMMENDED HOST SYSTEM LAYOUT FOR MSA-100GLH                 | 34 |

| FIGURE 20: MSA-100GLH OPTICAL FIBER PORT LOCATION AND DIMENSIONS         | 35 |

| 3 <u>List of Tables</u>                                                  |    |

| TABLE 1: MSA-100GLH PERFORMANCE SPECIFICATIONS                           | 10 |

| TABLE 2: MSA-100GLH REFERENCE CLOCK (REFCLK) CHARACTERISTICS             |    |

| TABLE 3: OPTIONAL TXMCLK AND RXMCLK CHARACTERISTICS                      |    |

| TABLE 4: MSA-100GLH CONTROL PINS (NON-MDIO)                              |    |

| TABLE 5: MSA-100GLH ALARM PINS (NON-MDIO)                                |    |

| TABLE 6: MSA-100GLH MDIO MANAGEMENT INTERFACE PINS                       |    |

| TABLE 7: 3.3V LVCMOS ELECTRICAL CHARACTERISTICS                          |    |

| TABLE 8: 1.2V LVCMOS ELECTRICAL CHARACTERISTICS                          |    |

| Table 9: Hardware Signaling Pins Timing Parameters Summary               |    |

| TABLE 10: MSA-100GLH PIN-MAP.                                            |    |

| TABLE 11: MSA-100GLH ELECTRICAL CONNECTOR - ROW B PIN DESCRIPTION        |    |

| TABLE 12: MSA-100GLH ELECTRICAL CONNECTOR - ROW A PIN DESCRIPTION        |    |

Working Group: Physical and Link Layer (PLL) Working Group

SOURCE: TECHNICAL EDITOR

Atul Srivastava, Ph. D. NEL America, Inc. 250 Pehie Ave., Suite 706 Saddle Brook, NJ 07663 Phone: +1-201-556-1770

Email: Srivastava@nel-america.com

**WORKING GROUP VICE CHAIR**

Karl Gass TriQuint Semiconductor

Phone: +1-505-844-8849

Email: <u>iamthedonutking@mac.com</u>

**WORKING GROUP CHAIR**

David R. Stauffer, Ph. D. IBM Corporation 1000 River Road, MC 862J Essex Jct., VT 05452 Phone: +1-802-769-6914 Email: dstauffe@us.ibm.com

DATE: January 14, 2013

| Revision            | Date          | Change Notes                                                       | Ву         |

|---------------------|---------------|--------------------------------------------------------------------|------------|

| Premininaly draft   | Jan. 14, 2013 | <u> </u>                                                           |            |

| Premininaly draft B | Apr. 23, 2013 | Location of PIN A1 indicate in                                     | Atul       |

|                     |               | Figure 15, 17 and 19                                               | Srivastava |

|                     |               | 9.6 Pin Assignment<br>Information delete of Appendix D<br>and E    |            |

|                     |               | 10.2 Informative references [I5] Revision update to latest version |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

|                     |               |                                                                    |            |

This document details an Implementation Agreement (IA) for a Generation 2.0 100G Long-Haul DWDM Transmission Module – Electromechanical (MSA-100GLH) for optical line interface applications. While specifically addressing 100G PM-QPSK long-haul DWDM transmission applications [I1], this IA strives to remain modulation format and data rate agnostic whenever practical to maximize applicability to future market requirements.

This IA specifies key electromechanical aspects of the Generation 2.0 100G Long-Haul DWDM Transmission Module (hereafter termed MSA-100GLH) that include the following: module mechanical dimensions, electrical connector and pin map, module hardware signaling pins, high-speed electrical characteristics, power supply, power dissipation, and management interface.

# **6** Functional Description

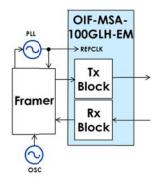

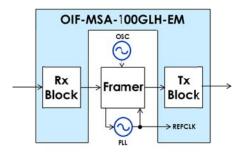

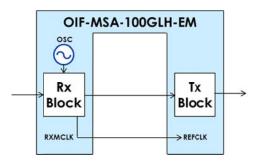

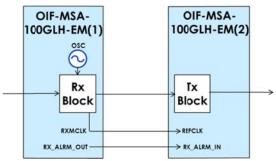

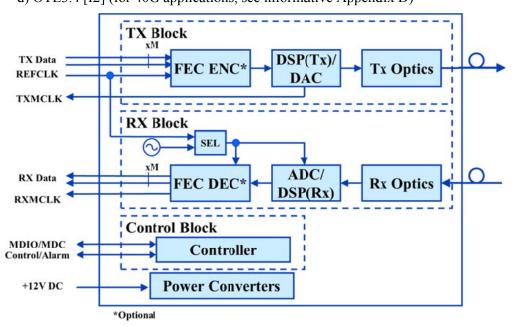

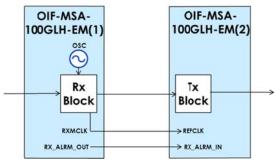

A functional block diagram of the MSA-100GLH is illustrated in Figure 1: Generation 2.0 100G Long-Haul DWDM Transmission Module (MSA-100GLH) Functional Diagram

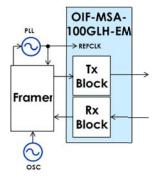

Figure 1A: Application Diagram 1 for 1 MSA Transponder w **Framer**

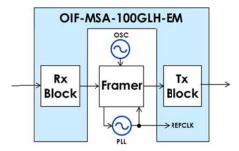

Figure 1B: Application Diagram 2 for 1 MSA Re-generator w Framer

Figure 1C: Application Diagram 3 for 1 MSA Re-generator w/o Framer

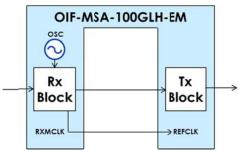

Figure 1D: Application Diagram 4 for 2 MSA Re-generator w/o Framer

Note: In normal operation, Tx have to use Rx recovered clock for REFCLK in Figure 1C and 1D.

- . Key module functions include transmitter optics, receiver optics, interface ICs, module controller supporting an MDIO/MDC management interface, and power conversion for a single +12V DC power supply from the host. The MSA-100GLH is not hot pluggable, but is fastened to the host system board during line card assembly. The interface IC(s) and module electrical interface are generically specified to allow vendor specific customization of multilane "M-lane"  $\sim$  11 Gbit/s interfaces. Module electrical interfaces include but are not limited to the following:

- a) Simple bit multiplex

- b) OTL4.10 [I2]

- c) SFI-S [I3]

d) OTL3.4 [12] (for 40G applications, see informative Appendix D)

Figure 1: Generation 2.0 100G Long-Haul DWDM Transmission Module (MSA-100GLH) Functional Diagram

Figure 1A: Application Diagram 1 for 1 MSA Transponder w Framer

Figure 1B: Application Diagram 2 for 1 MSA Re-generator w Framer

Figure 1C: Application Diagram 3 for 1 MSA Re-generator w/o Framer

Figure 1D: Application Diagram 4 for 2 MSA Re-generator w/o Framer

Note: In normal operation, Tx have to use Rx recovered clock for REFCLK in Figure 1C and 1D.

# 7 <u>Module Management Interface Description</u>

The MSA-100GLH utilizes MDIO IEEE 802.3 Clause 45 [N1] for its management interface. The MSA-100GLH MDIO hardware implementation is specified in Section 8.6. The MSA-100GLH MDIO register set specifications are defined in [15]. When multiple MSA-100GLH are connected via a single bus, a particular MSA-100GLH may be selected by using the MDIO Physical Port Address pins.

# 8 <u>Electrical Specifications</u>

# 8.1 Operating Case Temperature

The MSA-100GLH operating case temperature is specified in Table 1.

## 8.2 Electrical Power Supply and Power Dissipation

The MSA-100GLH is powered by a single +12V DC supply from the host board. This power supply is specified in Table 1. All voltages are measured at the electrical connector interface.

The MSA-100GLH power dissipation is specified in Table 1.

**Symbol** Min Max Unit Note **Parameter** Тур +12V DC Supply Voltage 11.4 12.0 ٧ +/- 5%  $V_{CC}$ 12.6 +12V DC Supply Current  $I_{CC}$ 4.0 A Notes 1 & 2 1Hz – 20MHz Power Supply Noise 1 %р-р  $V_{rip}$ Power Dissipation  $P_{w}$ 45 W **Operating Case Temperature** 0 70 °C

**Table 1: MSA-100GLH Performance Specifications**

Note: The parameter min and max values are specified End-of-Life within the overall relevant operating case temperature range. The typical values are referenced to +25°C, nominal power supply, Beginning-of -Life.

Note 1: Maximum current per pin shall not exceed 750mA.

Note 2: Icc max specified for current rating purposes. Normal operating current (Icc) must not exceed Pw / Vcc.

# 8.3 High Speed Pin Electrical Specifications

#### 8.3.1 Transmitter Data (TX)

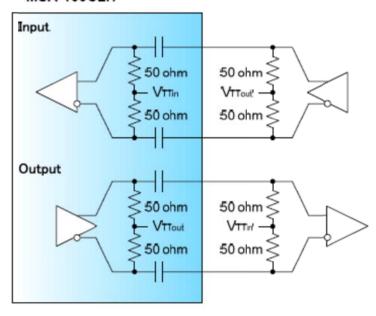

The Transmitter Data (TX) signals shall comply with CEI-11G-MR Low Swing option as per Clauses 9.3.1. and 9.3.1.2 [N2]. Full Swing support is not required. The recommended termination of the TX pins is given in Figure 2.

#### 8.3.2 Receiver Data (RX)

The Receiver Data (RX) signals shall comply with CEI-11G-MR Clause 9.3.3 [N2]. The recommended termination of the RX pins is given in Figure 2.

#### 8.3.3 Reference Clock (REFCLK)

The host shall supply a reference clock (REFCLK) at 1/16 of the electrical lane rate. The host shall optionally supply a reference clock (REFCLK) at 1/64 of the electrical lane rate.

The REFCLK shall be CML differential AC coupled and terminated with 50 Ohm internal  $V_{TT}$  within the MSA-100GLH, as shown in Figure 2. A frequency locked relationship is required between the transmit data lanes (TX/TXDSC) and the reference clock (REFCLK). There is no required phase relationship between the data lanes and the reference clock. The REFCLK frequency shall not deviate from nominal by more than  $\pm 20$  ppm. Detailed reference clock characteristics for the MSA-100GLH are given in Table 2.

### Table 2: MSA-100GLH Reference Clock (REFCLK) Characteristics

| Parameter        | Symbol        | Min | Тур  | Max  | Unit | Notes                     |

|------------------|---------------|-----|------|------|------|---------------------------|

| Impedance        | $Z_{d}$       | 80  | 100  | 120  | Ω    |                           |

| Frequency        | f             |     | 1/16 |      |      | Of electrical lane rate - |

|                  |               |     |      |      |      | default                   |

|                  |               |     | 1/64 |      |      | Of electrical lane rate - |

|                  |               |     |      |      |      | optional                  |

| Frequency        | $\Delta f$    | -20 |      | +20  | ppm  |                           |

| Stability        |               |     |      |      |      |                           |

| Differential     | $ m V_{DIFF}$ | 400 |      | 1600 | mV   | Peak-to-Peak Differential |

| Voltage          |               |     |      |      |      |                           |

| Clock Duty Cycle | CDC           | 40  |      | 60   | %    |                           |

| Clock Rise/Fall  | $t_{\rm r/f}$ | 200 |      | 1250 | ps   | 1/64 electrical lane rate |

| Time             |               | 50  |      | 315  | ps   | 1/16 electrical lane rate |

#### MSA-100GLH

Figure 2: High Speed I/O for Data and Clocks

# 8.3.4 Transmitter Monitor Clock (TXMCLK)

The MSA-100GLH optionally may supply a transmitter monitor clock (TXMCLK). This clock is intended to be used as a reference for measurements of the module optical transmit signal. If provided, the clock shall operate at 1/8 of the transmitter optical symbol rate for 32Gb

applications<sup>1</sup>. This rate is optimized for triggering high-speed sampling scopes. Clock termination is shown in Figure 2. TXMCLK characteristics are summarized in Table 3.

#### 8.3.5 Receiver Monitor Clock (RXMCLK)

The MSA-100GLH optionally may supply a receiver monitor clock (RXMCLK). This clock is intended to be used as a reference for measurements of the module receive data. If provided, the clock shall operate at 1/16 of the receiver electrical lane data rate. The RXMCLK may optionally operate at 1/64 of the receiver electrical lane data rate. Clock termination is shown in Figure 2. RXMCLK characteristics are summarized in Table 3.

**Parameter** Symbol Min Typ Max Unit **Notes** Impedance 80 100 120  $Z_d$ Ω Of TX optical symbol rate Frequency -1/8 **TXMCLK** - default Frequency -Of RX electrical lane data 1/16 **RXMCLK** rate - default Of RX electrical lane data 1/64 rate - optional Output Peak-to-Peak Differential  $V_{\rm DIFF}$ 400 1600 mV Differential Voltage Clock Duty Cycle **CDC** 40 60 %

Table 3: Optional TXMCLK and RXMCLK Characteristics

# 8.4 Control Pins (non-MDIO) Functional Description

The control functions between a host and a MSA-100GLH are conducted through a set of dedicated, non-data hardware signal pins on the 168-pin electrical connector and via an MDIO interface. The signal pins work together with the MDIO interface to form a complete HOST/MSA-100GLH management interface. Upon module initialization, the control functions are available. Pins allocated to control functions in the 168-pin electrical connector are listed in Table 4

<sup>&</sup>lt;sup>1</sup> For 40G applications, other clock rates may be necessary for operating with available test equipment.

#### Table 4: MSA-100GLH Control Pins (non-MDIO)

| Pin<br># | Symbol    | Description                                                                                   | I<br>/<br>O | Logic          | "H"                  | "L"                  | Pull-up<br>/down       |

|----------|-----------|-----------------------------------------------------------------------------------------------|-------------|----------------|----------------------|----------------------|------------------------|

| B20      | PRG_CNTL1 | Programmable Control 1 Default: TRXIC_RSTn, TX & RX ICs reset, "0": reset, "1" or NC: enabled | I           | 3.3V<br>LVCMOS | Per MDIC<br>document | Pull-Up <sup>1</sup> |                        |

| B19      | PRG_CNTL2 | Programmable Control 2 For Future Use                                                         | Ι           | 3.3V<br>LVCMOS |                      |                      | Pull-Up <sup>1</sup>   |

| B18      | PRG_CNTL3 | Programmable Control 3<br>For Future Use                                                      | I           | 3.3V<br>LVCMOS |                      |                      | Pull-Up <sup>1</sup>   |

| B13      | PM_SYNC   | Performance Monitoring Sync<br>Rising edge synchronizes PM<br>statistics counters             | Ι           | 3.3V<br>LVCMOS |                      |                      | Pull-Down <sup>2</sup> |

| B11      | TX_DIS    | Transmitter Disable "0": transmitter enabled "1" or NC: transmitter disabled                  | Ι           | 3.3V<br>LVCMOS | Disable              | Enable               | Pull-Up <sup>1</sup>   |

| B10      | MOD_LOPWR | Module Low Power "0": power-on enabled "1" or NC: module in low power (safe) mode             | I           | 3.3V<br>LVCMOS | Low<br>Power         | Enable               | Pull-Up <sup>1</sup>   |

| В9       | MOD_RSTn  | ` /                                                                                           |             | 3.3V<br>LVCMOS | Enable               | Reset                | Pull-Down <sup>2</sup> |

Note 1: Pull-Up resistor (4.7k - 10kOhm) is located within the MSA-100GLH.

Note 2: Pull-Down resistor (4.7k - 10kOhm) is located within the MSA-100GLH.

# 8.4.1 Programmable Control Pins (PRG\_CNTLs)

The Programmable Control pins (PRG\_CNTL) allow the host to program certain MSA-100GLH control functions via a hardware pin. The intention is to allow for maximum design and debug flexibility. The default setting for Control 1 is control of the Transmit & Receive Reset. Controls 2 and 3 are for future use.

## 8.4.1.1 Programmable Control 1 Pin (PRG\_CNTL1)

Programmable Control 1 Pin (PRG\_CNTL1) is an input pin from the host, operating with programmable logic. It is pulled up in the MSA-100GLH. It can be re-programmed over MDIO registers to another MDIO control register while the module is in any steady state except Reset. The default function is Transmit & Receive circuitry reset (TRXIC\_RSTn) with active-low logic. When TRXIC\_RSTn is asserted (driven low), the digital transmit and receive circuitry is reset clearing all FIFOs and/or resetting all CDRs. When de-asserted, the digital transmit and receive circuitry shall resume normal operation.

### 8.4.1.2 Programmable Control 2 Pin (PRG\_CNTL2)

Programmable Control 2 Pin (PRG\_CNTL2) is an input from the host, operating with programmable logic. It is pulled up in the MSA-100GLH. It can be re-programmed over MDIO registers to another MDIO control register while the module is in any steady state except Reset. It is reserved for future use.

# 8.4.1.3 Programmable Control 3 Pin (PRG\_CNTL3)

Programmable Control 3 Pin (PRG\_CNTL3) is an input from the host, operating with programmable logic. It is pulled up in the MSA-100GLH. It can be re-programmed over MDIO registers to another MDIO control register while the module is in any steady state except Reset. It is reserved for future use.

#### 8.4.1.4 Performance Monitoring Synchronization (PM\_SYNC)

The Performance Monitoring Synchronization pin (PM\_SYNC) is an input from the host. The purpose of this pin is to provide a synchronization pulse from the host time reference source for synchronizing module-level performance monitoring data collection with host system performance monitoring data collection. The default time period of this signal is 1 second. Use of PM SYNC is optional for the MSA-100GLH.

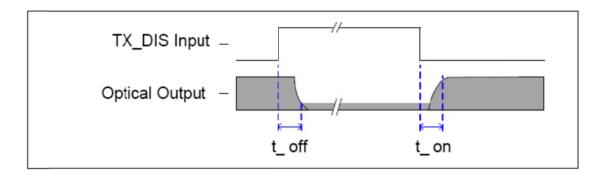

#### 8.4.1.5 Transmitter Disable Pin (TX\_DIS)

The Transmitter Disable pin (TX\_DIS) is an input from the host, operating with active-high logic. This pin is pulled up in the MSA-100GLH. When TX\_DIS is asserted, all of the optical outputs inside a MSA-100GLH shall be switched off. When this pin is de-asserted, optical transmitters shall be switched on according to a predefined TX power-on process defined by module vendor specification. The timing diagram for TX\_DIS pin is illustrated in Figure 3. Values for t\_off and t on are application specific and not specified in this IA.

Figure 3: Transmitter Disable (TX\_DIS) Timing Diagram

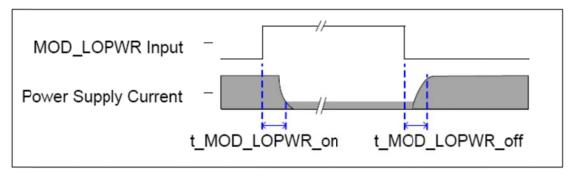

#### 8.4.1.6 Module Low Power Pin (MOD\_LOPWR)

The Module Low Power pin (MOD\_LOPWR) is an input from the host, operating with active-high logic. It is pulled up in the MSA-100GLH. When MOD\_LOPWR is asserted, the MSA-100GLH shall be in the low power state and will stay in the low power state as long as it is asserted. When de-asserted, the MSA-100GLH shall initiate the High-Power-Up process.

In Low Power mode, the MSA-100GLH shall communicate via the MDIO management interface. While the module is in Low Power mode, it has a maximum power consumption of 6W.

The timing diagram for the MOD\_LOPWR pin is illustrated in Figure 4. Values for t\_MOD\_LOPWR\_on and t\_MOD\_LOPWR\_off are application specific and not specified in this IA.

Figure 4: Module Low Power (MOD\_LOPWR) Timing Diagram

### 8.4.1.7 Module Reset Pin (MOD\_RSTn)

The Module Reset pin (MOD\_RSTn) is an input from the host, operating with active-low logic. This pin is pulled down in the MSA-100GLH. When MOD\_RSTn is asserted (driven low), the MSA-100GLH enters the Reset state. When de-asserted, the MSA-100GLH exits the Reset state and shall begin an initialization process as part of the overall module start-up sequence.

### 8.5 Alarm Pins (non-MDIO) Functional Description

Alarm indications from the MSA-100GLH to the host are conducted through a set of dedicated, non-data hardware signal pins on the 168-pin electrical connector and via an MDIO interface. The signal pins work together with the MDIO interface to form a complete HOST/MSA-100GLH management interface. Upon module initialization, the alarm indication functions are available. Pins allocated to alarm functions in the 168-pin electrical connector are listed in Table 5.

Table 5: MSA-100GLH Alarm Pins (non-MDIO)

| Pin<br># | Symbol          | Description                                                | I<br>/<br>O | Logic                              | "H"    | "L"     | Pull-<br>up/down       |

|----------|-----------------|------------------------------------------------------------|-------------|------------------------------------|--------|---------|------------------------|

| B16      | PRG_ALRM1       | Programmable Alarm 1 set over<br>MDIO                      | 0           | 3.3V<br>LVCMOS                     |        |         |                        |

| B15      | PRG_ALRM2       | Programmable Alarm 2 set over MDIO                         | 0           | 3.3V<br>LVCMOS                     |        |         |                        |

| B14      | PRG_ALRM3       | Programmable Alarm 3 set over<br>MDIO                      | О           | 3.3V<br>LVCMOS                     |        |         |                        |

| B8       | RX_LOS          | Receiver Loss of Signal                                    | О           | 3.3V<br>LVCMOS                     | LOS    | OK      |                        |

| A78      | MOD_ABS         | Module Absent "0": module present "1" or NC: module absent | 0           | GND                                | Absent | Present | Pull-Down <sup>1</sup> |

| В7       | GLB_ALRMn       | Global Alarm                                               | 0           | 3.3V<br>LVCMOS<br>w/ Open<br>Drain | OK     | Alarm   | Note 2                 |

| A11      | RX_ALRM_O<br>UT | Receiver Alarm transfer output for Re-generator mode       | О           | 3.3V<br>LVCMOS                     | Alarm  | OK      |                        |

| A12      | RX_ALRM_IN      | Receiver Alarm transfer input for<br>Re-generator mode     | I           | 3.3V<br>LVCMOS                     | Alarm  | OK      |                        |

Note 1: Pull-down resistor (<1000hm) is located within the MSA-100GLH. A Pull-Up resistor should be located on the host.

Note 2: Pull-Up resistor on host.

# 8.5.1 Programmable Alarm Pins (PRG\_ALRMs)

The Programmable Alarm pins enable the host system to program MSA-100GLH supported alarms to dedicated hardware pins.

## 8.5.1.1 Programmable Alarm 1 Pin (PRG\_ALRM1)

Programmable Alarm 1 Pin (PRG\_ALRM1) is an output to the host, operating with programmable logic. It can be re-programmed over MDIO registers to another MDIO alarm register while the MSA-100GLH is in any steady state except Reset. The default function is High Power On (HIPWR ON) indicator with active-high logic.

## 8.5.1.2 Programmable Alarm 2 Pin (PRG\_ALRM2)

Programmable Alarm 2 Pin (PRG\_ALRM2) is an output to the host, operating with programmable logic. It can be re-programmed over MDIO registers to another MDIO alarm register while the MSA-100GLH is in any steady state except Reset. The default function is Module Ready (MOD READY) indicator with active-high logic.

The default function MOD\_READY is used by the MSA-100GLH during the module initialization. When asserted, it indicates the MSA-100GLH has completed the necessary initialization process and is ready to transmit and receive data.

# 8.5.1.3 Programmable Alarm 3 Pin (PRG\_ALRM3)

Programmable Alarm 3 Pin (PRG\_ALRM3) is an output to the host, operating with programmable logic. It can be re-programmed over MDIO registers to another MDIO alarm register while the MSA-100GLH is in any steady state except Reset. The default function is Module Fault (MOD FAULT) indicator with active-high logic.

The default function MOD\_FAULT is used by the MSA-100GLH during module initialization. When asserted, it indicates the MSA-100GLH has entered into a fault state.

## 8.5.2 Receiver Loss of Signal Pin (RX\_LOS)

The Receiver Loss of Signal pin (RX\_LOS) is an output to the host, operating with active-high logic. When asserted, it indicates received optical power in the MSA-100GLH is lower than the expected value. The optical power at which RX\_LOS is asserted is application specific and specified by the host system or module vendor. The timing diagram for the RX\_LOS pin is illustrated in Figure 5. Values for t\_loss\_on and t\_ loss\_off are application specific and not specified in this IA.

Figure 5: Receiver Loss of Signal (RX\_LOS) Timing Diagram

# 8.5.3 Module Absent Pin (MOD\_ABS)

The Module Absent (MOD\_ABS) pin is an output from the MSA-100GLH to the host. It is pulled up on the host board and is pulled down to ground in the MSA-100GLH. MOD\_ABS asserts a "Low" condition when the MSA-100GLH is plugged into a host socket. MOD\_ABS is asserted "High" when the MSA-100GLH is physically absent from a host socket.

# 8.5.4 Global Alarm Pin (GLB\_ALRMn)

The Global Alarm pin (GLB\_ALRMn) is an output to the host, operating with active-low logic. When GLB\_ALRMn is asserted (driven low), it indicates that a Fault/Alarm/Warning/Status (FAWS) condition has occurred. It is driven by the logical OR of all fault, alarm, warning and status conditions latched in the latched registers. Masking Registers are provided so that GLB-ALRMn may be programmed to assert only for specific fault/alarm/warning/status conditions. It is recommended that the host board be designed to support high-priority event handling service to respond to the assertion of this pin. Upon the assertion of this pin, the host event handler identifies the source of the fault by reading the latched registers over the MDIO interface. The reading action clears the latched registers, which in turn causes the MSA-100GLH to de-assert (driven high) the GLB ALRMn pin.

The timing diagram for the GLB\_ALRMn pin is illustrated in Figure 6. Values for t\_GLB\_ALRM\_on and t\_GLB\_ALRMn\_off are application specific and not specified in this IA.

Figure 6: Global Alarm (GLB\_ALRMn) Timing Diagram

Note: In this Figure the Fault Occurrence is shown transitioning to a "Normal" status. In order for this transition to occur, a read of the alarm register must have occurred such that the fault has been received.

# 8.5.5 Receiver Alarm transfer output for Re-generator mode Pin (RX\_ALRM\_OUT)

The Receiver Alarm transfer output for Re-generator mode Pin (RX\_ALRM\_OUT) is an output to another connected MSA-100GLH for Re-generator application, operating with active-low logic. When RX\_ALRM\_OUT is asserted (driven low), it indicates that condition such as a Loss Of Signal/Loss Of Frame has occurred at RX. The timing diagram for the RX\_ALRM\_OUT pin is application specific and not specified in this IA.

# 8.5.6 Receiver Alarm transfer input for Re-generator mode Pin (RX\_ALRM\_IN)

The Receiver Alarm transfer input for Re-generator mode Pin (RX\_ALRM\_IN) is an input from another connected MSA-100GLH for Re-generator application, operating with active-low logic. When RX\_ALRM\_IN is asserted (driven low), the MSA-100GLH shall generate AIS(Alarm Indication Signal) condition, or similar signal at the TX. The timing diagram for the RX\_ALRM\_IN pin is application specific and not specified in this IA.

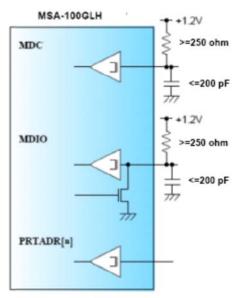

# 8.6 Module Management Interface Pins (MDIO) Description

The MSA-100GLH supports control, alarm and monitoring functions via dedicated hardware pins and via an MDIO bus. The MSA-100GLH MDIO electrical interface consists of 7 pins: 1 pin for MDIO, 1 pin for MDC, and 5 MDIO Physical Port Address pins. MDC is the MDIO clock line driven by the host. MDIO is the bidirectional data line driven by both the host and module, depending upon the data direction. Pins allocated to instantiate the MDIO interface in the MSA-100GLH electrical connector are listed in Table 6.

### Table 6: MSA-100GLH MDIO Management Interface Pins

| Pin<br># | Symbol  | Description                        | I<br>/<br>O | Logic          | "H" | "L" | Pull-up<br>/down |

|----------|---------|------------------------------------|-------------|----------------|-----|-----|------------------|

| A28      | MDIO    | Management Data I/O bi-directional | I<br>/<br>O | 1.2V<br>LVCMOS |     |     |                  |

| A27      | MDC     | MDIO Clock                         | I           | 1.2V<br>LVCMOS |     |     |                  |

| B21      | PRTADR0 | MDIO Physical Port Address bit 0   | I           | 1.2V<br>LVCMOS |     |     |                  |

| B22      | PRTADR1 | MDIO Physical Port Address bit 1   | I           | 1.2V<br>LVCMOS |     |     |                  |

| B23      | PRTADR2 | MDIO Physical Port Address bit 2   | I           | 1.2V<br>LVCMOS |     |     |                  |

| B24      | PRTADR3 | MDIO Physical Port Address bit 3   | I           | 1.2V<br>LVCMOS |     |     |                  |

| B25      | PRTADR4 | MDIO Physical Port Address bit 3   | I           | 1.2V<br>LVCMOS |     |     |                  |

# 8.6.1 Management Data Input/Output Pin (MDIO)

The MDIO specification is defined in IEEE 802.3 Clause 45 [N1]. The MSA-100GLH shall support 4.0 Mbit/s maximum data rate. The MSA-100GLH uses an MDIO with 1.2V LVCMOS logic.

# 8.6.2 Management Data Clock Pin (MDC)

The host specifies a maximum MDC rate of 4.0 MHz and MSA-100GLH hence shall support a maximum MDC rate up to 4.0 MHz. The timing diagram for the MDIO and MDC pins is illustrated in Figure 7: Module MDIO & MDC Timing Diagram

The MSA-100GLH shall support a minimal setup ( $t_{setup}$ ) and hold ( $t_{hold}$ ) time in its MDIO implementation (see Table 9).

Figure 7: Module MDIO & MDC Timing Diagram

Note: Measured at Module MDIO & MDC pins.

# 8.6.3 MDIO Physical Port Address Pins (PRTADRs)

The MDIO Physical Port Address pins (PRTADRs) are used by the host system to address all of the MSA-100GLHs contained within its management domain. PRTADR0 corresponds to the LSB in the physical port addressing scheme. The 5-pin Physical Port Address lines are driven by the host to set the module Physical Port Address which should match the address specified in the MDIO Frame. It is recommended that the Physical Port Addresses not be changed while the MSA-100GLH is powered on.

# 8.7 Hardware Signaling Pin Electrical Specifications

#### 8.7.1 Control & Alarm Pins: 3.3V LVCMOS Electrical Characteristics

The hardware control and alarm pins specified as 3.3V LVCMOS functionality described above shall meet the electrical characteristics described in Table 7. Figure 8 illustrates the recommended reference pin input and output terminations.

Parameter Symbol Min Typ Max Unit Supply Voltage VCC 3.2 3.3 3.4 V V Input High Voltage VIH 2 VCC+0.3 Input Low Voltage VIL V -0.3 0.8 Input Leakage Current IIN -10 +10 μΑ Output High Voltage (I<sub>OH</sub>=-100 μA) VOH VCC-0.2 V Output Low Voltage (I<sub>OL</sub>= 100 μA) VOL 0.2

**Table 7: 3.3V LVCMOS Electrical Characteristics**

Figure 8: Reference +3.3V LVCMOS Input/Output Terminations

### 8.7.2 MDIO Interface Pins: 1.2V LVCMOS Electrical Characteristics

The MDIO pins specified as 1.2V LVCMOS functionality described above shall meet the electrical characteristics described in Table 8. Figure 9 illustrates the recommended reference pin input and output terminations.

| Parameter             | Symbol | Min  | Тур | Max  | Unit |

|-----------------------|--------|------|-----|------|------|

| Input High Voltage    | VIH    | 0.84 | -   | 1.5  | V    |

| Input Low Voltage     | VIL    | -0.3 | -   | 0.36 | V    |

| Input Leakage Current | IIN    | -100 | -   | +100 | μΑ   |

| Output High Voltage   | VOH    | 1.0  | -   | 1.5  | V    |

| Output Low Voltage    | VOL    | -0.3 | -   | 0.2  | V    |

| Output High Current   | IOH    | -    | -   | -4   | mA   |

| Output Low Current    | IOL    | +4   | -   | -    | mA   |

| Input Capacitance     | Ci     | -    | -   | 10   | рF   |

**Table 8: 1.2V LVCMOS Electrical Characteristics**

Figure 9: Reference MDIO Interface Termination

Note: MDC pull-up resistor is optional.

Note: Host termination resistor value of 560 Ohms is recommended. This value provides the best balance of performance for both open-drain and active tri-state driver in the module. Host termination resistor values below 560 Ohms are allowed, to a minimum of 250 Ohms, but this degrades driver performance. Host termination resistor values above 560 Ohms are allowed, but this degrades open-drain driver performance.

# 8.8 Hardware Signaling Pin Timing Specifications

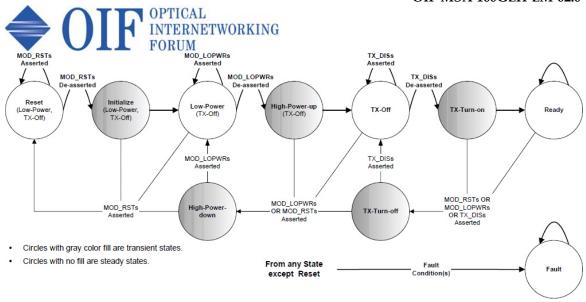

The MSA-100GLH is designed to have a tightly coupled interface with host systems. A simplified overview of the recommended start-up sequence is illustrated in Figure 10. This Figure indicates steady state conditions, transient state conditions and associated signaling flags to indicate state transitions. A complete description is defined in the MDIO management interface specification [I5].

Figure 10: MSA-100GLH Simplified Start-Up Flow Diagram

The MSA-100GLH is designed to support a range of optical transport applications. Many of the timing parameters associated with the module hardware control and alarm pins are application specific and thus are not specified in this IA. A summary of the timing parameters for the MSA-100GLH is given in Table 9.

Table 9: Hardware Signaling Pins Timing Parameters Summary

| Parameter                                | Symbol          | Min | Max | Unit | Notes                                           |

|------------------------------------------|-----------------|-----|-----|------|-------------------------------------------------|

| Transmitter Disabled (TX_DIS asserted)   | t_off           |     |     |      | Application specific. Defined by module vendor. |

| Transmitter Enabled (TX_DIS de-asserted) | t_on            |     |     |      | Application specific. Defined by module vendor. |

| MOD_LOPWR on                             | t_MOD_LOPWR_on  |     |     |      | Application specific. Defined by module vendor. |

| MOD_LOPWR off                            | t_MOD_LOPWR_off |     |     |      | Application specific. Defined by module vendor. |

| Module Reset Assert                      | MOD_RSTn        |     |     |      | Application specific. Defined by module vendor. |

| Module Reset De-assert                   | MOD_RSTn        |     |     |      | Application specific. Defined by module vendor. |

| Module Absent                            | MOD_ABS         |     |     |      | Application specific. Defined by module vendor. |

| Receiver Loss of Signal<br>Assert Time   | t_loss_on       |     |     |      | Application specific. Defined by module vendor. |

| Receiver Loss of Signal                  | t_loss_off      |     |     |      | Application specific.                           |

| De-assert Time         | Oltom            |     |     |    | Defined by module     |

|------------------------|------------------|-----|-----|----|-----------------------|

|                        |                  |     |     |    | vendor.               |

| Global Alarm Assert    | t_GLB_ALRMn_on   |     |     |    | This is a logical     |

| Delay Time             |                  |     |     |    | "OR" of associated    |

|                        |                  |     |     |    | MDIO alarm &          |

|                        |                  |     |     |    | status registers. See |

|                        |                  |     |     |    | MDIO spec for         |

|                        |                  |     |     |    | details.              |

| Global Alarm De-assert | t_GLB_ALRMn_off  |     |     |    | This is a logical     |

| Delay Time             |                  |     |     |    | "OR" of associated    |

|                        |                  |     |     |    | MDIO alarm &          |

|                        |                  |     |     |    | status registers. See |

|                        |                  |     |     |    | MDIO spec for         |

|                        |                  |     |     |    | details.              |

| Management Interface   | $t_{prd}$        | 250 |     | ns | MDC is 4 MHz rate;    |

| Clock Period           |                  |     |     |    | duty cycle =          |

|                        |                  |     |     |    | 50% ± 10% (typ.)      |

| Host MDIO setup time   | ${ m t_{setup}}$ | 10  |     | ns |                       |

| Host MDIO hold time    | $t_{hold}$       | 10  |     | ns |                       |

| Module MDIO delay      | ${ m t_{delay}}$ |     | 175 | ns |                       |

| time                   |                  |     |     |    |                       |

| Performance            |                  |     |     |    | Default period=1 sec. |

| Monitoring             |                  |     |     |    | ; min high/low time   |

| Synchronization        |                  |     |     |    | = 100msec.            |

| (PM_SYNC) (optional)   |                  |     |     |    |                       |

# 9 Mechanical Specifications

#### 9.1 Mechanical Overview

The MSA-100GLH is designed to be assembled into a host system line card. The MSA-100GLH is electrically connected to the host line card by a 168 position connector specified herein and is physically fastened to the host line card by mounting screws through the host line card PCB. The MSA-100GLH supports two optical fiber pigtails, one for optical transmit and one for optical receive. These optical fiber pigtails are terminated and attached to host line card face plate. The MSA-100GLH is not designed to be hot-pluggable. Its power and initialization sequencing in the host line card are specified by the host line card and transponder vendors.

## 9.2 Electrical Connector

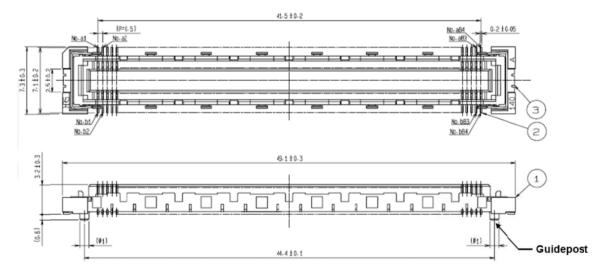

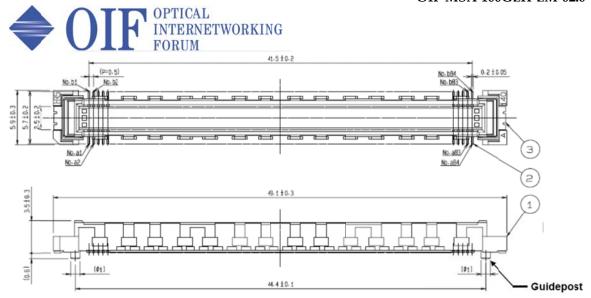

The Hirose FX10A-168P/S-SV(83) connector assembly [N3] is specified for the host line card – MSA-100GLH electrical connector. This connector is a two component (header, receptacle), 168 position, board mounted style assembly. It meets CEI-11G-MR [N2] signal integrity performance and provides 4mm - 8mm mated stack height flexibility by header component changes only, i.e. the MSA-100GLH receptacle component remains fixed. Detailed mechanical specifications and layout design application notes may be found at [N3].

The Hirose FX10B-168P/S-SV(83) connector assembly [N3] is also specified as an option for the host line card – MSA-100GLH electrical connector. The FX10A connector style has guidepost

features whereas the FX10B style does not. The FX10A and FX10B components are mate compatible and may be interchanged. Manufacturers can select either FX10A or FX10B version as appropriate for their design flow.

#### 9.2.1 Module Electrical Connector

The MSA-100GLH electrical connector is the Hirose FX10A-168S-SV(83) receptacle connector assembly [N3] illustrated in Figure 11. Pin orientation is also indicated in Figure 11. The Hirose FX10B-168S-SV(83) receptacle is also an option for the MSA-100GLH electrical connector.

Figure 11: Hirose FX10A-168S-SV(83) Receptacle Connector Assembly

### 9.2.2 Host Electrical Connector

The host line card electrical connector is the Hirose FX10A-168P-SV(83) header connector assembly[N3] illustrated in Figure 12. Pin orientation is also indicated in Figure 12. The Hirose FX10B-168P-SV(83) header is also an option for the host line card electrical connector.

Figure 12: Hirose FX10A-168P-SV(83) Header Connector Assembly

# 9.2.3 Host-Module Connector Alignment

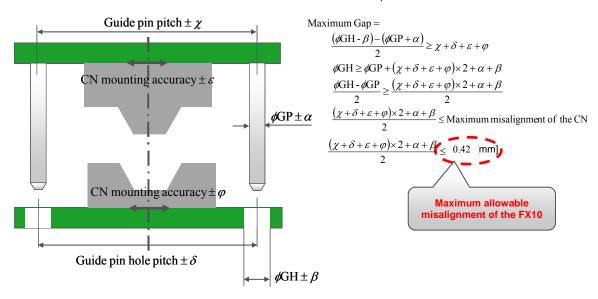

For alignment of host – MSA 100GLH connector mating, misalignment should be smaller that the maximum allowable misalignment value of the connector (CN) mating. Maximum gap between the connector guide pin (GP) and the PCB guide pin hole (GH) is:

Maximum Gap =

$$\frac{\phi GH - \phi GP}{2} \le \text{Maximum misalignment of the CN}$$

to assure CN mating after inserting guide pins into the guide pin hole. If

Maximum Gap =

$$\frac{\phi GH - \phi GP}{2} \ge \text{Maximum misalignment of the CN}$$

this may cause connector and contact deformation. Tolerance of GP and GH is defined in Figure 13. Maximum allowable misalignment should be  $\leq 0.42$ mm for FX10.

Maximum Gap should be

Figure 13: FX10 Connector Alignment

#### 9.3 Module Dimensions

Two options are specified for the MSA-100GLH mechanical dimensions:

- 1) Flattop

- 2) Integrated Heat Sink

The flattop option is specified to allow customization of the MSA-100GLH bolt-on heat sink for supporting a wide array of optical transport applications. With this option, the bolt-on heat sink is specified by the host system designer, allowing maximum flexibility in their system design while maintaining a common module form factor.

The integrated heat sink option is specified to simplify the host system design and supports module thermal performance per the maximum power consumption specified in Section 8.2.

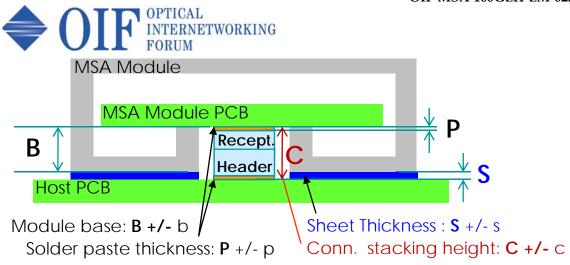

Mechanical dimensions of the MSA-100GLH with non-conductive sheet are specified in Figure 14. If a non-conductive sheet is used, the thickness is specified as  $0.15 \pm 0.05$ mm.

Module and Host PCB dimensions and tolerances in mm.

#### Figure 14: MSA-100GLH Non-conductive Sheet Dimensions

Note: The module vendor must ensure the module connector receptacle component is placed to enable the module to properly mate with the host connector header when the minimum height header component (i.e. C=4mm) is used by the host.

# 9.3.1 Flattop

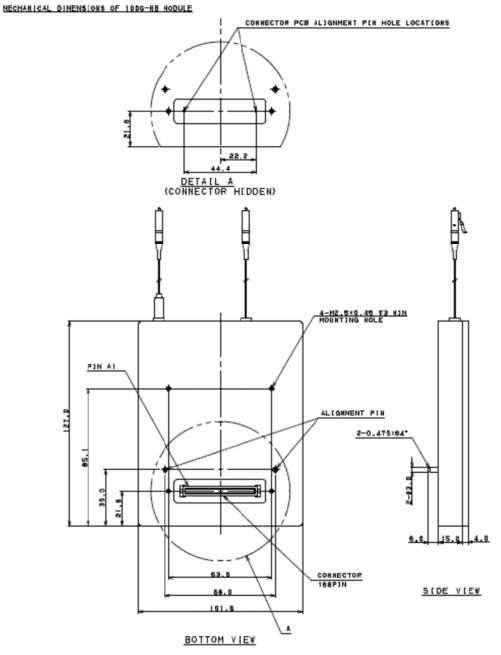

Mechanical dimensions of the MSA-100GLH flattop module are specified in Figure 15. The maximum module size is specified as: 101.6mm x 127.0mm (4" x 5")

Figure 15 also specifies the receptacle connector position, connector guide pin locations and module mounting hole locations.

Figure 15: MSA-100GLH Flattop mechanical dimensions - bottom/side views

The module heat sink mounting hole locations for the flattop option are specified in Figure 16. These mounting holes are not applicable to the MSA-100GLH with an integrated heat sink.

Figure 16: MSA-100GLH Flattop mechanical dimensions - top view

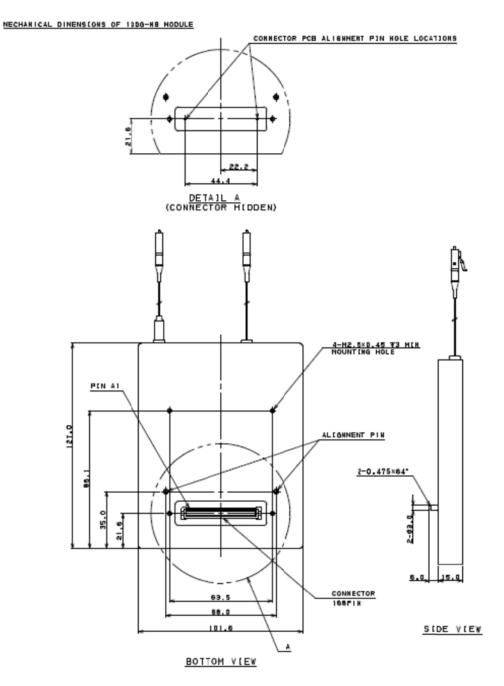

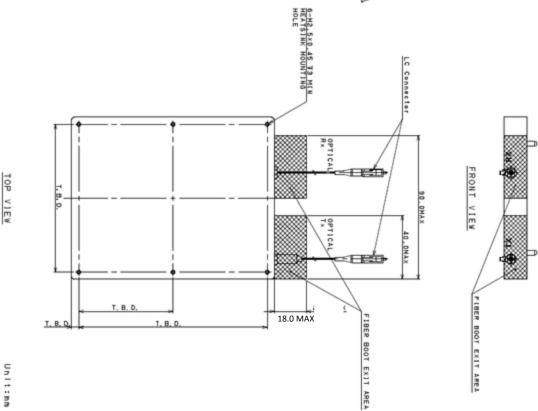

# 9.3.2 Integrated Heat Sink

Mechanical dimensions of the MSA-100GLH with integrated heat sink are specified in Figure 17. The maximum module size is specified as: 101.6mm x 127.0mm (4" x 5")

Figure 17 also specifies the receptacle connector position, connector guide pin locations and module mounting hole locations.

Figure 17: Mechanical Dimensions of MSA-100GLH with Integrated Heat Sink

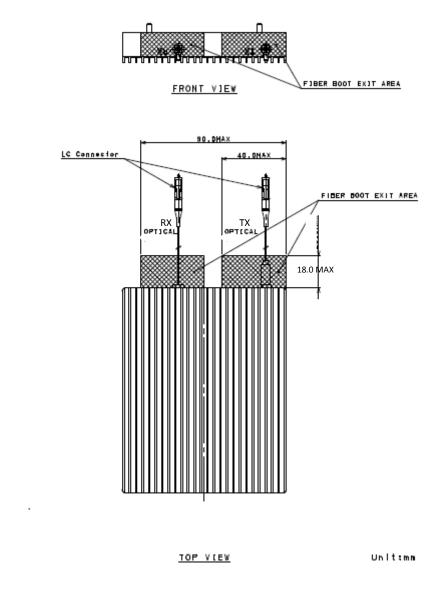

The top view of the MSA-100GLH is illustrated in Figure 18. The integrated heat-sink fin orientation and dimensions are module-vendor specific and are not specified in this document. However, the module height is required to fit within the maximum height dimension specified in Figure 17.

Figure 18: MSA-100GLH with Integrated Heat Sink - top view

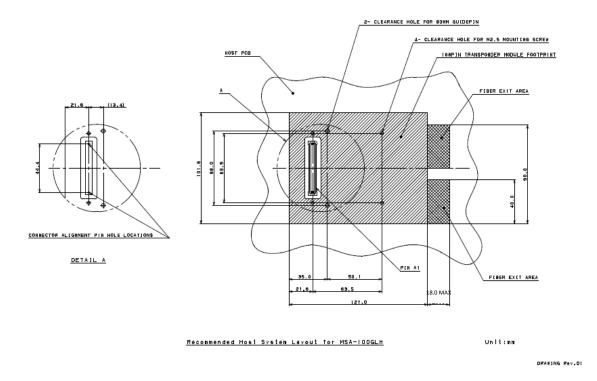

# 9.4 Host System Dimensions

The recommended host system dimensions including host board layout are given in Figure 19. PCB design guidelines for the Hirose FX10 connector assembly may be found at Reference [I4].

Figure 19: Recommended Host System Layout for MSA-100GLH

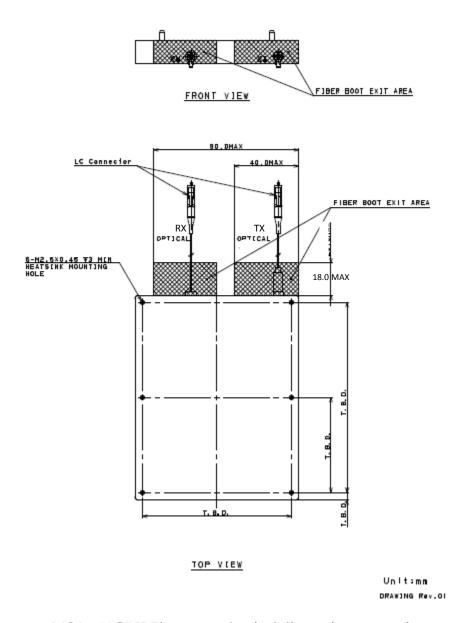

# 9.5 Module Optical Fiber Ports

The MSA-100GLH optical transmit and receive fiber pigtail port location, dimensions and orientation are specified in Figure 20. The fiber pigtail type, length and connector type parameters are vendor specified and not specified in this document. The fiber boot exit area is solely for the purpose of indicating where the fibers are to exit the module side-wall with fiber boots for strain relief.

Figure 20: MSA-100GLH Optical Fiber Port Location and Dimensions

# 9.6 Pin Assignment

The MSA-100GLH electrical connector has 168 pin positions that are arranged in a dual-row assembly. The pin assignment is specified in Table 10. Detailed description of the pin assignment is given in Table 11 and Table 12. The pin orientation is illustrated in Figure 17.

# Table 10: MSA-100GLH Pin-Map (Note: Pins for future use (FFU) should be left unconnected on both the host board and the MSA module)

| _   |           |    |    |             |

|-----|-----------|----|----|-------------|

| B84 | 12V       | A8 | 34 | 12V         |

| B83 | 12V       | A8 | 33 | 12V         |

| B82 | 12V       | A8 | 32 | 12V         |

| B81 | 12V_GND   | A8 | 31 | 12V_GND     |

| B80 | 12V GND   | A8 | 30 | 12V GND     |

| B79 | 12V_GND   | A7 | 79 | 12V_GND     |

| B78 |           | A7 | 78 |             |

| B77 | TXMCLKn   | A7 |    | GND         |

| B76 |           | A7 | 76 | RXMCLKn     |

| B75 |           | A7 |    | GND         |

|     | GND       |    |    | RXMCLKp     |

| B73 |           | A7 |    | GND         |

| B72 |           | A7 |    | RX0n        |

| B71 |           | A7 |    | GND         |

|     | GND       | A7 |    | RX0p        |

| B69 |           | A  | _  | GND         |

| B68 |           | A  |    | RX1n        |

| B67 |           | A  |    | GND         |

| B66 |           | A  |    |             |

| B65 |           | A6 |    | RX1p<br>GND |

|     | GND       |    |    |             |

|     |           |    |    | RX2n        |

|     | TX2p      | A6 |    | GND         |

|     | GND       |    |    | RX2p        |

| B61 |           | A6 |    | GND         |

|     | GND       | A  |    | RX3n        |

| B59 |           | A5 | 9  | GND         |

|     | GND       | A5 | 8  | RX3p        |

| B57 |           | A5 | )/ | GND         |

|     | GND       |    | 6  |             |

| B55 |           | A5 |    | GND         |

|     | GND       | A5 |    | RX4p        |

| B53 |           |    |    | GND         |

|     | GND       | A5 |    | RX5n        |

|     | TX5p      | A5 |    | GND         |

|     | GND       | A5 |    | RX5p        |

| B49 |           | A4 |    | GND         |

|     | GND       |    |    | RX6n        |

| B47 |           | A4 |    | GND         |

|     | GND       | A4 | 16 | RX6p        |

| B45 |           |    |    | GND         |

| B44 |           | A4 |    | RX7n        |

| B43 | TX7p      | A4 | 13 | GND         |

| B42 | GND       |    |    | RX7p        |

| B41 | TX8n      | A4 | 11 | GND         |

| B40 | GND       | A4 | 10 | RX8n        |

| B39 |           | A3 |    | GND         |

| B38 | GND       | A3 | 38 | RX8p        |

| B37 | TX9n      | A3 | 37 | GND         |

| B36 | GND       | A3 | 36 | RX9n        |

| B35 | TX9p      | A3 |    | GND         |

| B34 |           | A3 | 34 | RX9p        |

| B33 | TXDSCn    | A3 |    |             |

| B32 |           | A3 | 32 | RXDSCn      |

| B31 | TXDSCp    | A3 |    |             |

| B30 | GND       | A3 | 30 | RXDSCp      |

| B29 | REFCLKn   | A2 |    | GND         |

| B28 | GND       | A2 | 28 | MDIO        |

| B27 | REFCLKp   | A2 | 27 | MDC         |

|     | GND       |    |    | GND         |

|     | PRTADR4   | A2 | 25 | VND_IO_A    |

| B24 |           |    | 24 |             |

| B23 | PRTADR2   |    | 23 | VND IO C    |

|     | PRTADR1   | A2 | 22 | VND_IO_D    |

|     | PRTADR0   |    |    | GND         |

|     | PRG_CNTL1 |    |    | VND_IO_E    |

|     | PRG_CNTL2 |    |    | VND_IO_F    |

| B18 | PRG_CNTL3 |    |    | VND_IO_G    |

|     | GND       |    |    | VND_IO_H    |

| B16 |           | A1 |    | GND         |

|     | PRG ALRM2 |    |    | VND IO J    |

|     | PRG_ALRM3 |    |    | VND_IO_K    |

|     | PM_SYNC   |    |    | FFU         |

|     | GND       |    |    | RX ALRM IN  |

| B11 |           | A1 |    | RX ALRM OUT |

| B10 |           | A1 |    | FFU         |

| B9  | MOD_RSTn  | A  |    | FFU         |

| B8  | RX_LOS    | A  |    | FFU         |

| B7  | GLB_ALRMn | A  |    | FFU         |

| B6  | 12V GND   | A  |    | 12V CND     |

| B5  | 12V_GND   | A  | _  | 12V_GND     |

| B4  | 12V GND   | A  |    | 12V_GND     |

| B3  | 12V_GND   | A  |    | 12V_GND     |

| B2  | 12V       | A  | 2  | 12V<br>12V  |

| B1  | 12V       | A  | _  | 12V         |

| ы   | 124       | A  | _  | 12 V        |

|     |           |    |    |             |

# Table 11: MSA-100GLH Electrical Connector - Row B Pin Description

|            | 100G                   | 1/0 | Logic                      | Description                                                                                                                                                                       |

|------------|------------------------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 10000                  | "0  | Logic                      | ·                                                                                                                                                                                 |

| B84<br>B83 |                        |     |                            | +12V Module Supply Voltage                                                                                                                                                        |

| B82        | 12V                    |     |                            |                                                                                                                                                                                   |

| B81<br>B80 |                        |     |                            | +12V Module Supply Voltage Return Ground, can be seperate or tied together with Signal Ground                                                                                     |

| B79        |                        |     |                            |                                                                                                                                                                                   |

| B78        | GND                    |     |                            | Ground                                                                                                                                                                            |

|            | TXMCLKn<br>GND         | 0   | CML                        | Transmit Monitor Clock, negative leg                                                                                                                                              |

| B75        | TXMCLKp                | 0   | CML                        | Transmit Monitor Clock, positive leg                                                                                                                                              |

| B74        | TX0n                   | 1   | CML                        | Transmit Data 0, negative leg                                                                                                                                                     |

| B72        | GND                    |     | 2000                       |                                                                                                                                                                                   |

| B71<br>B70 | TX0p                   | 1   | CML                        | Transmit Data 0, positive leg                                                                                                                                                     |

| B69        | TX1n                   | -1  | CML                        | Transmit Data 1, negative leg                                                                                                                                                     |

| B68        | TX1p                   | 1   | CML                        | Transmit Data 1, positive leg                                                                                                                                                     |

| B66        |                        |     | Oiling                     | Trensmit Cate 1, positive reg                                                                                                                                                     |

| B65<br>B64 | TX2n<br>GND            | _   | CML                        | Transmit Data 2, negative leg                                                                                                                                                     |

|            | TX2p                   | 1   | CML                        | Transmit Data 2, positive leg                                                                                                                                                     |

| B62        | GND                    |     | CMI                        |                                                                                                                                                                                   |

| B61<br>B60 | TX3n<br>GND            | 1   | CML                        | Transmit Data 3, negative leg                                                                                                                                                     |

| B59        | TX3p                   | 1   | CML                        | Transmit Data 3, positive leg                                                                                                                                                     |

| B58<br>B57 | TX4n                   | 1   | CML                        | Transmit Data 4, negative leg                                                                                                                                                     |

| B56        | GND                    |     |                            |                                                                                                                                                                                   |

| B54        | TX4p<br>GND            | 1   | CML                        | Transmit Data 4, positive leg                                                                                                                                                     |

| B53        | TX5n                   | 1   | CML                        | Transmit Data 5, negative leg                                                                                                                                                     |

| B52<br>B51 | TX5p                   | 1   | CML                        | Transmit Data 5, positive leg                                                                                                                                                     |

| B50        | GND                    |     |                            |                                                                                                                                                                                   |

| B49<br>B48 | TX6n<br>GND            | 1   | CML                        | Transmit Data 6, negative leg                                                                                                                                                     |

| B47        | TX6p                   | 1   | CML                        | Transmit Data 6, positive leg                                                                                                                                                     |

| B46        | GND<br>TX7n            | 1   | CML                        | Transmit Data 7, negative leg                                                                                                                                                     |

| B44        |                        |     | Oint                       | Transmit Cata 1, negative leg                                                                                                                                                     |

| B43<br>B42 | ТХ7р                   | 1   | CML                        | Transmit Data 7, positive leg                                                                                                                                                     |

|            | TX8n                   | 1   | CML                        | Transmit Data 8, negative leg                                                                                                                                                     |

|            | GND                    | 1   | CML                        | Transmit Data 8, positive leg                                                                                                                                                     |

| B38        | TX8p<br>GND            | -   | CML                        | Transmit Data 6, positive leg                                                                                                                                                     |

| B37<br>B36 | TX9n<br>GND            | 1   | CML                        | Transmit Data 9, negative leg                                                                                                                                                     |

|            | ТХ9р                   | 1   | CML                        | Transmit Data 9, positive leg                                                                                                                                                     |

| B34        | TXDSCn                 |     | CAR                        | Towns in Death of Change I and the Let (OF) Control of the Change III                                                                                                             |

| B33        |                        | 1   | CML                        | Transmit Deskew Channel, negative leg (SFI-S only, otherwise no connect)                                                                                                          |

| B31        | TXDSCp                 | 1   | CML                        | Transmit Deskew Channel, positive leg (SFI-S only, otherwise no connect)                                                                                                          |

| B30<br>B29 | REFCLKn                | 1   | CML                        | Reference Clock, negative leg                                                                                                                                                     |

| B28        | GND                    |     |                            |                                                                                                                                                                                   |

| B27<br>B26 | REFCLKp<br>GND         | 1   | CML                        | Reference Clock, positive leg                                                                                                                                                     |

| B25        | PRTADR4                |     | 1.2V CMOS                  | MDIO port address bit 4                                                                                                                                                           |

|            | PRTADR3<br>PRTADR2     | -   | 1.2V CMOS<br>1.2V CMOS     | MDIO port address bit 3 MDIO port address bit 2                                                                                                                                   |

| B22        | PRTADR1                | 1   | 1.2V CMOS                  | MDIO port address bit 1                                                                                                                                                           |

|            | PRTADRO<br>PRG_CNTL1   |     | 1.2V CMOS<br>LVCMOS w/ PUR | MDIO port address bit 0 Programmable Control 1 set over MDIO                                                                                                                      |

| B19        | PRG_CNTL2              | 1   | LVCMOS w/ PUR              | Programmable Control 2 set over MDIO                                                                                                                                              |

| B18<br>B17 | PRG_CNTL3              | 1   | LVCMOS w/ PUR              | Programmable Control 3 set over MDIO                                                                                                                                              |

| B16        | PRG_ALRM1              |     | LVCMOS                     | Programmable Alarm 1 set over MDIO                                                                                                                                                |

|            | PRG_ALRM2<br>PRG_ALRM3 |     | LVCMOS<br>LVCMOS           | Programmable Alarm 2 set over MDIO Programmable Alarm 3 set over MDIO                                                                                                             |

| B13        | PM_SYNC                |     |                            | Performance monitoring sync: Rising edge synchronizes PM statistics counters                                                                                                      |

| B12        | GND<br>TX_DIS          |     |                            |                                                                                                                                                                                   |

|            | MOD_LOPWR              |     |                            | Transmitter Disable. "1" or NC = transmitter disabled, "0" = transmitter enabled  Module Low Power Mode. "1" or NC= module in low power (safe) mode, "0"= power-on enabled        |

|            | MOD_RSTn               | 1   | LVCMOS w/ PDR              | Module Reset. "0" resets the module, "1" or NC = module enabled.                                                                                                                  |

|            | RX_LOS<br>GLB_ALRMn    |     | LVCMOS / OD                | Receiver Loss of Optical Signal. "1'= low optical signal, "0"= normal condition Global Alarm. "0": Alarm condition, "1": no alarm condition, Open Drain, Pull Up Resistor on Host |

| B6         | 12V_GND                |     |                            | +12V Module Supply Voltage Return Ground, can be seperate or tied together with Signal Ground                                                                                     |

| B5<br>B4   | 12V_GND<br>12V_GND     | _   |                            |                                                                                                                                                                                   |

| B3         | 12V                    |     |                            | +12V Module Supply Voltage                                                                                                                                                        |

| B2<br>B1   |                        |     |                            |                                                                                                                                                                                   |

| -          |                        |     |                            |                                                                                                                                                                                   |

# Table 12: MSA-100GLH Electrical Connector - Row A Pin Description (Note: Pins for future use (FFU) should be left unconnected on both the host board and the module)

|            | 100G                 | I/O      | Logic            | Description                                                                                                    |

|------------|----------------------|----------|------------------|----------------------------------------------------------------------------------------------------------------|

| A84        |                      |          |                  | +12V Module Supply Voltage                                                                                     |

| A83<br>A82 |                      |          |                  |                                                                                                                |

| A81        | 12V_GND              |          |                  | +12V Module Supply Voltage Return Ground, can be seperate or tied together with Signal Groun                   |

|            | 12V_GND<br>12V_GND   |          |                  |                                                                                                                |

|            | MOD_ABS              | 0        | GND              | Module Absent. "1" or NC = module absent, "0" = module present, Pull Up Resistor on Host                       |

|            | GND<br>DYMCLKs       | 0        | CML              | Ground                                                                                                         |

|            | RXMCLKn<br>GND       | Ŭ        | CIVIL            | Receive Monitor Clock, negative leg                                                                            |

|            | RXMCLKp              | 0        | CML              | Receive Monitor Clock, positive leg                                                                            |

|            | GND<br>RX0n          | 0        | CML              | Receive Data 0, negative leg                                                                                   |

| A71        | GND                  |          |                  |                                                                                                                |

|            | RX0p<br>GND          | 0        | CML              | Receive Data 0, positive leg                                                                                   |

| A68        | RX1n                 | 0        | CML              | Receive Data 1, negative leg                                                                                   |

|            | GND<br>RX1p          | 0        | CML              | Receive Data 1, positive leg                                                                                   |

|            | GND                  | Ŭ        | OWL              | receive bata 1, postare reg                                                                                    |

|            | RX2n                 | 0        | CML              | Receive Data 2, negative leg                                                                                   |

|            | GND<br>RX2p          | 0        | CML              | Receive Data 2, positive leg                                                                                   |

| A61        | GND                  | _        | CMI              |                                                                                                                |

|            | RX3n<br>GND          | 0        | CML              | Receive Data 3, negative leg                                                                                   |

| A58        | RX3p                 | 0        | CML              | Receive Data 3, positive leg                                                                                   |

|            | GND<br>RX4n          | 0        | CML              | Receive Data 4, negative leg                                                                                   |

| A55        | GND                  |          |                  |                                                                                                                |

|            | RX4p<br>GND          | 0        | CML              | Receive Data 4, positive leg                                                                                   |