# Streaming Interface (NPSI) Implementation Agreement

October 18, 2002

Revision 1.0

Chris Bergen Streaming Interface Technical Editor

ZettaCom 2055 Laurelwood Road Santa Clara, CA 95054, USA Phone: +1 408-869-7002 Email: <u>chris@zettacom.com</u> Jeffrey Lynch Streaming Interface Task Group Chair & Asst Editor

IBM P.O. Box 12195 Research Triangle Park, NC 27709, USA Phone: +1 919-254-4454 Email: jjlynch@us.ibm.com

Copyright © 2002 The Network Processing Forum (portions copyright Optical Internetworking Forum © 2000,2001) All Rights Reserved.

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the NPF, except as needed for the purpose of developing NPF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the NPF or its successors or assigns.

THIS DOCUMENT AND THE INFORMATION CONTAINED HEREIN IS PROVIDED ON AN "AS IS" BASIS WITHOUT ANY WARRANTY OF ANY KIND. THE INFORMATION, CONCLUSIONS AND OPINIONS CONTAINED IN THE DOCUMENT ARE THOSE OF THE AUTHORS, AND NOT THOSE OF NPF. THE NPF DOES NOT WARRANT THE INFORMATION IN THIS DOCUMENT IS ACCURATE OR CORRECT. THE NPF DISCLAIMS ALL WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED THE IMPLIED LIMITED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

For additional information contact:

The Network Processing Forum, 39355 California Street, Suite 307, Fremont, CA 94538 +1 510 608-5990 phone ✦ info@npforum.org

Streaming Interface Task Group

# **Table of Contents**

| 1. | Scope and Purpose                                                                      | 1     |

|----|----------------------------------------------------------------------------------------|-------|

|    | 1.1 System Block Diagram                                                               | 1     |

|    | 1.2 Objectives and Non-objectives for this specification                               | 1     |

| 2. | Normative References                                                                   | 3     |

| 3. | Conventions in this Specification                                                      | 4     |

|    | 3.1 Definitions                                                                        | 4     |

|    | 3.2 Acronyms and Abbreviations                                                         | 5     |

| 4. | Introduction                                                                           | 6     |

| 5. | Architectural Overview                                                                 | 7     |

|    | 5.1 NPSI Reference Model                                                               | 7     |

|    | 5.2 General Features of the NPSI                                                       |       |

|    | 5.2.1 Common Functions                                                                 |       |

|    | 5.2.2 NPE-Framer Mode                                                                  |       |

|    | 5.2.3 NPE-Fabric Mode<br>5.2.4 NPE-NPE Mode                                            |       |

|    | 5.3 Implementation Examples using NPSI                                                 |       |

|    | 5.4 Interface Signals                                                                  |       |

| 6  | NPE-Framer Mode                                                                        |       |

| ю. | NPE-Framer Mode                                                                        | . 1 1 |

| 7. | Common Functions for the NPE-NPE and NPE-Fabric Mode                                   | 12    |

|    | 7.1 Common Data Path Operation                                                         |       |

|    | 7.1.1 Data Framing Formats<br>7.1.1.1 Control Word Field Definitions                   | . 14  |

|    | 7.1.1.2 Data Word Field Definitions                                                    |       |

|    | 7.1.2 Data Transfer Procedure                                                          |       |

|    | 7.1.3 Packet Delineation                                                               |       |

|    | 7.1.4 Error Detection                                                                  | . 19  |

|    | 7.1.5 Training Sequence for Data Path De-skew                                          |       |

|    | 7.2 Common Flow Control Path Operation                                                 |       |

|    | 7.2.1 Flow Control Status Framing<br>7.2.1.1 Training Sequence for Status Path De-skew |       |

|    | 7.2.1.2 Training Sequence for the 4-bit Status Path De-skew                            |       |

|    | 7.3 Loss of Synchronization                                                            |       |

|    | 7.3.1 Loss of Data Path Synchronization (LODS)                                         | . 24  |

|    | 7.3.2 Loss of Status Path Synchronization (LOSS)                                       | . 24  |

| 8. | NPE-Fabric Mode                                                                        | 26    |

|    | 8.1 Functional Description                                                             | . 26  |

|    | 8.2 Data Path Operation                                                                |       |

|    | 8.2.1 Data Framing                                                                     |       |

|    | 8.2.2 Status Not Ready Bit                                                             |       |

|    | 8.2.3 Data Transfer Procedure                                                          |       |

|    | 8.3 Addressing                                                                         | . 21  |

| 8.3.1 Requirements of an NPSI Switch Fabric                                          |      |

|--------------------------------------------------------------------------------------|------|

| 8.3.1.1 Address Swapping Operation                                                   |      |

| 8.3.1.2 Sequence Integrity                                                           |      |

| 8.3.2 Summary of Address Formats                                                     | . 29 |

| 8.3.2.1 Unicast Address Formats                                                      | . 29 |

| 8.3.2.2 Multicast ID Address Formats<br>8.3.2.3 Multicast Bitmap Address Formats     |      |

| 8.3.3 Unicast Addressing                                                             |      |

| 8.3.3.1 Ingress Unicast Addressing                                                   |      |

| 8.3.3.2 Egress Unicast Addressing                                                    |      |

| 8.3.4 Multicast Addressing                                                           |      |

| 8.3.4.1 Multicast ID Addressing (Ingress Only)                                       |      |

| 8.3.4.2 Multicast Bitmap Addressing (Ingress Only)                                   |      |

| 8.3.4.3 Multicast Egress Addressing                                                  |      |

| 8.4 Flow Control                                                                     | . 40 |

| 8.4.1 Flow Control Message Encoding and Framing                                      | . 40 |

| 8.4.2 Flow Control Mechanisms                                                        | . 41 |

| 8.4.3 Link-Level Flow Control                                                        |      |

| 8.4.4 Sub-Port Flow Control                                                          |      |

| 8.4.5 Ingress Flow Control                                                           |      |

| 8.4.5.1 Unicast Flow Control                                                         | . 43 |

| 8.4.5.2 Multicast Flow Control                                                       |      |

| 8.4.5.3 Class-Based Flow Control                                                     | . 43 |

| 8.4.5.4 Global Flow Control                                                          |      |

| 8.4.5.5 Queue Map Flow Control                                                       |      |

| 8.4.6 Egress Flow Control<br>8.4.6.1 Class-Based Flow Control                        | . 45 |

|                                                                                      |      |

| 8.4.7 Flow Control Message Format<br>8.4.7.1 Summary of Flow Control Message Formats |      |

| 8.4.7.2 Ingress Formats                                                              |      |

| 8.4.7.3 Egress Formats                                                               |      |

| 8.4.8 Flow Control Response Requirements                                             |      |

| 8.4.8.1 Link Level Flow Control                                                      | . 51 |

| 8.4.8.2 Class Flow Control                                                           | . 51 |

| 8.4.9 Flow Control of Directed Status                                                | . 51 |

| 8.5 Summary of Start-up Parameters                                                   | . 52 |

| 9. NPE-NPE Mode                                                                      | 53   |

|                                                                                      |      |

| 9.1 Functional Description                                                           | . 53 |

| 9.2 Data Path Operation                                                              | . 53 |

| 9.2.1 Data Framing                                                                   | . 53 |

| 9.2.2 Data Transfer Procedure                                                        | . 54 |

| 9.3 Addressing                                                                       | . 54 |

| 9.4 Flow Control                                                                     | . 54 |

| 9.4.1 Flow Control Message Encoding and Framing                                      |      |

| 9.4.2 Credit Pools                                                                   |      |

| 9.4.3 Pool Status Calendar                                                           |      |

| 9.4.4 Transmission                                                                   |      |

| 9.5 Summary of Start-up Parameters                                                   |      |

|                                                                                      |      |

| 10. Physical Layer                                                                   | .59  |

| 10.1 Data and Status Path DC Specifications                                          | . 59 |

| 10.2 Data and Status Path AC Specifications                                                                                                                                                                                                                                                                           | 60                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

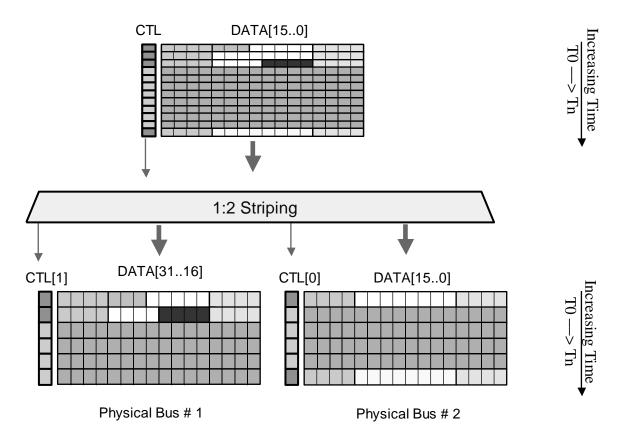

| 11. Appendix A. Aggregation of NPSI Interfaces for Higher Bandwidth Applications (Informative)                                                                                                                                                                                                                        | 63                               |

| <ul> <li>11.1 Introduction</li> <li>11.2 Wide Bus Physical Interface</li> <li>11.3 Operation of the NPSI-W</li> <li>11.4 NPSI-W Signals</li> <li>11.5 De-skewing</li> </ul>                                                                                                                                           | 63<br>64<br>65                   |

| 12. Appendix B: NPE-NPE Narrow Interface Applications                                                                                                                                                                                                                                                                 | 67                               |

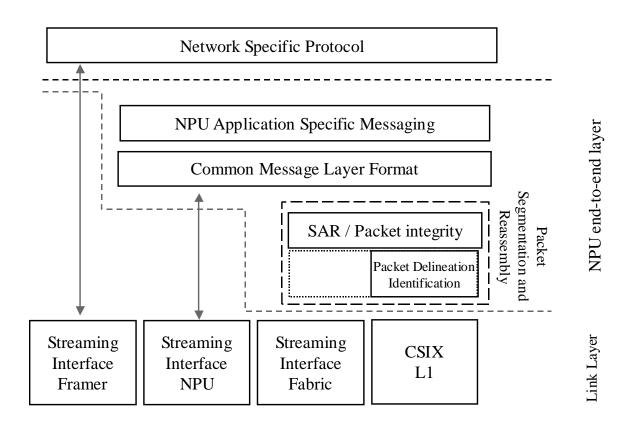

| <ol> <li>Appendix C: NPSI Architectural Relationship Figures (Informative)</li> <li>13.1 NPSI as Part of the NPF Layered Communication Model</li> <li>13.2 NPF Streaming Interface and L2 Reference Model</li> </ol>                                                                                                  | 68                               |

| <ul> <li>14. Appendix D. Features in CSIX-L1 Modified or Not Supported (Informative)</li></ul>                                                                                                                                                                                                                        | 70<br>70<br>70<br>71<br>71<br>71 |

| 15. Appendix E. Differences Between SPI-4 Phase 2 and NPE-NPE mode (Informati                                                                                                                                                                                                                                         | ve)72                            |

| <ul> <li>16. Appendix F: Recommendations to Ensure Interoperability when Implementing NF Fabric Optional Features (Informative)</li> <li>16.1.1 Implementation of Options and their dependencies.</li> <li>16.1.2 Ingress Flow Control Options (NPE)</li> <li>16.1.3 Ingress Flow Control Options (Fabric)</li> </ul> | 73<br>73<br>73                   |

| <ul> <li>16.1.4 Egress Flow Control Options</li></ul>                                                                                                                                                                                                                                                                 | 76<br>76<br>77<br>79<br>79       |

| 16.1.10 Max_Segment_Size Options                                                                                                                                                                                                                                                                                      | 80                               |

### Document revision history

| NPF2001.121.23 | August 13, 2002<br>Version 1.0 of the NPSI (Network Processing Forum Streaming<br>Interface) implementation agreement.                                                      |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NPF2001.121.24 | September 4, 2002<br>Version 1.0 of the NPSI (Network Processing Forum Streaming<br>Interface) implementation agreement. (Corrected typo.)                                  |

| NPF2001.121.25 | October 17, 2002<br>Version 1.0 of the NPSI (Network Processing Forum Streaming<br>Interface) implementation agreement. (Comments in<br>npf2002.540.00 after final ballot.) |

# 1. Scope and Purpose

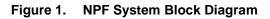

This specification defines the Network Processing<sup>1</sup> Forum (NPF) Streaming Interface (SI) implementation agreement (also, NPSI). The interface supports the transfer of network traffic between a pair of network processing devices, specifically including physical layer (PHY) devices (e.g., SONET framers/mappers or Ethernet MAC's), network processors, network coprocessors, and switch fabrics. It is targeted primarily, though not exclusively, at passing packets between a network processor and an adjacent physical layer, coprocessor, or switch fabric device at OC-192 line rates.

The streaming interface addresses processing in the data path and is complementary to the Look-Aside interface<sup>2</sup>.

# 1.1 System Block Diagram

Figure 1 is a reference diagram used to illustrate the separate efforts within the NPF.

## 1.2 Objectives and Non-objectives for this specification

The objectives for this specification are as follows:

- Provide a standard interface for connecting network processing devices.

- Network processor to network processor

- Network processor to coprocessor

- Network processor to switch fabric

- Coprocessor to switch fabric

- Network processor to framer

- Coprocessor to framer

<sup>&</sup>lt;sup>1</sup> Note that the name is "Network Processing" Forum (and not "Network Processor" Forum).

<sup>&</sup>lt;sup>2</sup> The Look-Aside Interface is a separate task group effort within the NPF.

- Provide a logical protocol that is scalable from 10 Gbps to 40 Gbps.

- Allow for the feasible implementation of a device that converts between NPSI and CSIX-L1 compliant devices.

The following are not objectives for this specification:

• The interface is not required nor specified to drive across a backplane.

# 2. Normative References

The following documents contain provisions, which through reference in this text constitute provisions of this specification. At the time of publication, the editions indicated were valid. All referenced documents are subject to revision, and parties implementing to agreements based on this specification are encouraged to investigate the possibility of applying the most recent editions of the standards indicated below.

[1] System Packet Interface Level 4 (SPI-4) Phase 2: OC-192 System Interface for Physical and Link Layer Devices, Optical Internetworking Forum Implementation Agreement, January 2001<sup>3</sup>.

[2] OIF-SPI5-01.0, System Packet Interface Level 5 (SPI-5): OC-768 System Interface for Physical and Link Layer Devices, Optical Internetworking Forum Implementation Agreement, November 2001<sup>4</sup>.

[3] CSIX-L1: Common Switch Interface Specification-L1, Network Processing Forum Implementation Agreement, August 5, 2000

[4] ANSI/TIA/EIA-644-A-2001, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits", Published February 1, 2001.

Portions of the OI Forum SPI-4 Phase 2 [1] and SPI-5 [2] specifications were used to create this document.

<sup>&</sup>lt;sup>3</sup> At the time of publication of this specification, the SPI-4 Phase 2 specification may be found on the Internet at the following location: <u>http://www.oiforum.com/public/documents/OIF-SPI4-02.0.pdf</u>

<sup>&</sup>lt;sup>4</sup> At the time of publication of this specification, the SPI-5 specification may be found on the Internet at the following location: <u>http://www.oiforum.com/public/documents/OIF-SPI5-01.0.pdf</u>

# 3. Conventions in this Specification

This specification follows the following protocol of terminology:

SHALL indicates that the item is a requirement for conformance to the NPSI specification.

MAY indicates that the item is optional.

SHOULD indicates that the item is not required by this specification, but is offered as implementation guidance.

Footnotes used in this specification are informative only.

A reserved field or bit shall be transmitted as zero and ignored on reception.

If there is a conflict between a state machine diagram and the text of this document (including a table entry), the state machine takes precedence over the text.

Figures (except state diagrams) are informative only.

## 3.1 Definitions

The following terms are used throughout this specification:

| Class:            | A field (up to 8 bits) that is used to discriminate and manage traffic flows. The mechanism for differentiation of services among multiple classes is implementation-specific and beyond the scope of this specification. |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Egress:           | From the switch fabric.                                                                                                                                                                                                   |

| Egress Port:      | An addressable endpoint at an egress NPE-Fabric interface.                                                                                                                                                                |

| Fabric:           | A switch fabric.                                                                                                                                                                                                          |

| Flow:             | A sequence of packets conveyed via the NPF Streaming Interface.                                                                                                                                                           |

| Flow Identifier:  | A set of values designating a flow at specific reference points in the NPF Streaming Interface architecture.                                                                                                              |

| Ingress:          | Toward the switch fabric.                                                                                                                                                                                                 |

| Ingress Port:     | An addressable endpoint at an ingress NPE-Fabric interface.                                                                                                                                                               |

| Logical Port:     | A port that may share a physical instantiation of the NPSI with other logical ports.                                                                                                                                      |

| Multicast:        | The fabric service that delivers a packet to one or more egress ports.                                                                                                                                                    |

| Multicast Bitma   | p:                                                                                                                                                                                                                        |

|                   | A bitmap enumerating a set of egress port identifiers.                                                                                                                                                                    |

| Multicast Flow:   | A flow that uses the multicast service of a fabric.                                                                                                                                                                       |

| Multicast Identif |                                                                                                                                                                                                                           |

|                   | A label designating a set of egress ports of a fabric.                                                                                                                                                                    |

| Network Proces    | ssing Element (NPE):<br>Any device that uses the NPF Streaming Interface as a data path interface to<br>communicate with either a switch fabric, a framer, or another NPE.                                                |

| Packet:           | A service data unit that is conveyed via the NPSI.                                                                                                                                                                        |

| Physical Port:    | A port that is a unique physical instantiation of the NPSI.                                                                                                                                                               |

| Pool:             | An aggregation of ports for flow control.                                                                                                                                                                                 |

| Port:             | An addressable endpoint of the NPSI protocol.                                                                                                                                                                             |

|                   |                                                                                                                                                                                                                           |

Word:

Port Identifier: An address designating a single ingress or egress port of a fabric or a channel of the NPE-NPE interface.

Segment: The payload of a protocol data unit that is transferred across a port.

Sub-port: A logical port within a given physical port.

Sub-port Identifier: An address designating a sub-port (without the physical port information).

Switch Fabric: A facility that accepts packets at multiple ingress ports and delivers them to their designated egress ports.

Unicast: The fabric service that delivers a packet to exactly one egress port.

A flow that uses the unicast service of a fabric.

## 3.2 Acronyms and Abbreviations

A 16-bit value.

The following acronyms and abbreviations are used in this specification

| DIP   | Diagonal Interleaved Parity.                       |

|-------|----------------------------------------------------|

| EOP   | End Of Packet.                                     |

| FIFO  | First-In First-Out (queue).                        |

| HSTL  | High Speed Transceiver Logic.                      |

| IEEE  | Institute of Electrical and Electronics Engineers. |

| I/O   | Input / Output (signal).                           |

| LSB   | Least Significant Bit.                             |

| LVDS  | Low-Voltage Differential Signaling.                |

| LVTTL | Low-Voltage Transistor to Transistor Logic.        |

| MSB   | Most Significant Bit.                              |

| NPE   | Network Processing Element.                        |

| NPF   | Network Processing Forum.                          |

| NPSI  | Network Processing Forum Streaming Interface.      |

| PHY   | Physical Layer Device.                             |

| SONET | Synchronous Optical Network.                       |

| SOP   | Start Of Packet.                                   |

# 4. Introduction

This document specifies the Network Processing Forum's data path interface, the NPF "Streaming Interface" (NPSI), for the interconnection of network processing devices. Included in the definition of network processing devices are framers, switch fabrics, network processors, and network coprocessors (e.g., classification or encryption coprocessors).

The interface supports the transfer of data for nominally 10 Gbps (OC192) aggregate bandwidth applications between two adjacent devices. It is a point-to-point interface with support for addressing and flow control for multiple framer channels, switch fabric and/or coprocessor destinations and classes, as well as multicast traffic.

The interface defines the link-level requirements, including data framing and packet delineation, flow control, address formats, and error detection.

The interface is applicable to multiple applications, and as such is a combination of multiple interface types. Because of this, the interface requirements are explained in multiple sections as three different NPSI modes, one addressing the requirements for a switch fabric interface, one addressing the requirements for a framer interface, and one addressing the requirements between network processors and coprocessors. A device may choose to implement one or more of these NPSI modes and, as such, should clearly state which NPSI mode or modes it supports.

# 5. Architectural Overview

The NPSI provides for the transfer of data traffic and control information between two adjacent network processing devices. There are three NPSI modes that are described individually due to specific requirements of the application. These three modes are described in the following NPF Streaming Interface (NPSI) Reference Model section.

# 5.1 NPSI Reference Model

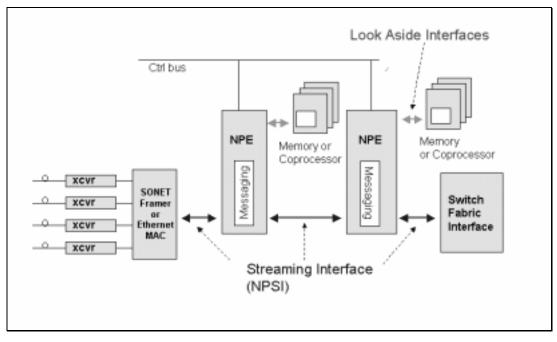

The NPSI supports 3 modes of operation:

- Between an NPE and a Framer (NPE-Framer)

- Between an NPE and a Switch Fabric (NPE-Fabric)

- Between an NPE and an adjacent NPE (NPE-NPE)

Each mode of operation is independent from the other modes of operation. As such, a device that claims conformance to the NPSI should indicate whether the specified interface is conformant to the NPE-Framer mode, NPE-NPE mode, or the NPE-Fabric mode (or more than one of these modes).

The interface is based on SPI-4 Phase 2 and SPI-5, with protocol concepts from CSIX-L1. The interface has a data path and an out-of-band (reverse channel) flow control path, thereby supporting simplex operation. (Two NPSI's are required, one in each direction, for a full-duplex interface. In that case, however, the two NPSI's are independent interfaces, although the two may be implemented on a single device.)

The following reference model identifies that the interface shares many SPI-4 Phase 2 functions, but each mode of operation has operational differences tailored to its specific environment.

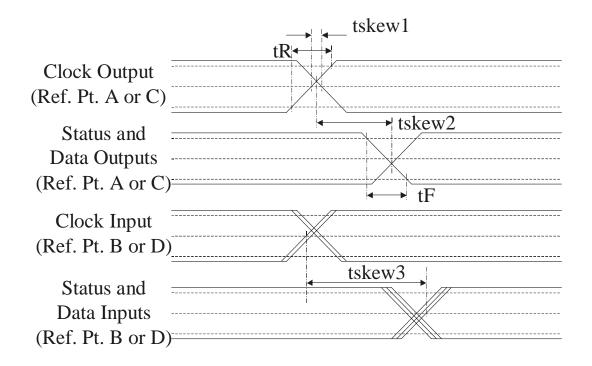

### Figure 2. Streaming Interface Reference Model

## 5.2 General Features of the NPSI

### 5.2.1 Common Functions

The NPSI provides a data path with in-band control and framing information, and an out-of-band status path for flow control information, allowing for the unidirectional transfer ("streaming") of data between two devices.

The NPSI has the following general characteristics:

- Point-to-point connectivity between two adjacent devices

- Data Path:

- 16-bit wide data path

- Source-synchronous, double-edge clocking at 311 MHz (622 Mbps<sup>5</sup> per bit lane<sup>6</sup>) minimum

- LVDS electrically compatible with SPI-4 Phase 2, with support for rates up to 1.3 Gbps and above per bit lane

- In-band data multiplexing and flow control context, packet delineation, and error control coding

- Status (Flow Control) Path:

- 2-bit wide status path

- Source-synchronous, double-edge clocking

- In-band framing and error control coding

- Support for packet and cell-based protocols

- Support for board-level connections of 8 inches FR-4 plus one connector.

#### 5.2.2 NPE-Framer Mode

The NPE-Framer mode of operation of the NPSI is the OI Forum SPI-4 Phase 2 specification [1]. The NPSI makes no changes to the SPI-4 Phase 2 interface.

#### 5.2.3 NPE-Fabric Mode

- Support for up to 4096 egress ports (destinations) with up to 256 classes

- Support for multicast and unicast traffic

- Data Path:

- Support for multiplexing on port and sub-port basis

- Status (Flow Control) Path:

- LVDS electrically compatible with SPI-4 Phase 2, with support for rates up to 1.3 Gbps and above per bit lane

- Signals operate at the full rate of the data path signals

- Link-level flow control (Data Ready indication)

- Directed status messages for flow control

- Support for flow control on port and sub-port basis

- Optional flow control of directed status messages

- Required 2-bit status bus optionally extended to 4 bits

<sup>&</sup>lt;sup>5</sup> Data rates are specified in bps, not Hz. Because the clock is double-edged, stating the data rate is less ambiguous than stating the clock rate.

<sup>&</sup>lt;sup>6</sup> A bit lane is a signal carrying one data bit (i.e., one LVDS differential pair).

### 5.2.4 NPE-NPE Mode

- Support for up to 256 ports (channels) with the ability to scale to a much larger number of ports

- Status (Flow Control) Path:

- LVDS electrically compatible with SPI-4 Phase 2, with support for rates up to 1.3 Gbps and above per bit lane

- Signals operate at the full rate of the data path signals

- Support for the SPI-5 Pool Status Mechanism [2], which allows the flow control granularity to be different from the full data multiplexing capability

## **5.3 Implementation Examples using NPSI**

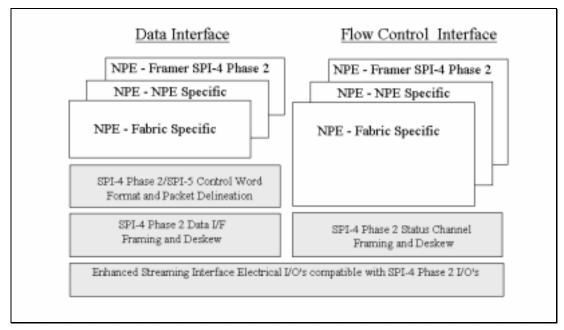

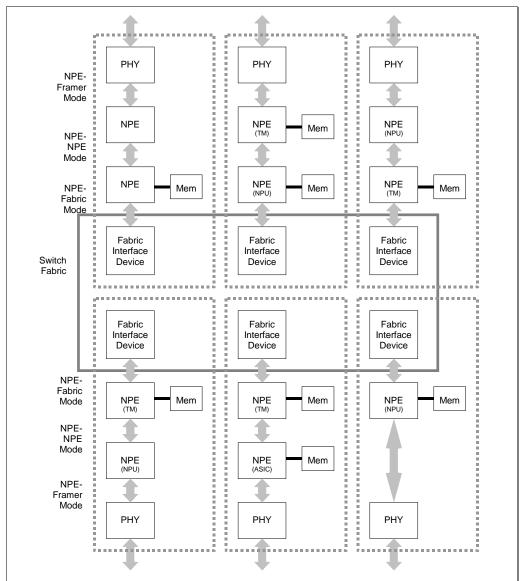

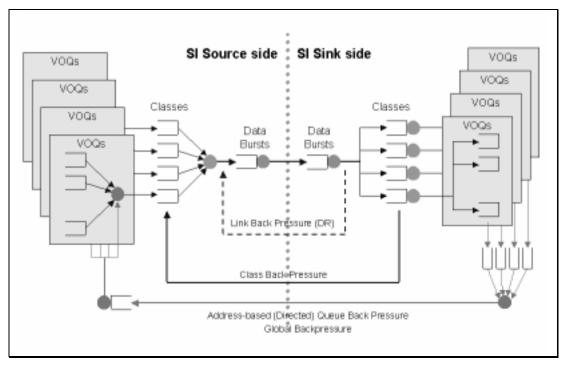

Figure 3, following, shows the NPSI at various points in an implementation.

## 5.4 Interface Signals

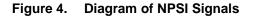

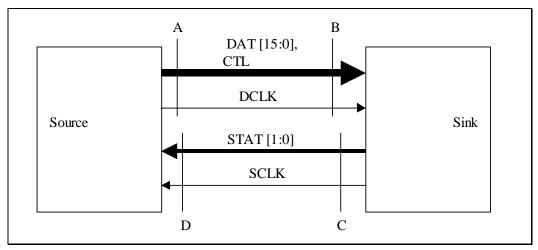

Figure 4 is a block diagram of the interface signals of an NPSI.

The data path includes clock, data, and control/framing (DCLK, DAT[15:0], and CTL).

The flow control status channel includes clock and flow control status (SCLK and STAT[1:0]<sup>7</sup>).

Note that the interface consists of a unidirectional data path, with an out-of-band flow control interface corresponding to (and in the opposite direction of) the data path. This allows for a device implementation that processes traffic in a single direction without the need for a companion device (in the opposite direction) for managing flow control information.

| SIGNAL    | Signal Name                                                                                                                              | DESCRIPTION                                                                                                                                                      |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DCLK      | Data Clock                                                                                                                               | Clock associated with data and control (DAT and CTL).                                                                                                            |  |

| DAT[15:0] | Data                                                                                                                                     | Data payload path with in-band control words for packet multiplexing and delineation.<br>These signals are driven off the rising and falling edges of DCLK.      |  |

| CTL       | Control CTL is high when a control word is present on DAT[15:0]. It is low otherwise is driven off the rising and falling edges of DCLK. |                                                                                                                                                                  |  |

| SCLK      | Status Clock                                                                                                                             | Clock associated with status (STAT).                                                                                                                             |  |

| STAT[1:0] | Status                                                                                                                                   | Status (flow control) information, along with associated framing and error control coding.<br>These signals are driven off the rising and falling edges of SCLK. |  |

Table 1. NPSI Signal Summary

<sup>&</sup>lt;sup>7</sup> This signal is optionally 4 bits in the NPE-Fabric Mode.

# 6. NPE-Framer Mode

The NPSI framer interface is the OI Forum SPI-4 Phase 2 interface specification [1]. The NPSI makes no changes to that specification.

# 7. Common Functions for the NPE-NPE and NPE-Fabric Mode

The NPE-NPE and NPE-Fabric modes of the NPSI (data path and status path) shall use the LVDS I/O electrical specifications in Section 10, "Physical Layer" for all interface signals.

# 7.1 Common Data Path Operation

The NPSI data path provides delineation of data on a packet basis and the ability to multiplex data from multiple packets on the data bus. Packets are delivered over the NPSI data bus in bursts of data that have a provisionable, constant length, with the exception of bursts that terminate with an EOP (End Of Packet); EOP bursts may be shorter. A data burst consists of one or more words of payload data, with a control sequence (as described below) immediately preceding it and following it. The control sequence differs for the various modes of operation. All data transfers include a payload section.

The data contained in the payload of a single data burst is called a segment. A packet is transferred as a sequence of one or more segments. Control words are inserted between segments. All segments of a packet, except the last segment (EOP), must be MAX\_SEGMENT\_SIZE (bytes)<sup>8</sup>. The last segment (EOP) may be shorter if the total packet length is not a multiple of MAX\_SEGMENT\_SIZE (bytes). Once a transfer has begun, the control sequence and data words of a segment are sent uninterrupted until the end of the packet or the MAX\_SEGMENT\_SIZE has been reached.

An NPSI device shall support one or more values of MAX\_SEGMENT\_SIZE that are integer multiples of 16 bytes. An NPSI device may also support one or more values of MAX\_SEGMENT\_SIZE of any size. If an NPSI device supports more than one value of MAX\_SEGMENT\_SIZE, it shall provide a mechanism to configure the value.

The transfer of data requires the use of control words and data words. Control words and data words are differentiated by the CTL signal (as described in Section 5.4, "Interface Signals").

There are four types of control words:

- Address Control Words (ACW),

- Payload Control Words (PCW),

- Idle Control Words (ICW), and

- Training Control Words (TCW).

Note that Training Control Words may only occur during a training sequence, and are never included in the control sequence of a data transfer.

There are three types of data words:

- Address Data Words (ADW),

- Payload Data Words (PDW), and

- Training Data Words (TDW).

Address Data Words may be included in a control sequence. Training Data Words may only occur during a training sequence.

<sup>&</sup>lt;sup>8</sup> Note that the framer interface, SPI-4 Phase 2, requires bursts (other than the EOP burst) to be multiples of 16 bytes and allows bursts of up to the maximum configured payload data transfer size, which is required to be a multiple of 16 bytes. In contrast to the SPI-4 Phase 2 specification, which permits non-EOP data bursts to be less than the maximum configured payload data transfer size, the NPSI requires all bursts (other than the EOP burst) to be segments of MAX\_SEGMENT\_SIZE in length (and MAX\_SEGMENT\_SIZE is an integer multiple of 16 bytes).

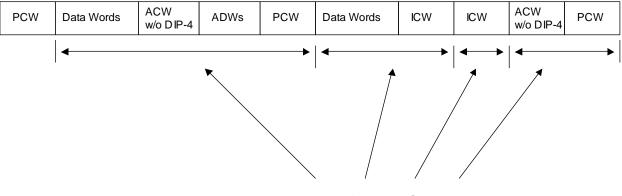

Data is always transferred with a control sequence occurring before and after each segment. A control sequence consists of zero or one ACW, followed by zero or more ADW's, followed by one PCW. An ACW or a PCW can indicate the start of a control sequence (and therefore the start of a transfer), depending on the interface mode. (Typically, an ACW starts the control sequence in NPE-Fabric mode and a PCW starts the control sequence in NPE-NPE mode.) Control words contain the SOP and EOP delineation of the packet.

A field in the control word immediately preceding the segment indicates if the segment is the SOP. The start of a packet (SOP) is always aligned to the beginning of a segment. Data from disparate packets do not share a segment.

A field in the control word immediately following the segment indicates if the segment was the end of the packet (EOP). The interval between the last payload word of a given transfer and the start of the next control sequence (marking the start of another transfer) consists of zero or more idle control words and zero or more training patterns (used for data path de-skew). The transfer of a segment may not be interrupted for any reason (e.g., insertion of idle words or training patterns).

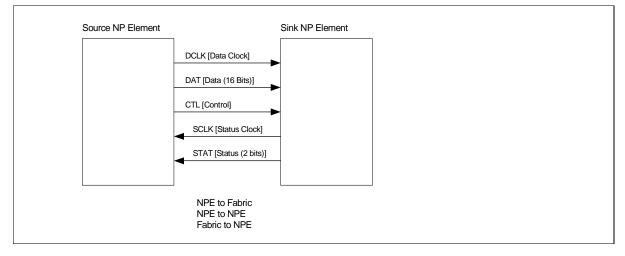

The following figure (Figure 5) is an example of how a single packet is broken into segments and sent across the NPSI.

### Figure 5. Example NPSI Data Path Segment Multiplexing

A control word carries the Start-of-Packet or End-of-Packet status. The last packet segment may need to be padded (by one byte) to the 2-byte (16-bit) width of the interface.

When inserted in the data path, a control word is aligned such that the MSB of the control word is sent on the MSB (bit 15) of the data lines. A control word or sequence of control words (control sequence) that separates two adjacent transfers may contain status information pertaining to the previous transfer, the following transfer, or both transfers.

During idle periods, when no data is being delivered, Idle Control words are sent.

Control words are described further in the following section.

#### 7.1.1 Data Framing Formats

This section describes the general operation of the NPSI data framing. In certain modes of operation, some framing formats or sequences may not apply.

The control sequence must contain a Payload Control Word (PCW). The control sequence may require an Address Control Word (ACW) and one or more Address Data Words (ADW). The required and optional formats are specific to the NPE-NPE Mode or NPE-Fabric Mode of operation, and are explained in Section 8, "NPE-Fabric Mode," and Section 9, "NPE-NPE Mode."

There are three possible data burst formats. Each has a defined control sequence:

- A Basic Data Burst control sequence contains a single Payload Control Word.

- An Extended Address Data Burst without ADW control sequence contains a single Address Control Word followed by a single Payload Control Word.

- An Extended Address Data Burst with ADW control sequence contains a single Address Control Word followed by one or more (up to eight) Address Data Words, followed by a single Payload Control Word.

A segment contains one or more Payload Data Words (PDW) and it must be preceded by one of the three valid control sequences, depending on the mode of operation.

The end of the transfer is indicated by a Control Word, which may be an Idle Control Word (ICW), a Payload Control Word (PCW), or an Address Control Word (ACW), and contains the end of packet (EOP) status. For back-to-back transfers (i.e., when no idle periods or training sequences need to be inserted between data transfers), a single Control Word (an ACW or PCW) terminates the previous transfer and initiates the next one. During idle periods, Idle Control Words are sent. During training, Training Control Words and Training Data Words are sent, with an Idle Control Word immediately preceding the training sequence.

Control Words contain the packet delineation information: Start Of Packet (SOP), and End Of Packet Status (EOPS). Control Words also may contain a 4-bit Diagonal Interleaved Parity (DIP-4) as the error control code.

The control sequence for the Basic data burst consists of one control word: PCW. The PCW contains the SOP, EOPS, and DIP-4<sup>9</sup>. The ACW and ADW are not used in this format. The Basic data burst is only allowed (and is the required format) in the NPE-NPE mode.

Control words and data words are differentiated by the CTL signal (as described in Section 5.4, "Interface Signals").

<sup>&</sup>lt;sup>9</sup> This is consistent with SPI-4 Phase 2 [1].

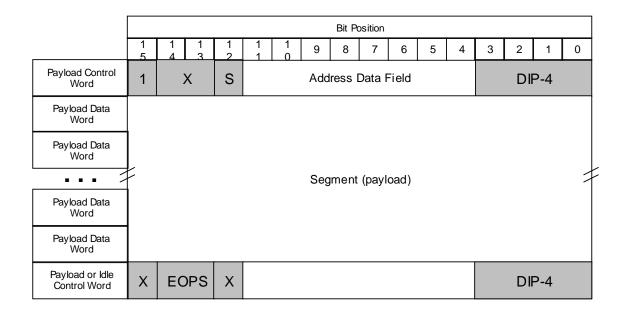

### Figure 6. Basic Data Burst

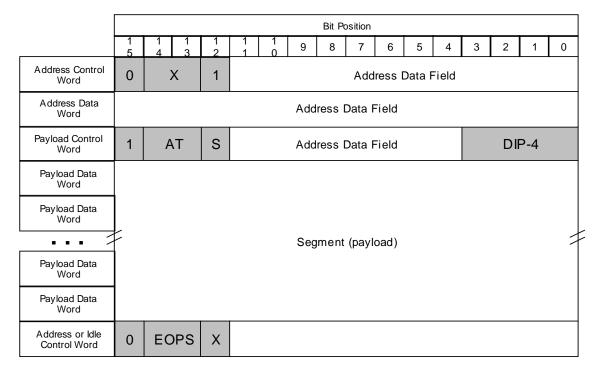

There are two forms of the Extended Address data burst: with or without the  $\text{ADW}^{10}$ .

The control sequence for the Extended Address data burst without ADW consists of two control words: ACW and PCW.

Figure 7. Extended Address Data Burst without ADW

|                                 |        | Bit Position |   |   |                                                                     |                    |      |       |      |       |                                                               |  |  |  |   |

|---------------------------------|--------|--------------|---|---|---------------------------------------------------------------------|--------------------|------|-------|------|-------|---------------------------------------------------------------|--|--|--|---|

|                                 | 1<br>5 | 1 1<br>4 3   | 1 | 1 | 1     1     9     8     7     6     5     4     3     2     1     0 |                    |      |       |      |       | 1         1         9         8         7         6         5 |  |  |  | 0 |

| Address Control<br>Word         | 0      | Х            | 1 |   | Address Data Field                                                  |                    |      |       |      |       |                                                               |  |  |  |   |

| Payload Control<br>Word         | 1      | 1 AT S       |   |   |                                                                     | Address Data Field |      |       |      | DIP-4 |                                                               |  |  |  |   |

| Payload Data<br>Word            |        |              |   |   |                                                                     |                    |      |       |      |       | -                                                             |  |  |  |   |

| Payload Data<br>Word            |        |              |   |   |                                                                     |                    |      |       |      |       |                                                               |  |  |  |   |

| ••• 7                           | F      |              |   |   |                                                                     | Seg                | ment | (payl | oad) |       |                                                               |  |  |  | 7 |

| Payload Data<br>Word            |        |              |   |   |                                                                     |                    |      |       |      |       |                                                               |  |  |  |   |

| Payload Data<br>Word            |        |              |   |   |                                                                     |                    |      |       |      |       |                                                               |  |  |  |   |

| Address or Idle<br>Control Word | 0      | EOPS         | X |   |                                                                     |                    |      |       |      |       |                                                               |  |  |  |   |

<sup>&</sup>lt;sup>10</sup> This is consistent with a mode of SPI-5 [2].

The control sequence for the Extended Address data burst with ADW consists of three (or more) control words: ACW and PCW, with up to eight ADWs in between.

#### Figure 8. Extended Address Data Burst with ADW

### 7.1.1.1 Control Word Field Definitions

Table 2 describes the fields used for ACW, PCW and ICW control words.

| CW Bits                      | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CW[15,12] CWT                |          | Control Word Type                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                              |          | The Control Word Type CWT[1:0] identifies the type of the Control Word.                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                              |          | CWT[1:0] = 0 0 : Idle Control Word (ICW)                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                              |          | CWT[1:0] = 0 1 : Address Control Word (ACW)                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                              |          | CWT[1:0] = 1 0 : Payload Control Word (PCW) and not Start-of-Packet (SOP)                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                              |          | CWT[1:0] = 1 1 : Payload Control Word (PCW) and Start-of-Packet (SOP)                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                              |          | CWT[1] is mapped to CW[15] while CWT[0] is mapped to CW[12]                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| CW[14:13]                    | EOPS/AT  | End-of-Packet Status, or Address Type (in PCW, NPE-Fabric Mode only)                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                              |          | The End-of-Packet Status Field EOPS[1:0] is present in Idle Control Words or<br>Address Control Words (or in Payload Control Words in the Basic Data Burst<br>format only) and reports the status of the payload transfer immediately<br>preceding it. EOPS[1:0] is only valid in the first Control Word (ACW, ICW, or<br>PCW) immediately following a PDW burst. |  |  |  |  |

|                              |          | EOPS[1:0] = 0 0 : Not EOP<br>EOPS[1:0] = 0 1 : EOP with abnormal cell/packet termination (Abort)                                                                                                                                                                                                                                                                  |  |  |  |  |

|                              |          | EOPS[1:0] = 1 0 : EOP with normal cell/packet termination, 2 bytes valid                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                              |          | EOPS[1:0] = 1 1 : EOP with normal cell/packet termination, 1 byte valid                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                              |          | EOPS[1:0] is mapped to CW[14:13].                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                              |          | The AT values are defined in Table 6, "Address Type Encoding for the NPE-<br>Fabric Mode."                                                                                                                                                                                                                                                                        |  |  |  |  |

| CW[11:4] (in ICW or          | ADF      | Address Data Field                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PCW) or<br>CW[11:0] (in ACW) |          | The Address Data Field contains addressing information related to the data<br>burst in PCW and ACW.                                                                                                                                                                                                                                                               |  |  |  |  |

|                              |          | ADF is all zeroes for ICW.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| CW[3:0]                      | DIP4     | 4-bit Diagonal Interleaved Parity                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| (in ICW or PCW)              |          | The 4-bit Diagonal Interleaved Parity (DIP4[3:0]) provides error control coding<br>over the current Control Word and the preceding Data Words (and possibly<br>Control Words). Odd parity is calculated diagonally over the covered words.                                                                                                                        |  |  |  |  |

Table 2.

Control Word Field Definitions

Training Control Words (in conjunction with Training Data Words) are used for data path de-skew. Their format and usage are described in Section 7.1.5, "Training Sequence for Data Path De-skew."

#### 7.1.1.2 Data Word Field Definitions

Control words and data words are differentiated by the CTL signal (as described in Section 5.4, "Interface Signals").

Table 3 describes the fields used in ADW and PDW data words .

| DW Bits  | Mnemonic | Description                                                                     |

|----------|----------|---------------------------------------------------------------------------------|

| DW[15:0] | ADW      | Address Data Word                                                               |

|          |          | The Address Data Word contains 16 bits of address information.                  |

|          |          | An ADW shall only appear according to the Extended Address Data Burst with ADW. |

| DW[15:0] | PDW      | Payload Data Word                                                               |

|          |          | The Payload Data Word contains 16 bits of payload (segment) data.               |

Table 3. Data Word Field Definitions

Training Data Words (in conjunction with Training Control Words) are used for data path de-skew. Their format and usage are described in Section 7.1.5, "Training Sequence for Data Path De-skew."

### 7.1.2 Data Transfer Procedure

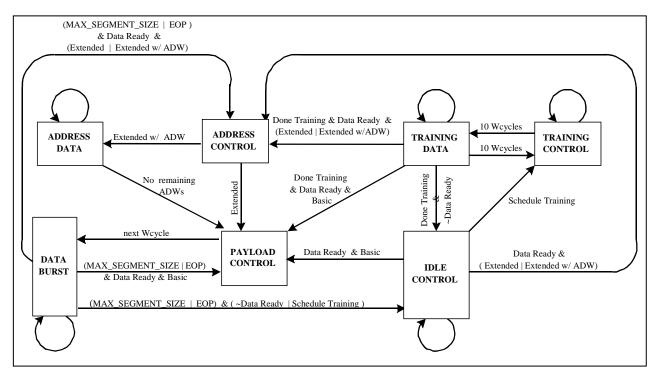

The proper sequence of Control and Data words on the data path constitutes a state machine. A state transition occurs for each 16-bit word cycle (Wcycle). Figure 9, below, shows the Wcycle-by-Wcycle

behavior of the data path state transitions. A transition is indicated by an arrow from one box to another.

For delivery of data over the NPSI, only states Idle Control, Address Control, Address Data, Payload Control, and Data Burst are involved. The remaining states, Training Control and Training Data, pertain to de-skew of the signals in the bus and will be described further in Section 7.1.5, "Training Sequence for Data Path ."Table 4 provides a description of the states.

| State            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle Control     | This state handles the case where no data needs to be sent over the bus. An Idle Control word is sent in the current Wcycle.                                                                                                                                                                                                                                                                                                                                                              |

| Address Control  | This state is entered at the beginning of each extended burst. An Address Control word is sent to deliver the first portion of a control sequence of addressing information. Additional addressing information may be sent in subsequent Address Data words and a Payload Control word.                                                                                                                                                                                                   |

| Address Data     | This state may be entered after the Address Control state to deliver the intermediate words of a control sequence. Transition into this state is only valid for Extended Address Data Bursts with ADW. Each Address Data word contains 2 bytes of the Address Data Field. Residence in this state is maintained until all but the final Payload Control word has been sent. The maximum duration in this state is 8 Wcycles. An Address Data word is sent for every Wcycle in this state. |

| Payload Control  | This state is entered at the beginning of each basic burst. It is also entered from the Address Control or Address Data state for extended bursts. A Payload Control word is sent in this state.                                                                                                                                                                                                                                                                                          |

| Data Burst       | The payload data (segment) of a data transfer is sent in this state. Residence is maintained until the first of the following two events occurs: MAX_SEGMENT_SIZE bytes have been sent or an end-of-packet is encountered. A Payload Data Word is sent for every Wcycle in this state.                                                                                                                                                                                                    |

| Training Control | This state provides the Control word portion of the de-skew training pattern. A Training Control word is sent for every Wcycle in this state. Training is described in detail in Section 7.1.5.                                                                                                                                                                                                                                                                                           |

| Training Data    | This state provides the Data word portion of the de-skew training pattern. A Training Data word is sent for every Wcycle in this state. Training is described in detail in Section 7.1.5.                                                                                                                                                                                                                                                                                                 |

Table 4.Data Path States

#### 7.1.3 Packet Delineation

EOP/SOP delineation applies to the multiplexing context in the Address Data Field (ADF), as explained in section 7.1.1.

No further multiplexing capability is defined in this specification.<sup>11</sup>

There is no minimum or maximum packet size assumed by this specification.

#### 7.1.4 Error Detection

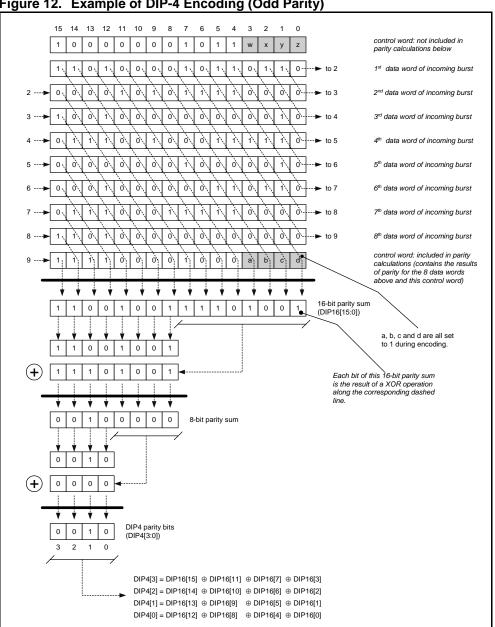

Error detection is provided using a 4-bit Diagonal Interleaved Parity (DIP-4)<sup>12</sup>. The Idle, Training, and Payload Control Words carry a DIP-4. The Address Control Word does not carry a DIP-4.

Unused bits in the ADF shall be transmitted as zero and included in the DIP-4 calculation. On reception, they shall be used only for the calculation of DIP-4 and otherwise ignored.

The range over which the DIP-4 parity bits are computed is from immediately after the last DIP-4 (in an ICW, PCW, or TCW) to the current control word (ICW, PCW, or TCW) containing the current DIP-4<sup>13</sup>. In the presence of random errors, DIP-4 offers the same error detection capability as a comparable BIP (Bit Interleaved Parity) code, but has an additional advantage of spreading single-column errors (as might occur in a single defective line) across the parity bits. Appendix A of the SPI-4 Phase 2 implementation agreement [1] discusses the error detection performance of this code.

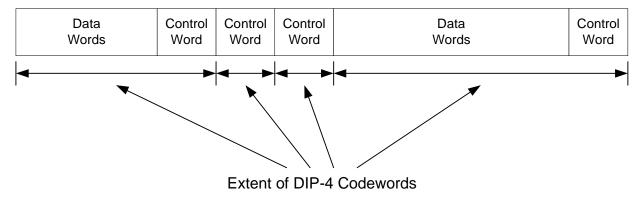

Figure 10 and Figure 11 show the range over which the DIP-4 parity bits are computed.

Figure 10. Extent of DIP-4 Coverage for Basic Addressing Mode

<sup>&</sup>lt;sup>11</sup> If an additional level of multiplexing (multiple packets within a given ADF) is required, an additional tag embedded in the payload must be used. This is outside the scope of this specification.

<sup>&</sup>lt;sup>12</sup> This is consistent with SPI-4 Phase 2 [1].

<sup>&</sup>lt;sup>13</sup> Note that the DIP-4 is also calculated and checked from ICW to ICW, but this is not covering any packet data. From PCW to PCW, the DIP-4 covers a segment of data plus the control sequence of the next segment. From PCW to ICW, the DIP-4 covers a segment of data plus the ICW. From ICW to PCW, the DIP-4 covers the control sequence of the next segment. The DIP-4 in the TCW covers only the TCW. Note that, in some cases, a single DIP-4 error may cause two segments to be considered to be in error.

#### Figure 11. Extent of DIP-4 Coverage for Extended Addressing Mode (ACW & ADW)

**Extent of DIP-4 Code Words**

A functional description of calculating the DIP-4 code is given as follows. Assume that the stream of 16-bit data words are arranged in a vertical stack, MSB at the leftmost column, time moving downward. (The first word received is at the top; the last word is at the bottom.) The parity bits are generated by summing diagonally. (In the control word, the space occupied by the DIP-4 code (bits a, b, c, d) is set to all 1's during encoding.) The first 16-bit checksum is split into two bytes, which are combined (bitwise XOR) to produce an 8-bit checksum. The 8-bit checksum is then divided into two 4-bit nibbles, which are combined (bitwise XOR) to produce the final DIP-4 code<sup>14</sup>. The procedure described applies to either parity generation on data transmission or to check parity on data reception.

Note that the control signal, CTL, is not included in the DIP-4 calculation. An example is shown in Figure 12.

<sup>&</sup>lt;sup>14</sup> This description is different from the description in the OIF SPI-4 Phase 2 and SPI-5 specifications ([1] and [2]) and is intended as a clarification. However, the process produces the same parity field values.

### Figure 12. Example of DIP-4 Encoding (Odd Parity)

### 7.1.5 Training Sequence for Data Path De-skew

A training sequence is scheduled to be sent at least once every pre-configured bounded interval (DATA MAX T) on the data path. These training sequences may be used by the receiving end of each interface for de-skewing bit arrival times on the data (and corresponding control) lines. The sequence defined in this section is designed to allow the receiving end to correct for relative skew differences of up to +/- 1 bit time. The training sequence consists of one idle control word followed by one or more repetitions of a 20-word training pattern consisting of 10 (repeated) training control words and 10 (repeated) training data words. The initial idle control word removes dependencies of the DIP-4 in the training control words from preceding data words. Assuming a maximum of +/- 1 bit time in bit alignment jitter on each line, and a maximum of +/- 1 bit time relative skew between lines, there will be at least 8 bit times during which a receiver can detect a training control word prior to de-skew. The training data word is chosen to be to the binary complement of the training control word.

| TW Bits  | Mnemonic | Description                                                                                                       |

|----------|----------|-------------------------------------------------------------------------------------------------------------------|

| TW[15:0] | TCW      | Training Control Word                                                                                             |

|          |          | The TCW pattern is 0x0FFF. Bits [3:0] of the TCW contain the DIP-4 of the control word (by design always 0b1111). |

| TW[15:0] | TDW      | Training Data Word                                                                                                |

|          |          | The TDW pattern is 0xF000.                                                                                        |

The sending (source) side of the data path must schedule the training sequence at least once every DATA\_MAX\_T interval, defined as DATA\_MAX\_T \* 2<sup>8</sup> clock cycles, and repeat the training pattern DATA\_ALPHA consecutive times, where DATA\_MAX\_T and DATA\_ALPHA are configurable on start-up. Once the training sequence is scheduled, the source shall wait until the completion of the current data burst to start the transmission of the training sequence. The subsequent training sequence shall be no later than the DATA\_MAX\_T interval from the scheduled time, not transmission time, of the training sequence. Training sequences must not be inserted within a data transfer (i.e., not inserted between the first control word of a control sequence and any of the subsequent control or data words until the end of transfer). Setting DATA\_MAX\_T equal to zero shall disable the periodic transmission of the trainsmitted. A transmitter shall support all values of DATA\_MAX\_T up to 2<sup>32</sup>-1 and shall provide a mechanism to configure the value. A transmitter shall support all values of DATA\_ALPHA up to 255 and shall provide a mechanism to configure the value.

Note that the error-free reception of all 10 of the Training Data Words always results in a DIP-4 code of '0xF' in a subsequent Idle Control Word. Likewise, if a Payload Control Word follows the training sequence, the DIP-4 result depends upon the content of the Payload Control Word. Also, if an Address Control Word (without a DIP-4 code) follows the training sequence, the DIP-4 result (in the Payload Control Word) depends upon the contents of the Address Control Word, any Address Data Words and the Payload Control Word.

## 7.2 Common Flow Control Path Operation

### 7.2.1 Flow Control Status Framing

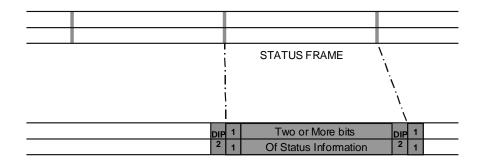

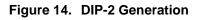

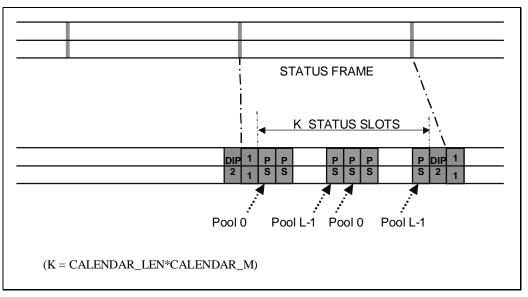

Flow control (downstream queue status) information is sent from the data path sink to the data path source over the Status bus in a framing structure called a status frame. Each status frame contains one framing code, two or more bits of flow control (status) information, and one 2-bit diagonal interleaved parity (DIP-2) code.

### Figure 13. Common Status Channel Format

The status frame is sent as follows: The framing code, '0b11', is sent, followed by the flow control (status) information, followed by a DIP-2 field. The status frame is then repeated, starting with the framing code. Three or more consecutive framing codes constitute a framing error. The DIP-2 field is an error check code that is computed diagonally over the contents of preceding status frame, not including the framing code, as shown below. The first 2-bit pair of the status frame immediately

following the framing code is at the top of the figure and the last 2-bit pair is at the bottom of the figure. The parity bits are computed by summing diagonally. Bits 'a' and 'b' in line 9 correspond to the space occupied by the DIP-2 parity bits, which are set to 1 during encoding. The procedure described applies to both parity generation and to parity checking functions.

Note that DIP-2 code and training patterns may both emulate the framing code ('0b11'). The framer state machine must not confuse these occurrences with frame boundaries.

The signal data rate of the status lines is the same as the signal data rate of the data lines. A 4-bit status bus is optional (for the NPE-Fabric Mode only).

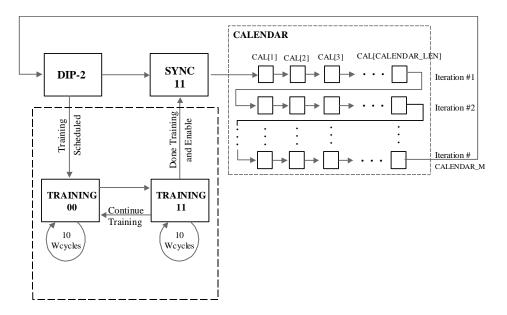

### 7.2.1.1 Training Sequence for Status Path De-skew

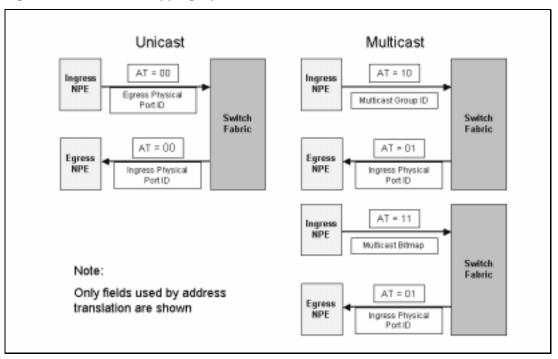

A Training Sequence is periodically inserted into the transmitted bit stream to allow the receiver to properly synchronize with the 2-bit (or 4-bit) signals of the status interface.

The training pattern consists of ten words of '0b00' followed by ten words of '0b11'. (The training sequence was chosen so that it can be distinguished from a valid status channel message.) The training pattern can optionally be extended by repeating the 20-cycle pattern STAT\_ALPHA times. The training sequence consists of the training pattern repeated STAT\_ALPHA times.

A training sequence is scheduled to be sent at least once every pre-configured bounded interval (STAT\_MAX\_T) on the status interface. Once the training sequence is scheduled, the source shall wait until the completion of the current status frame to start the transmission of the training sequence. The subsequent training sequence shall be no later than the STAT\_MAX\_T interval, defined as STAT\_MAX\_T \* 2<sup>8</sup> clock cycles, from the scheduled time, not transmission time, of the training sequence. Periodic status channel training can be disabled by setting the bus parameter STAT\_MAX\_T to '0'. The training sequence shall always be sent after reset and before normal operation begins. A transmitter shall support all values of STAT\_MAX\_T up to 2<sup>32</sup>-1 and shall provide a mechanism to configure the value. A transmitter shall support all values of STAT\_ALPHA up to 255 and shall provide a mechanism to configure the value.

These training sequences may be used by the receiving end of each interface for de-skewing bit arrival times on the status lines. The sequence defined in this section is designed to allow the receiving end to correct for relative skew differences of up to +/- 1 bit time.

The training sequence is inserted between two consecutive frames. Training sequences shall only be inserted between the DIP-2 checksum at the end of the preceding status frame and the '0b11' framing code of the following status frame.

#### 7.2.1.2 Training Sequence for the 4-bit Status Path De-skew

The same de-skewing pattern and procedure is used for the 4-bit wide mode as for the 2-bit wide mode, except that the pattern is duplicated on both halves of the status bus interface; the training pattern consists of ten words of '0b0000' followed by ten words of '0b1111'.

The training pattern shall be run across the full width of the status interface. If the previous frame did not end on a 4-bit boundary, the transmitter shall insert an all zeroes pattern after the DIP-2 code to ensure that the training sequence runs across the full width of the status interface.

## 7.3 Loss of Synchronization

### 7.3.1 Loss of Data Path Synchronization (LODS)

An NPE-NPE and NPE-Fabric data path sink shall continuously monitor the data path for proper synchronization and error free operation. If the reaction to LODS is enabled, the following mechanism of detecting and reacting to LODS is required.

When a data sink detects multiple consecutive errors on the data path, it shall report a Loss of Data Synchronization (LODS) condition. This alarm condition is reported by sending a LODS alarm pattern back to the data path source on the status channel. Although no specific number of data path errors is specified, it is a requirement that any single error event shall not cause loss of synchronization.

The LODS alarm status pattern shall be sent immediately when a LODS condition is detected, without regard to the current position in the status frame. The LODS pattern shall be repeated continuously until the data path has regained synchronization, having received sufficient training patterns.<sup>15</sup>

When a data path source detects a LODS alarm status pattern on its corresponding status bus, resulting in status out-of-frame state (as described below), the data path source shall cancel all previously granted credits (NPE-NPE mode) or set its internal DR state to de-asserted (NPE-Fabric mode). Credits are only refreshed (or the internal DR state set to asserted) after the status channel returns to the in-frame state (as described below). While the status frame receiver is in out-of-frame state, the data path transmitter shall send a training sequence on the data path. The data path transmitter shall send a training safter completion of a training sequence before sending a subsequent training sequence due to the LODS alarm (status out-of-frame state).

The LODS alarm status pattern consists of the training pattern (as described in Section 7.2.1.1) sent at least (STAT\_ALPHA+2) times. Receipt of no more than 12 repetitions of the LODS pattern shall be sufficient to force the status frame receiver to the out-of-frame state.

### 7.3.2 Loss of Status Path Synchronization (LOSS)

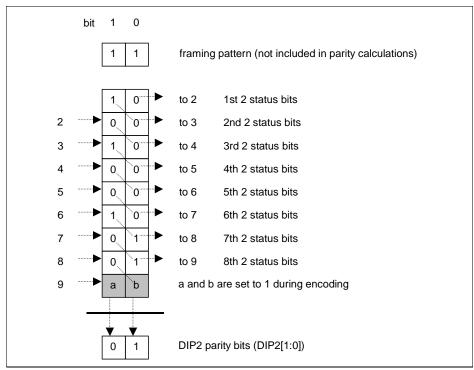

An NPE-NPE and NPE-Fabric status path sink shall continuously monitor the status path for proper synchronization and error free operation. If the reaction to Loss of Status Synchronization (LOSS) is enabled, the following mechanism of detecting and reacting to LOSS is required.