**Implementation Agreement for CFP2-**<u>Analogue</u> <u>Coherent</u> <u>Optics</u> Module

IA # OIF-CFP2-ACO-01.0

**January 22nd 2016**

Implementation Agreement created and approved by the Optical Internetworking Forum www.oiforum.com

IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

The OIF is an international non-profit organization with over 90 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements.

With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with IEEE 802.1, IEEE 802.3ba, IETF, IP-MPLS Forum, IPv6 Forum, ITU-T SG13, ITU-T SG15, MEF, ATIS-OPTXS, ATIS-TMOC, TMF and the XFP MSA Group.

For additional information contact: The Optical Internetworking Forum, 48377 Fremont Blvd., Suite 117, Fremont, CA 94538 510-492-4040, info@oiforum.com

www.oiforum.com

#### Working Group: Physical and Link Layer (PLL) Working Group

# TITLE: Implementation Agreement for a CFP2 Analogue Coherent Optics Module IA OIF-CFP2-ACO-01.0

#### SOURCE: TECHNICAL EDITOR

Ian Betty, Ph.D. Ciena 3500 Carling Ave Ottawa, ON K2H 8E9, Canada Phone: +1-613-670-2160 Email: <u>ibetty@ciena.com</u>

#### PLL WORKING GROUP CHAIR

David R. Stauffer, Ph.D. Kandou Bus, SA QI-I 1015 Lausanne, Switzerland Phone: +1.802.316.0808 Email: <u>david@kandou.com</u>

#### PLL WORKING GROUP - OPTICAL VICE CHAIR

Karl Gass Qorvo Phone: +1-505-301-1511 Email: <u>iamthedonutking@mac.com</u>

**ABSTRACT:** Implementation Agreement created and approved by the Optical Internetworking Forum for a CFP2 Analog Coherent Optics Module. The project start was approved at the Q2 Technical Meeting, April 2013 (Albuquerque, USA). OIF2013.130.01 is the original project start document for this project.

#### IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

#### © 2016 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

| OFFICAL<br>INTERNETWORKING<br>FORUM IA # OIF-CFP2-AC IA for CFP2 Analog Coherent Optics M                                                                                                                                                    | lodule               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LIST OF FIGURES                                                                                                                                                                                                                              | 8                    |

| LIST OF TABLES                                                                                                                                                                                                                               | 8                    |

| <ol> <li>Document Revision History</li> <li>Reference Documents</li> <li>2.1 Normative References</li> <li>3 Introduction</li> <li>4 CFP2-ACO Module Functions</li> <li>4.1 Transmit (Tx) Coherent Optics Function Block Diagrams</li> </ol> | 10<br>10<br>11<br>12 |

| 4.2 Receive (Rx) Coherent Optics Function Block Diagrams                                                                                                                                                                                     | 15                   |

| 4.3 Laser Sources (Tx and Rx LO)                                                                                                                                                                                                             | 17                   |

| 4.4 Integrated Polarization Multiplexed Quadrature Mach-Zehnder<br>Modulator (PMQ Modulator)                                                                                                                                                 | 18                   |

| 4.5 Intradyne Coherent Receiver (ICR)                                                                                                                                                                                                        |                      |

| 4.6 MZ Modulator RF Drivers                                                                                                                                                                                                                  | 19                   |

| 4.7 Optical Power Monitoring and Control                                                                                                                                                                                                     |                      |

| <ul><li>4.8 MDIO Management Interface Specification</li><li>4.9 Electronics</li></ul>                                                                                                                                                        |                      |

| 5 CFP2-ACO Module Classification by Electrical Interface                                                                                                                                                                                     |                      |

| 6 CFP2-ACO Module Mechanicals and Power                                                                                                                                                                                                      |                      |

| 6.1 Overview                                                                                                                                                                                                                                 |                      |

| 6.2 Mechanical Dimensions                                                                                                                                                                                                                    |                      |

| 6.3 Optical Connector                                                                                                                                                                                                                        |                      |

| <ul><li>6.4 Module Power Dissipation Classes</li><li>6.5 Module Bail Latch Color</li></ul>                                                                                                                                                   |                      |

| 7 CFP2-ACO Module Thermal Interface Requirements                                                                                                                                                                                             |                      |

| 7.1 Data Requirements                                                                                                                                                                                                                        |                      |

| 7.2 Thermal Environment                                                                                                                                                                                                                      | 24                   |

| 7.3 Thermal Interface Area                                                                                                                                                                                                                   |                      |

| 7.4 Module Thermal Interface Surface Requirements                                                                                                                                                                                            |                      |

| <ul> <li>7.5 Thermal Sensor Calibration</li> <li>8 CFP2-ACO Electrical Connector Interface</li> </ul>                                                                                                                                        |                      |

| 8.1 104-Pin Electrical Connector                                                                                                                                                                                                             |                      |

| 8.1.1 Background                                                                                                                                                                                                                             |                      |

| 8.1.2 Photographs of Connector: Plug and Host                                                                                                                                                                                                | 26                   |

| 8.1.3 Suppliers and Example Part Numbers                                                                                                                                                                                                     |                      |

| 8.1.4 Reliability and Environmental Test Documentation                                                                                                                                                                                       |                      |

| 8.1.5 Connector Ratings                                                                                                                                                                                                                      |                      |

| 8.1.6 RF Path S-Parameters                                                                                                                                                                                                                   |                      |

| 8.1.7 Connector Cross Mating                                                                                                                                                                                                                 | 27                   |

| 8.1.8 Related CFP2 Cage Products                                                                                                                                                                                                             |                      |

| 8.2 Electrical Pin Maps                                                                                                                                                                                                                      |                      |

| 8.2.1 Class 1 and Class 2 Electrical Pin Map                                                                                                                                                                                                 |                      |

| 8.2.2 Class 3 Electrical Pin Map with the Full Superset Analog Control |

|------------------------------------------------------------------------|

| Interface (ACI)                                                        |

| 8.3 Allowed Tx and Rx RF Channel Mappings                              |

| 9 CFP2-ACO Tx and Rx RF Electrical Interfaces                          |

| 9.1 Introduction                                                       |

| 9.2 Tx and Rx Electrical Interface Specification Compliance Points33   |

| 9.3 Compliance Board Suppliers and Example Part Numbers                |

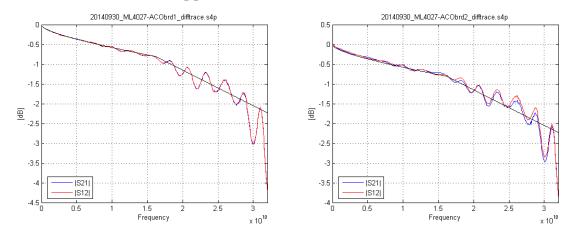

| 9.4 Compliance Board S Parameter Requirements                          |

| 9.5 Class 1: RF Electrical Interface Specifications                    |

| 9.5.1 Class 1: Tx RF Interface Specifications                          |

| 9.5.2 Class 1: Rx RF Interface Specifications                          |

| 9.6 Class 2/3: RF Electrical Interface Specifications                  |

| 9.6.1 Class 2/3: Tx RF Interface Specifications                        |

| 9.6.2 Class 2/3: Rx RF Interface Electrical Specifications40           |

| 10 Class 3 Analogue Control Interface (ACI) Requirements               |

| 10.1 Tx MZ Arm Phase Control Dither Inputs44                           |

| 10.2 Tx X-Pol. and Y-Pol. Power Control Dither Inputs45                |

| 10.3 Tx Optical Power Monitor Taps                                     |

| 10.4 Rx TIA/VGA Gain Control Inputs                                    |

| 10.5 PM_SYNC Input                                                     |

| 10.6 TX_DIS Input and RX_LOS Output Configurability                    |

| 11 MDIO Register Interface                                             |

| <ul><li>11.1 Implementation Overview</li></ul>                         |

| 11.3 CFP2-ACO User Private Use Registers                               |

| 12 OIF Requested CFP MSA MIS V2.4 R06b Extensions and Modifications    |

| Supporting the CFP2-ACO Module ( <i>Informative</i> )                  |

| 12.1 OIF Requested Changes to Existing CFP MSA MIS V2.4 R06b           |

| Content                                                                |

| 12.2 New MDIO Registers for Tx Subsystem Control                       |

| 12.3 New MDIO Registers for Rx Subsystem Control                       |

| 12.4 CFP2-ACO Fault, Alarm, Warning and Status (FAWS) Registers67      |

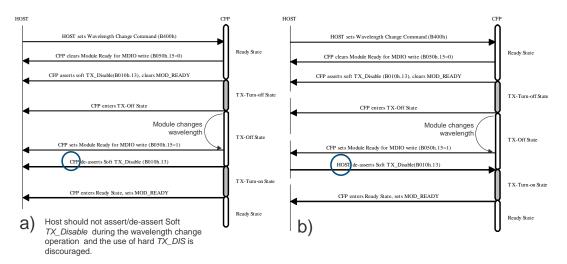

| 12.5 CFP2-ACO Wavelength Change Operation                              |

| 12.6 CFP2-ACO Wavelength Selection Registers                           |

| 12.6.1 Use of the High Resolution Tuning Registers                     |

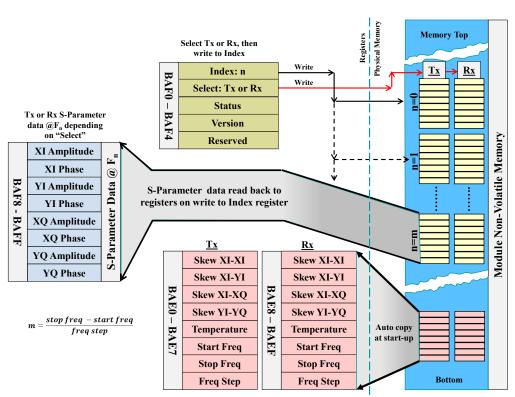

| 12.7 CFP2-ACO Module Characteristic Data Registers                     |

| 13 Relevant 0xB000 MDIO Registers in CFP MSA MIS V2.4 R06b             |

| (Informative)                                                          |

| <ul> <li>13.1 Tx and Rx Laser Source Control</li></ul>                 |

| <ul> <li>13.2 Tx and Rx Laser Source Performance Monitoring</li></ul>  |

| 13.4 Tx Output Power and Monitoring (VOA Control)                      |

| 13.5 Modulator Bias Voltages                                           |

| 13.6 FAWS Registers                                                    |

|                                                                        |

| 14 | Glossary                                                        | 85  |

|----|-----------------------------------------------------------------|-----|

|    | Annex A: HCB and MCB Differential Insertion Losses              |     |

| 16 | Annex B: Mated HCB and MCB S-Parameters                         | .87 |

| 17 | Appendix I: Electrical Connector S-Parameters (Informative)     | .90 |

| 18 | Appendix II: Beat Frequency Skew Measurement Method (Informativ | e)  |

|    | 91                                                              |     |

- 19

- 20

# List of Figures

| FIGURE 1: CFP2-ACO MODULE ILLUSTRATION <sup>1</sup>                                                        | 12  |

|------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 2 CFP2-ACO MODULE HIGH LEVEL BLOCK DIAGRAM                                                          | 13  |

| FIGURE 3: SUPERSET TRANSMIT FUNCTION BLOCK DIAGRAM WITH AN MDIO ONLY CONTROL INTERFACE                     | 14  |

| FIGURE 4: SUPERSET TRANSMIT FUNCTION BLOCK DIAGRAM WITH AN MDIO PLUS FULL SUPERSET ANALOG CONTROL          |     |

| INTERFACE (ACI)                                                                                            | 15  |

| FIGURE 5: SUPERSET RECEIVE FUNCTION BLOCK DIAGRAM WITH AN MDIO ONLY CONTROL INTERFACE                      | 16  |

| FIGURE 6: SUPERSET RECEIVE FUNCTION BLOCK DIAGRAM WITH AN MDIO PLUS FULL SUPERSET ANALOG CONTROL INTERF    | ACE |

| (ACI)                                                                                                      | 17  |

| FIGURE 7: CFP2-ACO ALLOWED CONNECTOR POSITIONS (CENTERED, LEFT JUSTIFIED, AND RIGHT JUSTIFIED) WITH        |     |

| DIMENSIONAL TOLERANCES                                                                                     | 23  |

| FIGURE 8 : (A) PLUG BOTTOM SIDE SHOWING SEQUENCED CONNECTION CONTACTS, (B) PLUG TOP SIDE SHOWING GSSG      |     |

| FORMAT RF CONTACT GROUPS, (C) HOST CONNECTOR REAR VIEW – PINS CONNECTED TO HOST PCBS, (D) HOST             |     |

| CONNECTOR FRONT VIEW – ACCEPTS THE PLUG                                                                    |     |

| FIGURE 9: SINGLE CFP2 CAGE ILLUSTRATION (INFORMATIVE).                                                     |     |

| FIGURE 10 (A) CLASS 1 AND 2 ELECTRICAL PIN MAP, (B) CLASS 3 FULL SUPERSET ACI INTERFACE ELECTRICAL PIN MAP |     |

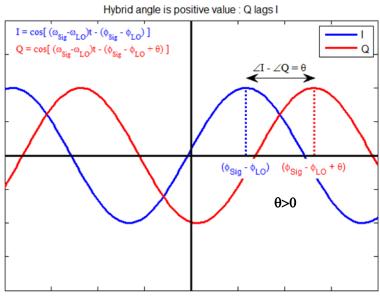

| FIGURE 11: I AND Q PHASE DEFINITIONS                                                                       |     |

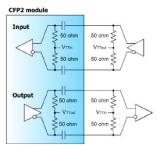

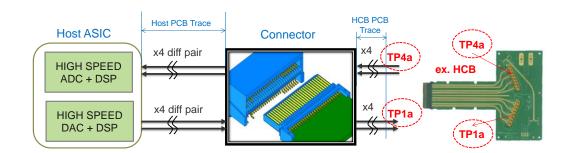

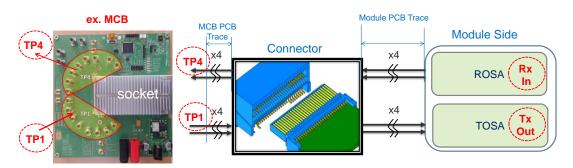

| FIGURE 12: HIGH-SPEED I/O FOR DATA                                                                         | 32  |

| FIGURE 13: INFORMATIVE RF CHANNEL IMPLEMENTATION EXAMPLE                                                   | 33  |

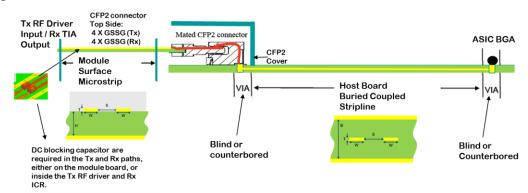

| FIGURE 14: TX AND RX ELECTRICAL INTERFACE COMPLIANCE POINTS. THE PROVIDED HCB AND MCB IMPLEMENTATION       |     |

| Pictures are <i>Informative</i> Examples Only.                                                             |     |

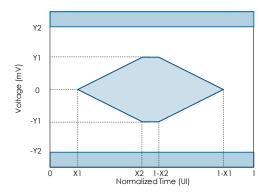

| FIGURE 15: CLASS 1 TX RF INTERFACE DRIVE SIGNAL EYE-MASK @ TP1A                                            |     |

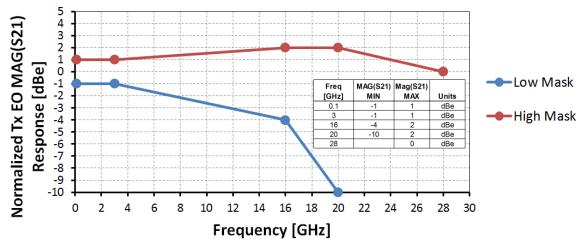

| FIGURE 16: NORMALIZED TX EO MAG(S21) COMPLIANCE MASK                                                       | 40  |

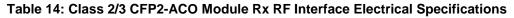

| FIGURE 17: NORMALIZED RX OE CG MAG(S21) COMPLIANCE MASK                                                    |     |

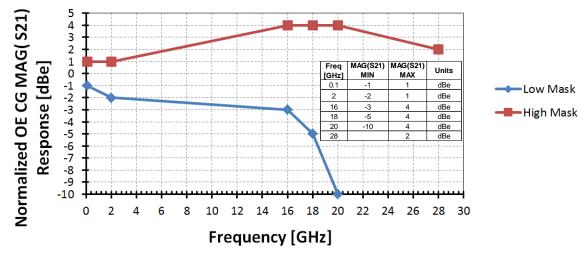

| FIGURE 18: TX ANALOG CONTROL INTERFACE (ACI) SCHEMATIC                                                     |     |

| FIGURE 19: RX ANALOG CONTROL INTERFACE (ACI) SCHEMATIC                                                     |     |

| FIGURE 20: WAVELENGTH CHANGE SEQUENCE (A) CLASS 1 AND 2, (B) CLASS 3.                                      |     |

| FIGURE 21: ACCESS METHODOLOGY TO OBTAIN CLASS 2 AND CLASS 3 MODULE CHARACTERISTIC DATA                     | 75  |

| FIGURE 22: REFERENCE DIFFERENTIAL INSERTION LOSSES FOR THE PCB TRACES ON TWO MODULE COMPLIANCE BOARDS      |     |

| [MCB SDD21]                                                                                                | 86  |

| FIGURE 23: REFERENCE DIFFERENTIAL INSERTION LOSSES FOR THE PCB TRACES ON A HOST COMPLIANCE BOARD [HCB      |     |

| SDD21]                                                                                                     |     |

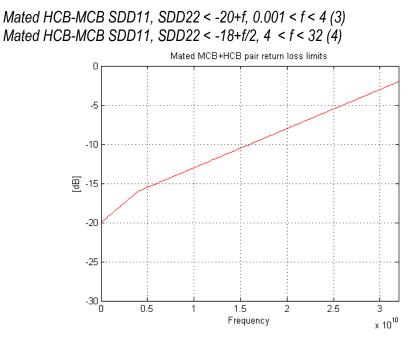

| FIGURE 24: MATED HCB-MCB SDD11, SDD22                                                                      |     |

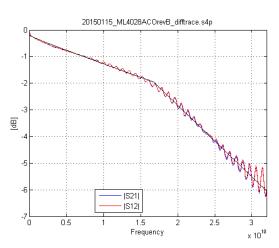

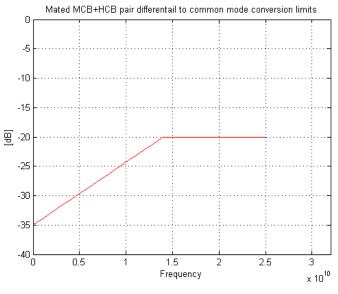

| FIGURE 25: MATED HCB-MCB SCD21, SCD12                                                                      |     |

| FIGURE 26: MATED HCB-MCB SCD11, SCD22 AND SDC11, SDC22                                                     |     |

| FIGURE 27: MATED HCB-MCB SDD21, SDD12                                                                      |     |

| FIGURE 28: MATED CFP2 CONNECTOR SI PERFORMANCE MEASUREMENT CONDITIONS                                      |     |

| FIGURE 29: TYPICAL MATED CFP2 CONNECTOR SI PERFORMANCE                                                     |     |

| FIGURE 30: BEAT FREQUENCY SKEW MEASUREMENT METHOD                                                          | 91  |

# List of Tables

| 9  |

|----|

| 21 |

| 22 |

| 26 |

| 27 |

| 27 |

| 28 |

| 31 |

| 34 |

|    |

#### IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

| TABLE 10: CLASS 1 CFP2-ACO MODULE TX RF INTERFACE ELECTRICAL SPECIFICATIONS                          |         |

|------------------------------------------------------------------------------------------------------|---------|

| TABLE 11: CLASS 1 CFP2-ACO MODULE RX RF INTERFACE ELECTRICAL SPECIFICATIONS                          |         |

| TABLE 12: CLASS 2/3 CFP2-ACO MODULE TX RF INTERFACE ELECTRICAL SPECIFICATIONS FOR A MODULE CONTROL   | led PMQ |

| TRANSMITTER                                                                                          |         |

| TABLE 13: CLASS 3 CFP2-ACO MODULE TX RF INTERFACE ELECTRICAL SPECIFICATIONS FOR A HOST CONTROLLED PI | MQ      |

| TRANSMITTER                                                                                          | 40      |

| TABLE 14: CLASS 2/3 CFP2-ACO MODULE RX RF INTERFACE ELECTRICAL SPECIFICATIONS                        | 42      |

| TABLE 15 REQUESTED CHANGES TO CFP MSA MIS V2.4 R06B REGISTERS                                        | 51      |

| TABLE 16: TX SUBSYSTEM MDIO REGISTERS                                                                | 60      |

| TABLE 17: RX SUBSYSTEM MDIO REGISTERS                                                                | 65      |

| TABLE 18: RX SUBSYSTEM MDIO REGISTERS CONTINUED                                                      |         |

| TABLE 19: CFP MSA MIS V2.4 R06B LASER CONTROL REGISTERS                                              |         |

| Table 20: Tx Minimum Laser Frequency Registers                                                       |         |

| TABLE 21: TX TUNED LASER FREQUENCY REGISTERS                                                         |         |

| Table 22: Rx Minimum Laser Frequency Registers                                                       | 72      |

| TABLE 23: RX TUNED LASER FREQUENCY REGISTERS                                                         | 72      |

| TABLE 24: MDIO MODULE CHARACTERISTIC DATA REGISTERS                                                  | 75      |

| TABLE 25: GLOSSARY                                                                                   | 85      |

|                                                                                                      |         |

# 1 **Document Revision History**

Table 1 provides the OIF-CFP2-ACO-1.0 IA document revision history.

| Document          | Date                             | Revisions/Comments                                        |  |

|-------------------|----------------------------------|-----------------------------------------------------------|--|

| OIF2013.130.01    | April 19 <sup>th</sup><br>2013   | Project Start: CFP2 Coherent Optics Transceiver<br>Module |  |

| OIF-CFP2-ACO-01.0 | January<br>22 <sup>nd</sup> 2016 | Release created from OIF2014.006.19                       |  |

**Table 1: IA Document Revision History**

# 2 **Reference Documents**

#### 2.1 Normative References

[1] <u>www.cfp-msa.org</u>

[2] CFP MSA Management Interface Specification, Version 2.4 R06b (June 8<sup>th</sup> 2015)

[3] CFP MSA CFP2 Hardware Specification Revision 1.0, 31 July 2013

[4] CFP MSA CFP/CFP2/CFP4 Pin Allocation Rev. 25

[5] OIF-MSA-100GLH-EM-01.1 - Multisource Agreement for 100G Long-Haul DWDM Transmission Module - Electromechanical (September 2011)

[6] OIF-PMQ-TX-01.2 - Implementation Agreement for Integrated Polarization Multiplexed Quadrature Modulated Transmitters (May 2015)

[7] OIF-DPC-RX-01.2 - Implementation Agreement for Integrated Dual Polarization Intradyne Coherent Receivers (November 2013)

[8] OIF-microITLA-01.1 – Implementation Agreement for Micro Integrable Tunable Laser Assembly (July 2015)

[9] OIF-ITLA-MSA-01.3 - Integrable Tunable Laser Assembly Multi Source Agreement (July 2015)

[10] OIF-CEI-03.1 - Common Electrical I/O (CEI) - Electrical and Jitter Interoperability agreements for 6G+ bps, 11G+ bps, 25G+ bps I/O (February 2014)

[11] CFP2 Hardware Baseline Design Rev. 1L

[12] Implementation Agreement for Thermal Interface Specification for Pluggable Optics Modules (May 2015)

[13] OIF-DPC-MRX-01.0 - Implementation Agreement for Integrated Dual Polarization Micro-Intradyne Coherent Receivers (March 2015)

[14] Telcordia NEBS<sup>TM</sup> Requirements: Physical Protection, Telcordia Technologies Generic Requirements, GR-63-CORE Issue 3, March 2006.

# 3 Introduction

Faceplate density of optical IO is a key metric for switching and line-side transport applications. The industry experience is that this faceplate density is maximized when high power electronics are removed from optical modules [e.g. CFP  $\rightarrow$  CFP2  $\rightarrow$  CFP4 for 100GbE client modules.]

Faceplate density improvements can be realized for line-side optical transport by placing coherent DSP engines on the Host board and the E-to-O conversion functions within a CFP2 <u>A</u>nalog <u>C</u>oherent <u>O</u>ptics (CFP2-ACO) module. This architecture for line cards, that broadly separates optical and electronic DSP functions, offers the following additional benefits:

- Margin stacking of the coherent DSP engine in the supply chain is removed.

- Coherent DSP engine development is decoupled from the electro-optics development, which is beneficial since they have different supply chains and development cadences. This decoupling also enables specialization within the supply chain and reduces duplication of development efforts.

- Optimal cooling of the optical and electronic DSP functions is possible, enabling higher performance line-side applications. Shared heat sinking between low temperature optics and high temperature electronics is avoided and there is no inefficient "box"-in-"box" thermal stacking:

- A Host board coherent DSP engine can have a permanently attached full slot height heat sink with excellent thermal interface conductivity. The DSP engine can operate with high junction temperatures.

- A faceplate pluggable module has limited space available for a riding heat sink and the interface thermal conductivity is limited by both the maximum spring force that can be applied to the module and the module surface roughness. A pluggable module is best suited to relatively low power E-to-O conversion functionality.

- The dominant coherent modem Bill of Material (BOM) cost along with the main contributors to reliability FITs (Failures in Time) become hot-pluggable within the CFP2-ACO module. This addresses the problem of the modem first-in install cost in multi-port line cards. It also allows the selection of the best-fit CFP2-ACO module for each system application at the time of deployment (price/performance/power/etc.)

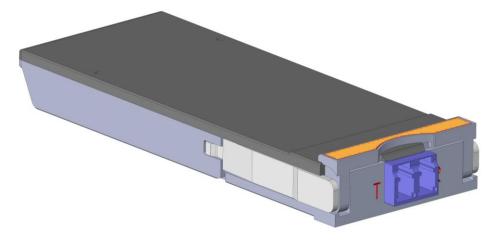

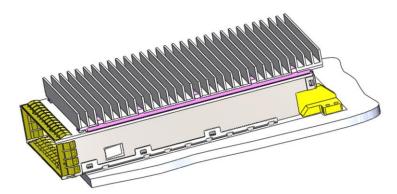

Figure 1 shows a CFP2-ACO module for illustration purposes only<sup>1</sup>. The CFP2-ACO module contains all the required functions to perform bi-directional

<sup>&</sup>lt;sup>1</sup> Do not use Figure 1 for design detail or scale.

dual polarization coherent optical signaling over a pair of single mode optical fibers and its definition is the topic of this implementation agreement.

Figure 1: CFP2-ACO Module Illustration<sup>1</sup>

Data rate agnostic CFP2 Analog Coherent Optics (CFP2-ACO) modules will be defined sufficiently in this IA to enable their use for *Metro-to-Regional* reach line-side transport applications and to allow them to interwork with multiple Host coherent DSP engine implementations. These modules are also expected to be used across *multiple* coherent DSP ASIC generations. The CFP2-ACO module is *not* a Metro-only reach transport solution. Different Classes of CFP2-ACO modules are defined in Section 5.

The CFP2-ACO provides a sufficient level of functional abstraction, within a "large enough" electromechanical envelope, to enable multiple optical technology choices to deliver competitive modules compatible with this IA. In addition, the CFP2 form factor provides a good physical match between optical and CMOS integration capabilities for coherent applications enabling the maximum practical medium term faceplate density for coherent optical transport.

The broad application space available to the CFP2-ACO provides a large enough addressable market for the optical module vendors to amortize significant investments in the development of the module. A long life-span for the CFP2-ACO solution is expected to provide the necessary runway and unit volumes required to spur significant innovation and cost reduction in the coherent optics solutions for *Metro-to-Regional* reach line-side transport.

### 4 **CFP2-ACO Module Functions**

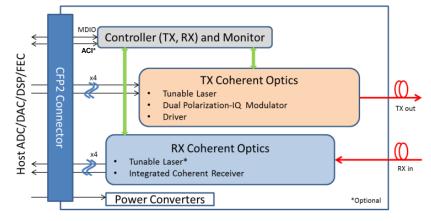

In this Section an overview is provided on the functions contained within the CFP2-ACO module to provide E-to-O and O-to-E conversions for dual

polarization (DP) coherent optical signaling. The high level block diagram for the CFP2-ACO module is given in Figure 2.

Figure 2 CFP2-ACO Module High Level Block Diagram

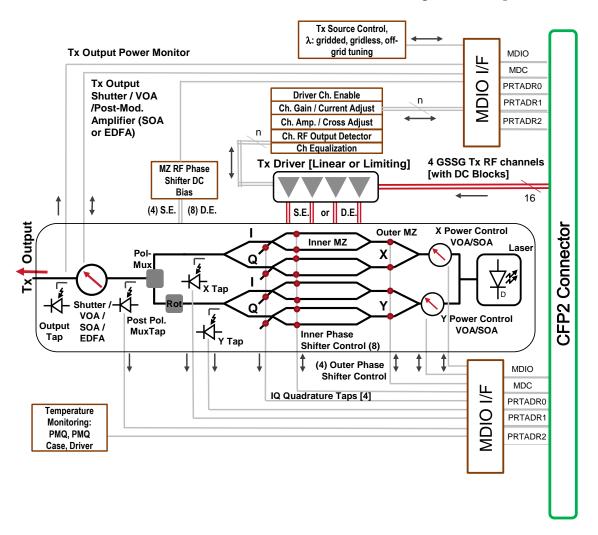

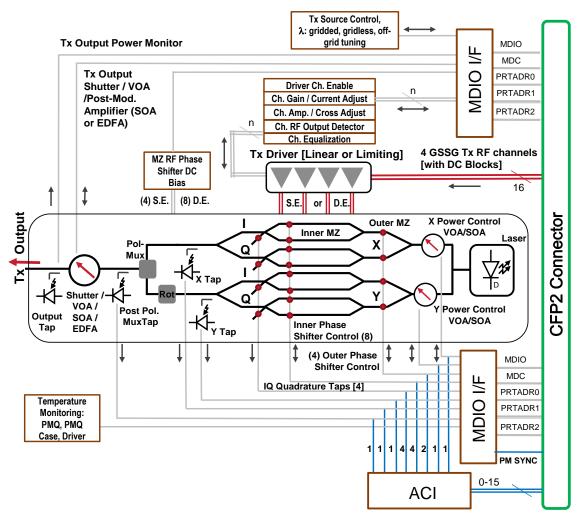

#### 4.1 Transmit (Tx) Coherent Optics Function Block Diagrams

The CFP2-ACO transmit function block diagram for an "MDIO<sup>2</sup> only" control interface is shown in Figure 3. The CFP2-ACO transmit function block diagram for an "MDIO plus Analog Control Interface (ACI)" is shown in Figure 4. In both Figures the Tx superset module functionality available on the MDIO control interface is shown. Not all this Tx functionality is required for an IA compatible module. The **BB01** *Tx Optical Features* register, the **BB02** *Tx Analog Control Interface Availability* register and the **BB04** *Tx Driver Features* register provide the user feedback on the functionality available within a given module vendor's implementation.

<sup>&</sup>lt;sup>2</sup> Management Data Input/Output

#### IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

Figure 3: Superset Transmit Function Block Diagram with an MDIO Only Control Interface

Figure 4: Superset Transmit Function Block Diagram with an MDIO plus Full Superset Analog Control Interface (ACI)

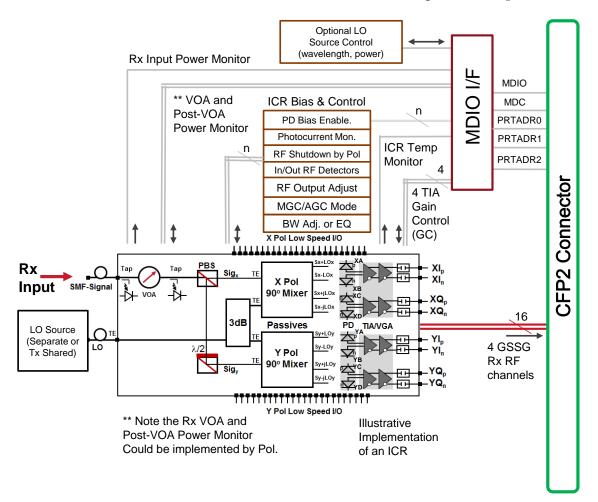

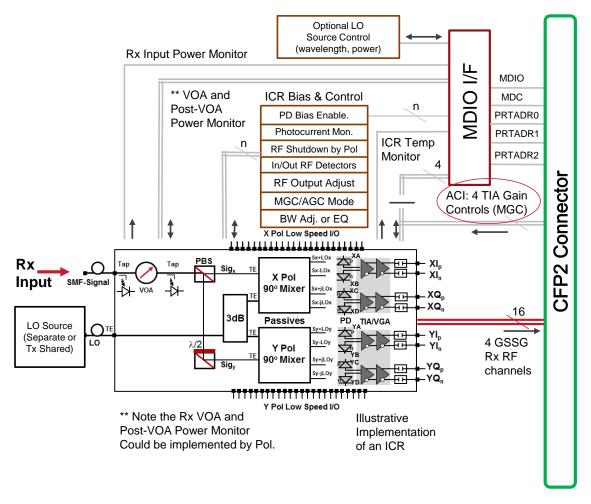

#### 4.2 Receive (Rx) Coherent Optics Function Block Diagrams

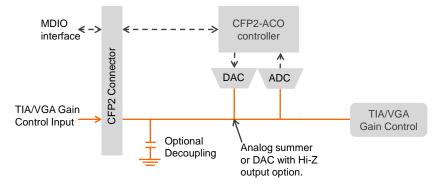

The CFP2-ACO receive function block diagram for an MDIO only control interface is shown in Figure 5. The CFP2-ACO receive function block diagram for an MDIO plus Analog Control Interface (ACI) is shown in Figure 6. In both Figures the Rx superset module functionality available on the MDIO control interface is shown. Not all this Rx functionality is required for an IA compatible module. The **BB8B** *Rx Subsystem Features* register and the **BB8C** *Rx TIA/VGA Features* register provide the user feedback on the functionality available within a given module vendor's implementation.

#### IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

Figure 5: Superset Receive Function Block Diagram with an MDIO Only Control Interface

Figure 6: Superset Receive Function Block Diagram with an MDIO plus Full Superset Analog Control Interface (ACI)

#### 4.3 Laser Sources (Tx and Rx LO)

The CFP2-ACO module may contain a single laser source whose optical power is shared between the transmit signal and LO functions, or it may contain two laser sources. The laser source(s) may be integrated with other electro-optics such as the ICR or the PMQ modulator, or be stand-alone components derived from the Ref. [8] µITLA. The number of laser sources in the module will depend on the technology available to the manufacturer along with design trade-offs such as CFP2-ACO module power dissipation or the physical space available.

The laser source(s) will require a narrow optical linewidth that is consistent with operation of coherent optical systems. Lorentzian components of the Tx and LO sources are expected to be below 500 kHz linewidth.

The channelization of the Tx and LO sources is expected to vary by application, with the most demanding applications requiring compatibility with arbitrary wavelength channel grids having a 6.25 GHz channel spacing.

To enable these applications in Section 12.1, the OIF is requesting registers to implement arbitrary settable Tx/Rx first channel frequencies with a 1 MHz resolution from the CFP2-MSA. The **B430** and **B440** *Fine Tune Frequency* registers are also required in the CFP2-ACO (they are not optional.)

# 4.4 Integrated Polarization Multiplexed Quadrature Mach-Zehnder Modulator (PMQ Modulator)

The PMQ modulator impresses the optical phase modulation onto the Tx CW source output. Electrical drive signals are provided from four modulator RF drivers and may be differential or single-ended, depending on the material and/or design of the optical modulators.

The modulator comprises X and Y polarization paths which are orthogonally polarization multiplexed prior to coupling into the single mode fiber output. Power in the two polarization paths may be balanced by the action of variable optical attenuator (VOA) or semiconductor amplifier (SOA) functions. Prior to launch into the output fiber the total power shall be controlled by a shutter, variable optical attenuator (VOA), or optical amplifier (SOA or EDFA) using associated tap monitoring photodiodes.

The individual Mach-Zehnder (MZ) modulator elements have electrodes that allow the phase imbalance between their arms to be adjusted to maintain optimum system performance over life, wavelength and temperature. Control is facilitated using various in-line and complimentary optical tap monitoring points. CFP2-ACO operating Classes are introduced in Section 5. For Class 1 and Class 2 operation it is expected that all control for bias and imbalance of the MZ elements will be controlled by the module itself, or via the management interface (MDIO). For Class 3 operation the imbalance of the MZ elements can optionally be controlled by the Host using both the MDIO interface and the Analogue Control Interface.

#### 4.5 Intradyne Coherent Receiver (ICR)

The ICR function may be a stand-alone function within the CFP2-ACO or it may be physically integrated with other functions such as an LO source. The Ref. [7] ICR and the Ref. [13]  $\mu$ ICR are anticipated implementations for this function. The Rx optical input signal may be monitored and controlled by optical photodiode tap and VOA functions before or after the polarization demultiplexing occurs within the ICR.

The ICR function shall provide Rx optical input polarization demultiplexing, LO splitting, and 90-degree mixer hybrids feeding eight photodiodes in 4 balanced pairs. Four differential transimpedance amplifiers (TIAs) shall amplify the received X and Y polarization quadrature signals (XI,XQ,YI,YQ) and AC couple them to the CFP2 connector Rx differential signal pairs for return to the Host.

The TIAs in the ICR function enable multiple signal monitors and control methods. The most notable TIA control choice is between an automatic or manual gain control operating mode (AGC or MGC). The TIAs may also facilitate a bandwidth equalization function and provide various input signal strength and/or output level monitors.

In the AGC operating mode there is RF output level adjust control available on the management interface and in the MGC operating mode an external signal is used to control the gain of each differential amplifier. The MGC external gain control can be provided via management interface registers or via the Analogue Control Interface (ACI).

#### 4.6 MZ Modulator RF Drivers

The MZ modulator RF drivers amplify the signals from the Host that are delivered across the CFP2 transmit-side connector interface. They drive the optical MZ modulators at a chosen fraction of 2×Vpi, dependent on the CFP2-ACO operating class and modulation format.

RF drivers are likely to be one of the more highly power dissipative components within the CFP2-ACO module, so they require appropriate heatsinking for long term operation.

The RF drivers may be controlled from the management interface registers and/or their output drive level may be actively controlled. To assist with accurate drive level control the driver function may include output side RF detectors which return mean or peak signal levels.

RF drivers shall provide either a limiting or linear drive transfer characteristic in order to deliver the Class 1 or Class 2&3 operating regimes respectively.

#### 4.7 Optical Power Monitoring and Control

Optical power monitoring and control are key parts of the functionality in the CFP2-ACO module. The electronics within the module must process the various monitoring signals and make them available over the management interface (MDIO) or send them via the Analogue Control Interface (ACI). Example requirements for the power monitoring and control functions include the following:

- Maintain stable total output power.

- Adjust output power to match the use situation.

- Shutter Tx output power during tuning and set up operations.

- Balance X and Y polarization optical powers.

- Monitor or adjust modulation depth to suit modulation type.

- Maintain modulator imbalance and bias point over time, temperature and wavelength.

- Control receiver optical signal level.

- Adjust receiver output voltage swing.

- Adjust receiver bandwidth or peaking function, if available.

- Indicate received signal strength

- Alarm on LOS.

### 4.8 MDIO Management Interface Specification

The Management Data Input/Output interface is the main way of communicating with the CFP2-ACO module. The interface implements a clause 45 compliant IEEE Std. 802.3<sup>TM</sup>-2012 [8] management data interface that allows control information to be sent to the CFP2-ACO module as required. The MDIO bus carries bidirectional data and the MDC signal is the associated clock. Three hardware port address lines (PRTADR0 to PRTADR2) allow multiple modules to be controlled from a single Host. The MDIO Management Interface Specification (MIS) is detailed in Section 11.

#### 4.9 Electronics

The CFP2-ACO needs to include the necessary electronics to realize communications and control functions for all the electro-optic elements. These electronics will include power supplies with appropriate filtering, control elements such as micro-processors or FPGAs, and bias circuitry for modulator elements and photodiodes. The cumulative power dissipation of all the electronics and electro-optic functions need to be within the specified power dissipation limits for the CFP2-ACO module, provided in Section 6.4.

# 5 **CFP2-ACO Module Classification by Electrical Interface**

Three broad classes of operation for the CFP2-ACO module are necessary to meet the requirements of users, as shown in Table 2. These operation classes may be realized by a single configurable module or in optimized module types,

depending on the technical feasibility and the cost of providing a single module solution.

For the implementer of the CFP2-ACO module these operation classes vary in the choice of Tx RF drive condition (linear/limiting) and in the presence of a possible Analog Control Interface (ACI) on the connector pin map.

| Class | Application                                                              | Control Interface                                                                                 | Connector Pin Map  |

|-------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|

| 1     | DP-BPSK and DP-QPSK<br>with Limiting Tx RF<br>Driver                     | Control via MIS/MDIO<br>instruction set.                                                          | See Section 8.2.1. |

| 2     | Enhanced DP-BPSK,<br>DP-QPSK and DP-<br>xQAM with Linear Tx RF<br>Driver | Control via MIS/MDIO<br>instruction set.                                                          | See Section 8.2.1. |

| 3     | Enhanced DP-BPSK,<br>DP-QPSK and DP-<br>xQAM with Linear Tx RF<br>Driver | Control via MIS/MDIO<br>instruction set plus <b>an Analog</b><br><b>Control Interface (ACI)</b> . | See Section 8.2.2. |

Table 2: CFP2-ACO Module Classification by Electrical Interface

Note for a Class 3 CFP2-ACO the level of implementation coverage for the ACI is at the discretion of the vendor. Any ACI function identified in the pin map of Figure 10b that is not implemented by the module shall be left as not-connected (N.C.) within the module. The available ACI functionality can be queried from the **BB02** *Tx Analog Control Interface Availability* register and Bit 6 of the **BB8B** *Rx Subsystem Features* register.

### 6 **CFP2-ACO Module Mechanicals and Power**

#### 6.1 Overview

The CFP2 form factor was designed by the CFP MSA to be hot-pluggable into a faceplate slot on a packet optical switch or line-side transport card. Surface mounted cages (see Section 8.1.8) on the card provide physical alignment between the CFP2 modules and Host PCB surface mounted electrical connectors (see Section 8). The cages also provide riding heat sinks through which the majority of dissipated power is removed from the CFP2. Ensuring the thermal interface between a CFP2 module and the riding heat sink is made in a repeatable manner is critical to ensure the CFP2 module does not exceed its upper operating temperature (See Section 7).

#### 6.2 Mechanical Dimensions

Normative engineering drawings of the CFP2 form factor, cages and connectors are given in Ref. [11]. Further detail on the mechanical characteristics of the CFP2 housing are given in Ref. [3], which should be read in conjunction with this IA for a successful CFP2-ACO implementation. Table 3 outlines the CFP2-ACO relevant sections in the Ref. [3] CFP-MSA Hardware Specification.

| CFP MSA Hardware<br>Specification [Ref 3.]                  | Topic | Comment                                                                                                                                                              |  |

|-------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Section 5.3 CFP2 Module<br>Dimensions                       |       | Simple mechanical outline.                                                                                                                                           |  |

| Section 5.3.1 CFP2 Mechanical<br>Surface<br>Characteristics |       | In addition see Section 7.3 and 7.4 below<br>for recommendations on the CFP2-ACO<br>thermal interface area dimensions, as<br>well as surface flatness and roughness. |  |

| Section 5.3.2 CFP2 Insertion &<br>Extraction                |       | Details insertion, extraction and retention forces.                                                                                                                  |  |

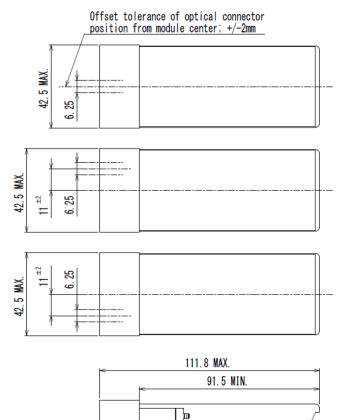

#### 6.3 Optical Connector

The optical port connections on the front of the CFP2 are detailed in Ref. [3] and Ref. [11]. While the CFP2 MSA allows for MPO12 and MPO24 connector options, the CFP2-ACO application uses only the duplex LC connector configuration.

In addition to the centered duplex LC connector location specified by the CFP MSA, the CFP2-ACO IA also optionally allows the optical port position on the front of the module to be either left or right-justified if needed to enable a certain vendor-specific implementation technology. The centered, left-justified and right-justified connector positions with dimensional tolerances are provided in Figure 7.

The bail latch dimensions are not specified, for consistency with the CFP2 MSA specification in Ref. [3].

# Figure 7: CFP2-ACO Allowed Connector Positions (Centered, Left Justified, and Right Justified) with Dimensional Tolerances.

#### 6.4 Module Power Dissipation Classes

The *Power Dissipation Classes* for CFP2 modules are defined in Section 4.2 of Ref. [3]. The CFP2-ACO shall use these same definitions that range from a maximum total power dissipation of 3 Watts (*Power Dissipation Class* 1) in 3W increments up to 18 Watts (*Power Dissipation Class* 6).

Register **807E** bits 6-7 provide the *Power Dissipation Class* for the CFP2-ACO module.

Class 1 CFP2-ACO modules shall be *Power Dissipation Class* 4 or better, i.e. <12W.

#### 6.5 Module Bail Latch Color

The CFP2-ACO bail latch color shall be a pale orange. One possible implementation would be Pantone 1575C.

# 7 CFP2-ACO Module Thermal Interface Requirements

#### 7.1 Data Requirements

The basic thermal data reporting requirements for the CFP2 ACO module, following Ref. [12], are as follows:

- a) Maximum Power Dissipation at EOL Long Term Operating Case Temperature

- b) Maximum Power Dissipation at EOL Short-Term Operating Case Temperature

- c) Minimum Power Dissipation at BOL Short-Term Operating Case Temperature

- d) Monitor Point Location within the Thermal Interface Area

- e) Maximum Long-Term Operating Temperature at the Monitor Point

- f) Maximum Short-Term Operating Temperature at the Monitor Point

- g) Minimum Operating Temperature at the Monitor Point

- h) Thermal Interface Resistance

- i) Surface Flatness of the Thermal Interface Area

- j) Surface Roughness across the Thermal Interface Area

#### 7.2 Thermal Environment

To define the thermal interface requirements, the CFP2-ACO thermal environment is assumed to be that of a shelf level product, as defined by Telcordia NEBS requirements in Ref. [14], with 55°C ambient air, corresponding to a 70°C or greater *Monitor Point* maximum temperature for short-term operation.

#### 7.3 Thermal Interface Area

For a *Power Dissipation Class* 4 CFP2-ACO module (<12W) the *Power Density Class* of the module is pd05 (<0.5W/cm<sup>2</sup>), as defined in Ref. [12].

The top surface of the CFP2-ACO module that lies directly under the cage opening shall be dimensionally controlled to enable a good thermal interface with the riding heat sink. The thermal interface area is defined in Section 7.2 of Ref. [12] as the heat transfer contact area between the module and heat sink, centered with respect to the cage opening, but typically at most 0.5 mm less in width, and 2 mm less in depth.

In Ref. [3] an example cage opening of 37.8 mm wide x 71 mm deep is provided for the generic CFP2 module. It is recommended that this cage opening be maximized for the CFP2-ACO application using the cage design principles implemented for the CFP4 Baseline Design Rev. R available at Ref. [1].

The normal force between the heat sink and the CFP2 ACO module is limited to 15N as specified in Ref [3].

#### 7.4 Module Thermal Interface Surface Requirements

To ensure good repeatable heat sink performance it is recommended that the CFP2-ACO thermal interface area have flatness  $\leq 0.08$  mm and a surface finish  $\leq 0.8 \mu$ m Ra. This is to ensure that system designers can provide adequate cooling for modules with similar or better heat sink contact surface preparation. The goal is to have an overall thermal interface resistance of  $<2 \text{ °C-cm}^2/W$ , as defined in Ref. [12].

#### 7.5 Thermal Sensor Calibration

The CFP2 ACO internal temperature sensor is to be calibrated to report the temperature at the monitor point with >95% of the heat removed through the heat sink. This implies that the CFP2 module is in thermal equilibrium with the cage and PCB so that little net heat is transferred in or out of locations other than the thermal interface area.

### 8 CFP2-ACO Electrical Connector Interface

#### 8.1 104-Pin Electrical Connector

#### 8.1.1 Background

The Plug and Host connector parts for the CFP2 are detailed in the CFP MSA Ref. [3]. The Plug is the male connector part attached to the CFP2-ACO module PCB. The Host Connector is the female connector part that is located at the rear of the CFP2 cage, attached to the line or switch card. The female Host Connector is covered by a Host Connector Cover Assembly that includes gaskets around the opening for the Plug connector to provide electromagnetic shielding.

Both connector parts are of a molded polymer construction with plated metal contact inserts. The contact pitch is 0.6mm and there are 104 contacts.

Performance characterization of several connector implementations in provided in Appendix I.

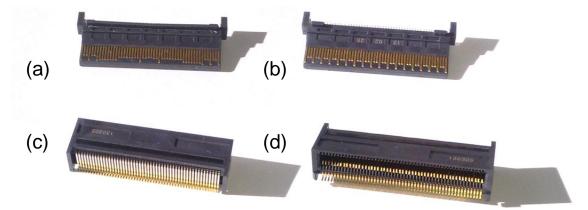

#### 8.1.2 Photographs of Connector: Plug and Host

Representative examples of both the Plug and Host Connector parts are provided in Figure 8.

Figure 8 : (a) Plug bottom side showing sequenced connection contacts, (b) Plug top side showing GSSG format RF contact groups, (c) Host Connector rear view – pins connected to Host PCBs, (d) Host Connector front view – accepts the Plug.

#### 8.1.3 Suppliers and Example Part Numbers

At the time of publication there are three suppliers of the connector for the CFP2-ACO. The suppliers listed in alphabetical order and example connector part numbers are given in Table 4 for reference. It is the responsibility of the connector users to ensure that an appropriate part and plating finish is specified for their requirements.

| Supplier             | Example Plug Part<br>Number        | Example Host<br>Part Number        | Comments                                                                                                                                                                                                                                      |

|----------------------|------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amphenol             | P-U56-B104-XXXX                    | P-U99-B104-XXXX                    | -XXXX represents plating<br>thickness, packaging and<br>other options                                                                                                                                                                         |

| TE Connectivity      | 2274844-1                          | 2274845-1                          |                                                                                                                                                                                                                                               |

| Yamaichi Electronics | CN121P-104-0003<br>CN121P-104-1003 | CN121S-104-0001<br>CN121S-104-1001 | -000X are the Standard<br>Performance version (28G).<br>-100X are the High<br>Performance version (56G).<br>These part numbers come<br>with tray packaging. Different<br>packaging option and plug<br>PCB thickness options are<br>available. |

| Other                |                                    |                                    | Add details when available                                                                                                                                                                                                                    |

#### 8.1.4 Reliability and Environmental Test Documentation

At the time of publication the reliability documents given in Table 5 are available from the respective suppliers. The listed suppliers have completed and passed the mixed flowing gas test requirements of GR-1217-CORE.

| Supplier                | Document                                        | Date                           | Qualification Target |

|-------------------------|-------------------------------------------------|--------------------------------|----------------------|

| Amphenol                | QTP9300537                                      | 28 <sup>th</sup> February 2014 | GR-1217-CORE         |

| Yamaichi<br>Electronics | RE-5354. CN121 Series<br>Evaluation Test Report | 31 <sup>st</sup> January 2013  | GR-1217-CORE         |

| Other 1                 |                                                 |                                |                      |

| Other 2                 |                                                 |                                |                      |

#### Table 5: CFP2 Connector Reliability Documents

#### 8.1.5 Connector Ratings

The current rating per contact pin for the various connectors is given in Table 6 along with the voltage rating and the allowed number of mating cycles.

| Supplier    | Current<br>Capacity per<br>Pin (mA) | Voltage Rating per pin (V) | Rated Mating Cycles |

|-------------|-------------------------------------|----------------------------|---------------------|

| Amphenol    | 1875                                | TBC                        | <=200               |

| Yamaichi    | 1250                                | 120                        | <=200               |

| Electronics |                                     |                            |                     |

| Other 1     |                                     |                            |                     |

| Other 2     |                                     |                            |                     |

#### Table 6: CFP2 Connector Ratings

#### 8.1.6 **RF Path S-Parameters**

Informative reference data is provided in Appendix I (Section 17).

#### 8.1.7 Connector Cross Mating

This is the subject of further study at the time of publication.

#### 8.1.8 Related CFP2 Cage Products

Manufacturers supply the hardware for single and/or dual CFP2 PCB mounting cages to facilitate the manufacture of line cards, switch cards, or module compliance boards (MCB).

Figure 9: Single CFP2 Cage Illustration (informative).

Some *informative* part numbers are given in Table 7 and an example of a single CFP2 mounting cage is shown in Figure 9. It is left to the user to ensure that they specify the correct part variant and options for their requirements.

| Supplier             | Single Slot Cage | Dual Slot Cage  | Comments                                     |

|----------------------|------------------|-----------------|----------------------------------------------|

| Amphenol             | P-U98-B1XX-X0XX  | P-U98-B2XX-X0XX |                                              |

| Yamaichi Electronics | CN121A-104-0003  | CN121A-104-0004 |                                              |

| TE Connectivity      | 2274842-1        | 2287075-1       | Cage kits including<br>cage/receptacle/cover |

| Other 1              |                  |                 |                                              |

Table 7: Related CFP2 Cage Part Numbers

### 8.2 Electrical Pin Maps

### 8.2.1 Class 1 and Class 2 Electrical Pin Map

The Class 1 and Class 2 CFP2-ACO module electrical pin map is given in Figure 10a. The pin-out changes in Figure 10a relative to the "Top/Bottom" pin allocation in Ref. [4] are identified by an asterisk on the pin number. These changes include the following: MCLK outputs shall be N.C. within the module; REFCLK inputs shall be appropriately terminated inside the CFP2-ACO, although for Class 2 these inputs can be optionally N.C in the module; the CFP2 4x25G RX0-3 and TX0-3 data pins shall be mapped to the coherent Tx/Rx channels as outlined in Section 8.3. In Figure 10a the [0,0,0] Tx/Rx channel mapping is used for illustrative purposes.

The Class 1 and Class 2 CFP2-ACO module electrical pin map **does not** impede the Host implementing a CFP2 "universal slot" compatible with both the CFP2-ACO **and** any selected set of the CFP2 client module electrical interfaces given in Ref. [4].

# 8.2.2 Class 3 Electrical Pin Map with the Full Superset Analog Control Interface (ACI)

The Class 3 CFP2-ACO module electrical pin map with the full superset Analog Control Interface (ACI) is given in Figure 10b. Any ACI pin in Figure 10b whose function is not implemented by the module shall be left as N.C. within the module. The pin-out changes in Figure 10b relative to the "Top/Bottom" pin allocation in Ref. [4] are identified by an asterisk on the pin number. In Figure 10b the CFP2 4x25G RX0-3 and TX0-3 data pins have also been mapped for illustrative purposes to coherent Tx/Rx channels using the [0,0,0] Tx/Rx channel mapping defined in Section 8.3.

The superset ACI has been implemented using the RF data pins un-used by the 4x25G CFP2 client modules (N.C. in Ref. [4] "Top/Bottom" pin allocations), and the optional MCLK output pins. These are all 4<sup>th</sup> engagement category<sup>3</sup> connector pins. The detailed ACI I/O requirements are given in Section 10. Note there shall be a one-to-one physical correspondence between any Tx/Rx ACI pin and its associated RF Signal pins regardless of the Tx/Rx channel mapping used. For example, pin 67 is physically mapped to the RF hardware driving pins 72-73, and similarly for all other ACI input/output connections. Note also that all connector pins used for the analog control interface are N.C. pins on the Class 1 and 2 CFP2-ACO electrical connector interfaces.

When the ACI is used, the Host is **limited** to implementing a CFP2 "universal slot" that is compatible with **only** the 4X25G CFP2 client (Ref. [4] "Top/Bottom" pin allocations) and the CFP2-ACO. This is an acknowledged and accepted limitation of the Host using the ACI.

<sup>&</sup>lt;sup>3</sup> As defined by Section 5.2.3 of Ref. [3].

#### IA # OIF-CFP2-ACO-01.0 IA for CFP2 Analog Coherent Optics Module

| CFP2-ACO         CFP2-ACO           Bottom: Class 1/2         Top: Class 1/2           1         GND         104         GND           2*         N.C.         103         N.C.           3*         N.C.         102         N.C.           4         GND         101         GND           5         N.C.         102         N.C.           6         N.C.         99*         TX_Xlp (RF Mapping [0,0,0])           6         N.C.         99*         TX_Xln (RF Mapping [0,0,0])           7         3.3V_GND         98         GND           8         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           10         3.3V         95         GND           11         3.3V         94         N.C.           12         3.3V         94         N.C.           13         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           15         VN_LIO_A         90         N.C.           16         VND_IO_A         90         N.C.           17 <th>GND<br/>GND<br/>GND<br/>RF Signal<br/>3.3V Supply<br/>Vendor IO pi<br/>MSA Pins<br/>ACI-Input</th>                            | GND<br>GND<br>GND<br>RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1       GND       104       GND         2*       N.C.       103       N.C.         3*       N.C.       102       N.C.         4       GND       101       GND         5       N.C.       100*       TX_Xlp (RF Mapping [0,0,0])         6       N.C.       99*       TX_Xln (RF Mapping [0,0,0])         7       3.3V_GND       98       GND         8       3.3V_GND       97*       TX_XQp (RF Mapping [0,0,0])         9       3.3V       96*       TX_XQn (RF Mapping [0,0,0])         10       3.3V_GND       97*       TX_XQn (RF Mapping [0,0,0])         10       3.3V       96*       TX_XQn (RF Mapping [0,0,0])         11       3.3V       94       N.C.         12       3.3V       94       N.C.         12       3.3V       93       N.C.         13       3.3V_GND       91       N.C.         14       3.3V_GND       92       GND         14       3.3V_GND       91       N.C.         15       VND_IO_A       90       N.C.         16       VND_IO_B       89       GND         17       PRG_CNTL2                                                                                                                                                                                                     | view<br>from<br>top<br>RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input |

| 2*         N.C.         103         N.C.           3*         N.C.         102         N.C.           4         GND         101         GND           5         N.C.         100*         TX_Xlp (RF Mapping [0,0,0])           6         N.C.         99*         TX_Xln (RF Mapping [0,0,0])           7         3.3V_GND         98         GND           8         3.3V_GND         98         GND           10         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           10         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           10         3.3V         95         GND           11         3.3V         94         N.C.           12         3.3V         94         N.C.           13         3.3V_GND         91         N.C.           13         3.3V_GND         91         N.C.           13         3.3V_GND         91         N.C.           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_A         90         N.C.           18         PRG_CNTL2                                                                                                                                      | view<br>from<br>top<br>RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input |

| 4         GND         101         GND           5         N.C.         100*         TX_XIp (RF Mapping [0,0,0])           6         N.C.         99*         TX_XIn (RF Mapping [0,0,0])           7         3.3V_GND         98         GND           8         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           10         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           10         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           10         3.3V         95         GND           11         3.3V         94         N.C.           12         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           13         3.3V_GND         91         N.C.           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL2         87*         TX_YIp (RF Mapping [0,0,0])           18         PRG_CNTL3         86         GND <td>top<br/>RF Signal<br/>3.3V Supply<br/>Vendor IO pi<br/>MSA Pins<br/>ACI-Input</td> | top<br>RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                 |

| 5         N.C.         100*         TX_XIp (RF Mapping [0,0,0])           6         N.C.         99*         TX_XIn (RF Mapping [0,0,0])           7         3.3V_GND         98         GND           8         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           10         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           11         3.3V         94         N.C.           12         3.3V         94         N.C.           13         3.3V_GND         91         N.C.           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL1         88*         TX_YIp (RF Mapping [0,0,0])           18         PRG_CNTL2         87*         TX_YIp (RF Mapping [0,0,0])           19         PRG_CNTL3         86         GND           20         PRG_ALRM1         85*         TX_YQn (RF Mapping [0,0,0])           21                                                                    | GND<br>RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                 |

| 6         N.C.         99*         TX_XIn (RF Mapping [0,0,0])           7         3.3V_GND         98         GND           8         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V         96*         TX_XQp (RF Mapping [0,0,0])           9         3.3V         96*         TX_XQp (RF Mapping [0,0,0])           10         3.3V         95         GND           11         3.3V         94         N.C.           12         3.3V         94         N.C.           12         3.3V         93         N.C.           13         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL1         88*         TX_Ylp (RF Mapping [0,0,0])           18         PRG_CNTL2         87*         TX_Ylp (RF Mapping [0,0,0])           19         PRG_CNTL3         86         GND           20         PRG_ALRM1         85*         TX_YQp (RF Mapping [0,0,0])           21         PRG_ALRM3         83         GND                                                                                     | RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                        |

| 7         3.3V_GND         98         GND           8         3.3V_GND         97*         TX_XQp (RF Mapping [0,0,0])           9         3.3V         96*         TX_XQp (RF Mapping [0,0,0])           10         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           11         3.3V         95         GND           12         3.3V         94         N.C.           12         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL1         88*         TX_YIp (RF Mapping [0,0,0])           18         PRG_CNTL2         87*         TX_YIn (RF Mapping [0,0,0])           19         PRG_CNTL3         86         GND           20         PRG ALRM1         85*         TX YQp (RF Mapping [0,0,0])           21         PRG_ALRM2         84*         TX YQn (RF Mapping [0,0,0])           22         PRG_ALRM3         83         GND           23         GND         82         N.C.           24         TX_DIS         81                                                                                          | RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                        |

| 8         3.3V         GND         97*         TX_XQp (RF Mapping [0,0,0])         9         3.3V         96*         TX_XQn (RF Mapping [0,0,0])         10         3.3V         95         GND           10         3.3V         95         GND         91         N.C.           11         3.3V         94         N.C.         93         N.C.           12         3.3V_GND         92         GND         91         N.C.           13         3.3V_GND         91         N.C.         91         N.C.           14         3.3V_GND         91         N.C.         91         N.C.           15         VND_IO_A         90         N.C.         91         N.C.           16         VND_IO_B         89         GND         91         N.C.           17         PRG_CNTL1         88*         TX_YIp (RF Mapping [0,0,0])         18         PRG_CNTL2         87*         TX_YQp (RF Mapping [0,0,0])         19           18         PRG_CNTL3         86         GND         90         90         90         90         90         90         90         90         90         90         90         90         90         90         90         9                                                         | RF Signal<br>3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                        |

| 9         3.3V         96*         TX_XQn (RF Mapping [0,0,0])           10         3.3V         95         GND           11         3.3V         94         N.C.           12         3.3V         93         N.C.           12         3.3V         93         N.C.           13         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL1         88*         TX_YIp (RF Mapping [0,0,0])           18         PRG_CNTL2         87*         TX_Yun (RF Mapping [0,0,0])           19         PRG_CNTL3         86         GND           20         PRG_ALRM1         85*         TX_YQp (RF Mapping [0,0,0])           21         PRG_ALRM2         84*         TX_YQn (RF Mapping [0,0,0])           22         PRG_ALRM3         83         GND           23         GND         82         N.C.           24         TX_DIS         81         N.C.           25         RX_LOS         80         GND                                                                                                                                 | 3.3V Supply<br>Vendor IO pi<br>MSA Pins<br>ACI-Input                                     |

| 10       3.3V       95       GND         11       3.3V       94       N.C.         12       3.3V       93       N.C.         13       3.3V_GND       92       GND         14       3.3V_GND       91       N.C.         15       VND_IO_A       90       N.C.         16       VND_IO_B       89       GND         17       PRG_CNTL1       88*       TX_YIp (RF Mapping [0,0,0])         18       PRG_CNTL2       87*       TX_YIn (RF Mapping [0,0,0])         19       PRG_CNTL3       86       GND         20       PRG_ALRM1       85*       TX_YQP (RF Mapping [0,0,0])         21       PRG_ALRM2       84*       TX_YQN (RF Mapping [0,0,0])         22       PRG_ALRM3       83       GND         23       GND       82       N.C.         24       TX_DIS       81       N.C.         25       RX_LOS       80       GND                                                                                                                                                                                                                                                                                                                                                                                          | Vendor IO pi<br>MSA Pins<br>ACI-Input                                                    |

| 11       3.3V       94       N.C.         12       3.3V       93       N.C.         13       3.3V_GND       92       GND         14       3.3V_GND       91       N.C.         15       VND_IO_A       90       N.C.         16       VND_IO_B       89       GND         17       PRG_CNTL1       88*       TX_YIp (RF Mapping [0,0,0])         18       PRG_CNTL2       87*       TX_YIn (RF Mapping [0,0,0])         19       PRG_CNTL3       86       GND         20       PRG_ALRM1       85*       TX_YQn (RF Mapping [0,0,0])         21       PRG_ALRM2       84*       TX_YQn (RF Mapping [0,0,0])         22       PRG_ALRM3       83       GND         23       GND       82       N.C.         24       TX_DIS       81       N.C.         25       RX_LOS       80       GND                                                                                                                                                                                                                                                                                                                                                                                                                                   | MSA Pins<br>ACI-Input                                                                    |

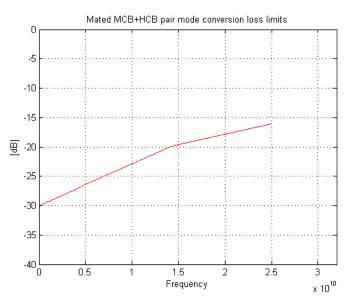

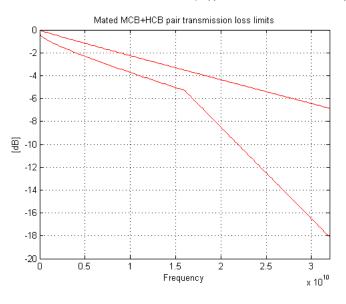

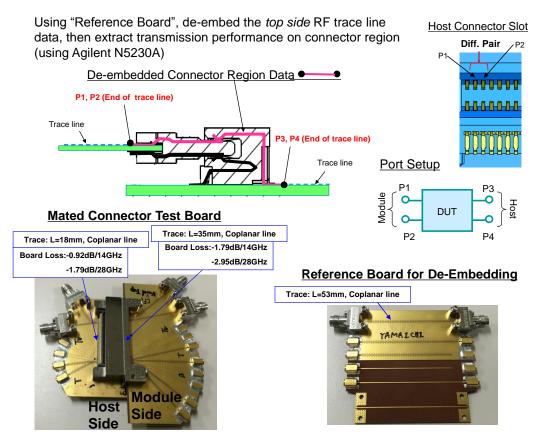

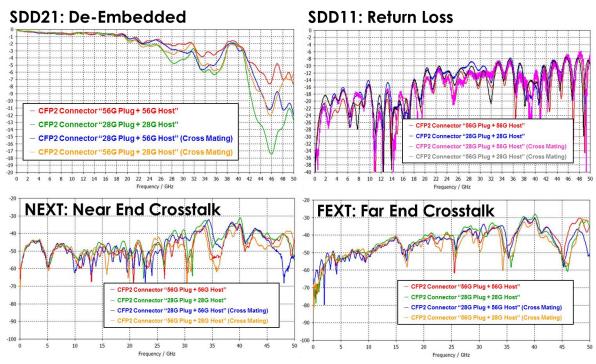

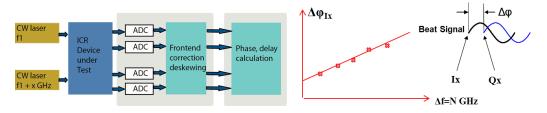

| 12         3.3V         93         N.C.           13         3.3V_GND         92         GND           14         3.3V_GND         91         N.C.           15         VND_IO_A         90         N.C.           16         VND_IO_B         89         GND           17         PRG_CNTL1         88*         TX_YIp (RF Mapping [0,0,0])           18         PRG_CNTL2         87*         TX_YIn (RF Mapping [0,0,0])           19         PRG_CNTL3         86         GND           20         PRG_ALRM1         85*         TX_YQp (RF Mapping [0,0,0])           21         PRG_ALRM2         84*         TX_YQn (RF Mapping [0,0,0])           22         PRG_ALRM3         83         GND           23         GND         82         N.C.           24         TX_DIS         81         N.C.           25         RX_LOS         80         GND                                                                                                                                                                                                                                                                                                                                                               | ACI-Input                                                                                |