Implementation Agreement for Micro Intradyne Coherent Receivers

IA # OIF-DPC-MRX-02.0

June 21, 2017

Implementation Agreement created and approved by the Optical Internetworking Forum <u>www.oiforum.com</u>

The OIF is an international non-profit organization with over 100 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements.

With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with CFP-MSA, COAST, Ethernet Alliance, Fibre Channel T11, IEEE 802.1, IEEE 802.3, IETF, InfiniBand, ITU-T SG13, ITU-T SG15, MEF, ONF, Rapid I/O, SAS T10, SFF Committee, TMF and TMOC.

For additional information contact: The Optical Internetworking Forum, 5177 Brandin Ct. Fremont, CA 94538 510-492-4040 □ <u>info@oiforum.com</u>

www.oiforum.com

#### Working Group: Physical and Link Layer (PLL) Working Group

TITLE: Implementation Agreement for Micro Intradyne Coherent Receivers

#### SOURCE: TECHNICAL EDITOR Gert Sarlet Finisar Corp. 1389 Moffett Park Drive Sunnyvale, CA 94089, USA Phone: +1 267 830 3730 Email: gert.sarlet@finisar.com

#### PLL WORKING GROUP CHAIR

David R. Stauffer Kandou Bus, S.A. EPFL Innovation Park, Building I 1015 Lausanne, Switzerland Phone: +1 802 316 0808 Email: david@kandou.com

PLL WORKING GROUP – OPTICAL VICE CHAIR Karl Gass Qorvo, Inc. Phone: +1 505 301 1511 Email: <u>iamthedonutking@mac.com</u>

ABSTRACT: Implementation agreement for a micro intradyne coherent receiver (ICR) – Revision 02.0, with additions addressing higher bandwidth / higher symbol rate applications.

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

#### © 2017 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

# **Table of Contents**

| TAB  | LE OF CONTENTS                                                           | 5  |

|------|--------------------------------------------------------------------------|----|

| LIST | OF FIGURES                                                               | 6  |

| LIST | COF TABLES                                                               | 6  |

| DOC  | CUMENT REVISION HISTORY                                                  | 7  |

| 1    | Introduction                                                             | 8  |

| 2    | Functionality                                                            |    |

| 3    | High Speed Electrical Interface                                          |    |

|      | 3.1 High Speed Electrical Interface in the Type 1 Mechanical Form Factor |    |

|      | 3.2 High Speed Electrical Interface in the Type 2 Mechanical Form Factor |    |

| 4    | Low Speed Electrical Interface                                           |    |

|      | 4.1 Low Speed Electrical Interface in the Type 1 Mechanical Form Factor  |    |

|      | 4.2 Low Speed Electrical Interface in the Type 2 Mechanical Form Factor  |    |

| 5    | Environmental and Operating Characteristics                              |    |

| 6    | Electro-Optical Characteristics (Normative)                              |    |

|      | 6.1 General Electro-Optical Characteristics                              |    |

|      | 6.2 RF Frequency Response                                                |    |

| 7    | Mechanical                                                               |    |

|      | 7.1 General Overview and Fiber Types                                     | 24 |

|      | 7.2 Type 1 Mechanical Form Factor                                        |    |

|      | 7.3 Type 2 Mechanical Form Factor                                        |    |

|      | 7.4 Type 1 and Type 2 Mechanical Form Factor Dimensions                  |    |

| 8    | Low Speed Electrical Interface Implemented using SPI Control             |    |

|      | 8.1 SPI Enabled Low Speed Electrical Interface Pin Assignment            |    |

|      | 8.2 Functional Diagram of µICR with SPI Interface                        |    |

|      | 8.3 SPI Interface Voltage and Control Specifications                     | 33 |

|      | 8.4 SPI Read / Write Datagram                                            |    |

|      | 8.5 SPI Read / Write Operation Timing Diagrams                           |    |

|      | 8.6 SPI Timing Specifications                                            |    |

|      | 8.7 SPI Registers Specification                                          | 36 |

| 9    | References                                                               |    |

|      | 9.1 Normative references                                                 |    |

|      | 9.2 Informative references                                               | 39 |

| 10   | ) Appendix A: Glossary                                                   | 39 |

| 11   |                                                                          |    |

| 12   |                                                                          |    |

| 13   | Appendix D: List of companies belonging to OIF when document is approved | 41 |

# List of Figures

| Functional blocks in a coherent receiver                                                                          | .10                        |

|-------------------------------------------------------------------------------------------------------------------|----------------------------|

| Definition of hybrid angle.                                                                                       | .10                        |

| High speed electrical interface definition.                                                                       | .12                        |

| High speed flexible PCB interface for the Type 2 mechanical form factor enabling                                  |                            |

| ion to the CFP2-ACO module environment                                                                            | 13                         |

| Low speed electrical interface in the Type 2 form factor                                                          | 16                         |

| Informative example: recommended maximum LO power as a function of Signal                                         |                            |

| r for a $\mu$ ICR with R <sub>SIG</sub> = 0.10 A/W, R <sub>LO</sub> = 0.05 A/W, and peak-to-peak differential lin | ear                        |

| dynamic range of 0.80 mA.                                                                                         | 20                         |

| Normalized O/E $S_{21}$ transfer function masks for the class 20, 30, and 40 µICR                                 |                            |

| ctively                                                                                                           | 22                         |

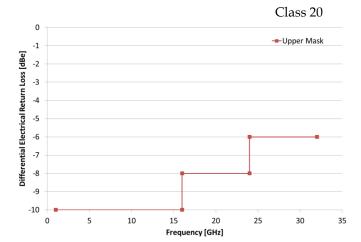

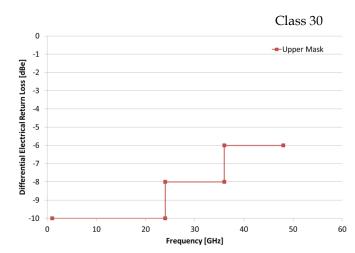

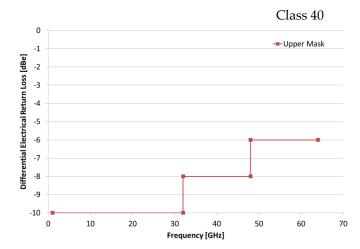

| Differential $S_{22}$ electrical return loss masks for the class 20, 30, and 40 µICR,                             |                            |

| ctively                                                                                                           | 23                         |

| Mechanical drawing for Type 1 form factor.                                                                        | 25                         |

| Host PCB landing pad locations for low speed pins - Type 1 form factor                                            | 25                         |

| Informative host PCB landing pad dimensions for high speed pins - Type 1 form                                     |                            |

|                                                                                                                   | 26                         |

| Mechanical drawing for Type 2 form factor.                                                                        | 27                         |

| Possible adaptation of the Type 2 form factor low speed and RF interfaces to the                                  |                            |

| ACO module environment                                                                                            | 27                         |

| Possible adaptation of the Type 2 form factor to the CFP2-ACO module environmer                                   | nt –                       |

| erface detail                                                                                                     | 28                         |

| Schematic diagram of a µICR with SPI control                                                                      | .32                        |

| SPI write operation timing diagram.                                                                               | .34                        |

| SPI read operation timing diagram.                                                                                |                            |

| SPI client read/write timing                                                                                      | .35                        |

| SPI client reset timing - asynchronous.                                                                           | 36                         |

|                                                                                                                   | Definition of hybrid angle |

# List of Tables

| Table 3-1  | High speed electrical interface description.                                      | 12 |

|------------|-----------------------------------------------------------------------------------|----|

|            | Type 1 high speed electrical interface dimensions                                 |    |

| Table 3-3  | Allowable channel mappings for the µICR high speed electrical interface           | 13 |

| Table 4-1  | Low speed electrical interface definition.                                        | 15 |

| Table 5-1  | Operating characteristics.                                                        | 17 |

| Table 6-1  | Electro-optic characteristics (normative).                                        | 18 |

| Table 7-1  | Input fiber characteristics.                                                      | 24 |

| Table 7-2  | Type 1 and Type 2 mechanical form factor dimensions (in mm)                       | 29 |

| Table 7-3  | Possible dimensions for the adaptation of the Type 2 form factor low speed and RF |    |

| interf     | faces to the CFP2-ACO module environment.                                         | 29 |

| Table 8-1  | SPI enabled low speed electrical interface pin assignment                         | 31 |

| Table 8-2  | SPI voltage and control specification.                                            | 33 |

| Table 8-3  | SPI data telegram structure.                                                      | 33 |

| Table 8-4  | SPI read / write timing specifications.                                           | 35 |

| Table 8-5  | General SPI register mapping.                                                     | 36 |

| Table 8-6  | General manufacturer information register map.                                    | 36 |

| Table 8-7  | Base set of SPI control functions and registers.                                  | 37 |

| Table 8-8  | Vendor specific SPI control functions and registers.                              | 38 |

| Table 11-1 | Additional electro-optical characteristics (informative)                          | 40 |

# **Document Revision History**

| Document         | Date           | Revisions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OIF-DPC-MRX-01.0 | March 31, 2015 | First release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| OIF-DPC-MRX-02.0 | June 21, 2017  | <ul> <li>Second release, with following edits:</li> <li>Updated introduction to make text symbol rate / data rate agnostic;</li> <li>Re-ordered paragraphs to improve document flow;</li> <li>Moved electro-optical characteristics from informative appendix to normative section;</li> <li>Introduced three classes of micro-ICR (Class 20, 30 and 40), corresponding to devices having notional S<sub>21</sub> bandwidths of 20GHz, 30GHz, and 40GHz, respectively;</li> <li>Added target masks for S<sub>21</sub> optical-to-electrical transfer function and S<sub>22</sub> electrical return loss frequency responses;</li> </ul> |  |  |

# 1 Introduction

This document details an Implementation Agreement for a Micro-Intradyne Coherent Receiver ( $\mu$ ICR) targeting modulation and data-rate agnostic coherent applications having nominal symbol rates up to 64Gbaud. The IA aims to identify and specify the common features and properties of coherent receivers to enable them to broadly meet the needs of current and future coherent systems.

The µICR Implementation Agreement defines the following: (1) Required functionality; (2) High speed electrical interfaces; (3) Low speed electrical interfaces; (4) Environmental and operating characteristics; (5) Electro-optical characteristics; (6) Mechanical requirements. Additional informative electro-optical specifications are also included in Appendix B.

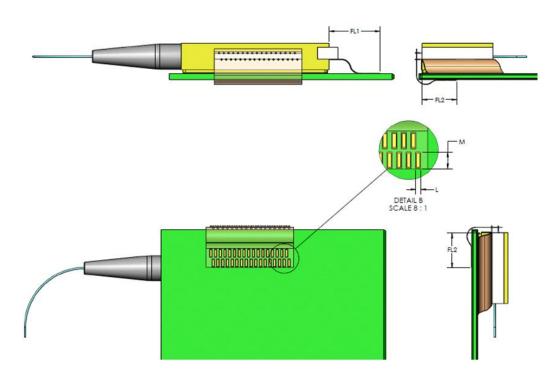

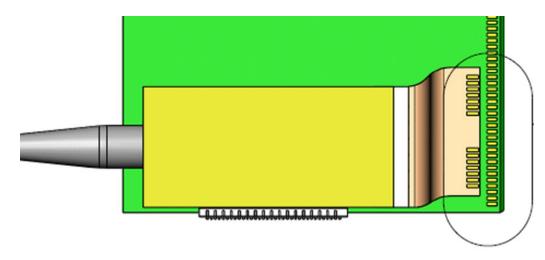

Both a primary and alternative electro-mechanical form factor are defined in this revision of the  $\mu$ ICR IA. The primary electro-mechanical form factor (Type 1) uses a surface mount configuration. The alternative electro-mechanical form factor (Type 2) employs flexible PCBs for the DC and RF I/O interfaces. The Type 2 form factor can allow for the direct connection of the  $\mu$ ICR hot zone to the heat sinking surface in the use-case of a pluggable coherent module. Differences between the Type 1 and Type 2 form factors are highlighted where appropriate, otherwise common characteristics are required for the two form factors.

The IA also defines an option for a low speed electrical interface that incorporates an SPI bus to control the Trans-Impedance Amplifiers (TIAs) in the  $\mu$ ICR. The SPI enabled low speed interface is equally applicable to either the Type 1 and Type 2 electro-mechanical form-factors. The choice of a combination of the package form factor and whether the low speed electrical interface incorporates an SPI bus will be specific to the application and/or  $\mu$ ICR customer preference.

The IA does not define the technologies used to implement the IA, nor the expected optical transmission performance of coherent systems using receivers conforming to the IA.

# 2 <u>Functionality</u>

The functional blocks required to implement a coherent receiver are shown in Figure 2-1. A  $\mu$ ICR that meets the objectives of the IA contains the functionality shown within the dashed line box in Figure 2-1.

A µICR shall provide at a minimum the following functionality:

- 1. A Signal input fiber that shall be Single Mode Fiber (SMF).

- 2. A Local Oscillator (LO) input fiber that shall be Polarization Maintaining Single Mode Fiber (PM-SMF).

- 3. A polarization splitting element, separating the input Signal light into two orthogonal polarizations, with each polarization delivered to a 90 degree hybrid mixer.

- 4. A polarization maintaining power splitter or polarization splitting element, splitting the local oscillator input power equally and delivering it to the two 90 degree hybrid mixers.

- 5. Two (2) 90 degree hybrid mixers with differential optical outputs.

- 6. Eight (8) photo-detectors comprised of 4 sets of differential detectors.

- 7. Four (4) linear trans-impedance amplifiers providing differential AC coupled RF output signals [XI, XQ, YI, YQ.].

A µICR *may* also contain the following optical functionality:

- 8. Optical power tap(s) and monitor photodiode(s) in the Signal input path either before the signal polarization splitting element or in each path after the splitting element.

- 9. A variable optical attenuator in the Signal input path either before the signal polarization splitting element or in each path after the splitting element.

X (X-Pol) and Y (Y-Pol) indicate a pair of mutually orthogonal polarizations of any orientation, and I and Q are mutually orthogonal phase channels in each polarization. As shown in Figure 2-1 the µICR therefore has 4 polarization-phase RF output channels labeled as XI, XQ, YI, YQ.

**Figure 2-1** Functional blocks in a coherent receiver.

Notes:

- 1. VOA and MPD are optional. One configuration for the order of the VOA and MPD is shown. The configuration with the MPD followed by the VOA is an equally acceptable configuration. Configurations having VOAs and/or MPDs after the polarization beam splitter (one VOA/MPD per polarization) are also considered acceptable implementations.

- 2. The yellow area enclosed by the dashed line indicates the  $\mu$ ICR functionality specified in the IA.

Under internet in a setting vehice i O la set

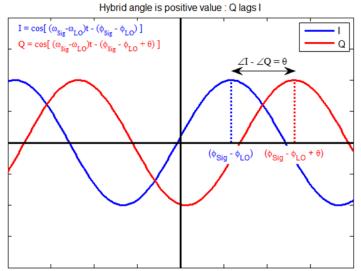

Figure 2-2 Definition of hybrid angle.

The phase relationship between I and Q outputs is established by the heterodyne technique with the frequency of the Signal input to the receiver greater than the frequency of the LO input. Under this condition, when the I and Q output waveforms are observed in the time domain, the Q channel *lags* the I Channel by nominally +90 degrees, as shown in Figure 2-2.

Channel outputs 'p' and 'n' are the complementary outputs for each polarization-phase channel and are defined such that the output voltage for 'p' increases as the Signal and Local Oscillator approach the in-phase condition to form constructive interference, and the output voltage for 'n' decreases under the same conditions.

The TIAs in the µICR function enable multiple signal monitors and control methods. The most notable TIA control selection is between automatic or manual gain control operating mode (AGC or MGC). TIAs can support AGC only, MGC only, or both – all are valid implementations. The TIAs may also facilitate a bandwidth equalization function and provide various input signal strength and/or output level monitors (PI). In the AGC operating mode there is a RF output level adjust control (Output Adjust, OA) available and in the MGC operating mode an external signal (Gain Adjust, GA) is used to control the gain of each differential amplifier.

# 3 <u>High Speed Electrical Interface</u>

#### 3.1 High Speed Electrical Interface in the Type 1 Mechanical Form Factor

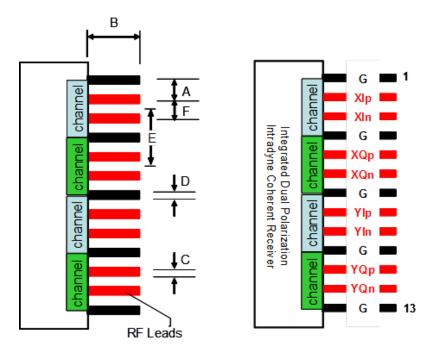

The high speed electrical output interface for a Type 1  $\mu$ ICR form-factor uses surface mounted pins in a differential co-planar waveguide arrangement (GSSG), with shared ground pins. The pin definitions and pitches shall be as detailed in Table 3-1, Table 3-2, and Figure 3-1. It is noted that alternate configurations for the differential signals shown in Figure 3-1 are acceptable.

All allowable channel mappings are enumerated in Table 3-3. The pin configuration shown in Figure 3-1 corresponds to mapping [0,0,0]. Each mapping is specified by three designations: [X:Y ; I,Q ; p/n], where a ":" is used to separate X&Y, a "," is used to separate I&Q, and a "/" is used to separate p&n. In Table 3-3 red text shows where the mapping flips occur relative to the 1st row in each group. It is important to highlight that Table 3-3 *does not* allow interleaving of the channels by polarization since this would add a non-essential level of complexity to the digital signal processing.

| Parameter             | Value                | Notes          |

|-----------------------|----------------------|----------------|

| Interface type        | Differential         |                |

| Channel number        | 4                    |                |

| Channel configuration | G-S-S-G              | Per Figure 3-1 |

| Signal line coupling  | AC                   |                |

| Signal line impedance | 100 Ohm Differential |                |

|                       | XI                   |                |

| Channel nin out       | XQ                   | Por Figure 2.1 |

| Channel pin-out       | YI                   | Per Figure 3-1 |

|                       | YQ                   |                |

| Differential pip out  | Signal               | р              |

| Differential pin-out  | Complimentary Signal | n              |

Table 3-1 High speed electrical interface description.

| Parameter                            | Symbol | Min | Тур | Max | Units |

|--------------------------------------|--------|-----|-----|-----|-------|

| Lead pitch                           | А      |     | 0.8 |     | mm    |

| Lead length (referenced from         | В      | 1.5 | 2.0 | 2.5 | mm    |

| outside wall of package, as defined  |        |     |     |     |       |

| by dimension LP2 in Section 7)       |        |     |     |     |       |

| Signal lead width                    | С      | 0.1 | 0.2 | 0.3 | mm    |

| Ground lead width                    | D      | 0.1 | 0.2 | 0.3 | mm    |

| Channel pitch                        | Е      |     | 2.4 |     | mm    |

| Signal to complimentary signal pitch | F      |     | 0.8 |     | mm    |

Table 3-2 Type 1 high speed electrical interface dimensions.

Figure 3-1 High speed electrical interface definition.

| Mapping | X:Y | I,Q                   | p/n                                          | Notes                         |  |

|---------|-----|-----------------------|----------------------------------------------|-------------------------------|--|

| [0,x,x] | X:Y |                       |                                              | Pol. cannot be interleaved    |  |

| [1,x,x] | Y:X |                       |                                              | 1 of. califiot be interfeaved |  |

| [x,0,x] |     | I,Q:I,Q               |                                              | Same across Pol.              |  |

| [x,1,x] |     | Q,I:Q,I               |                                              | Same across i oi.             |  |

| [x,2,x] |     | I,Q: <mark>Q,I</mark> |                                              | Flip across Pol.              |  |

| [x,3,x] |     | <mark>Q,I</mark> :I,Q |                                              |                               |  |

| [x,x,0] |     |                       | p/n,p/n:p/n,p/n                              | Same across Pol. and I,Q      |  |

| [x,x,1] |     |                       | n/p,n/p:n/p,n/p                              | Same across 1 of. and 1,Q     |  |

| [x,x,2] |     |                       | p/n,p/n: <mark>n/p,n/p</mark>                | Flip across Pol.              |  |

| [x,x,3] |     |                       | <mark>n/p,n/p</mark> :p/n,p/n                |                               |  |

| [x,x,4] |     |                       | p/n, <mark>n/p</mark> :p/n,n/p               | Flip across I,Q               |  |

| [x,x,5] |     |                       | <mark>n/p</mark> ,p/n: <mark>n/p</mark> ,p/n |                               |  |

| [x,x,6] |     |                       | p/n, <mark>n/p:n/p</mark> ,p/n               | Flip across Pol. and I,Q      |  |

| [x,x,7] |     |                       | n/p,p/n:p/n,n/p                              |                               |  |

Table 3-3 Allowable channel mappings for the µICR high speed electrical interface.

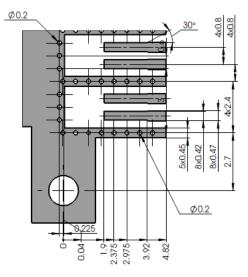

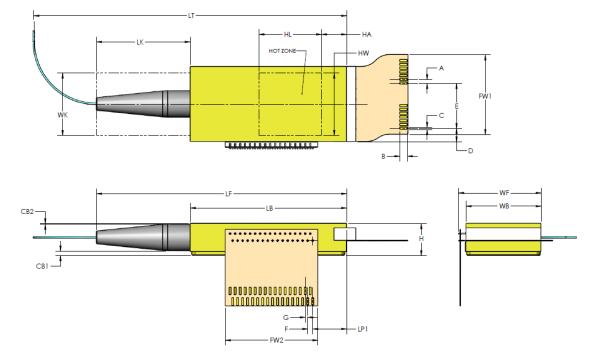

## 3.2 High Speed Electrical Interface in the Type 2 Mechanical Form Factor

The high speed electrical interface for the Type 2 form factor is realized using an RF flexible PCB. This allows for a customized RF connection between a vendor-specific interface on the  $\mu$ ICR package and a customer-specific interface on the host PCB.

Figure 3-2 High speed flexible PCB interface for the Type 2 mechanical form factor enabling adaption to the CFP2-ACO module environment.

In one key example, the customer interface for the flexible PCB matches the pitch of a CFP2 connector as shown in Figure 3-2. Numerical values for the dimensions in Figure 3-2 are given in Table 7-2 and Table 7-3.

# 4 Low Speed Electrical Interface

#### 4.1 Low Speed Electrical Interface in the Type 1 Mechanical Form Factor

The low speed electrical connections for the Type 1 form factor are provided through 34 pins, located on both sides of the package, and numbered as shown in Table 4-1. Note that unused pins on the interface are not required to be present.

The pin pitch shall be nominally 0.8 mm.

The low speed electrical interface pin functionality is specified in Table 4-1. Note that an equally valid alternative low speed interface pin definition implemented using an SPI bus is detailed in Section 8.

The photocurrent of each channel, or a representative equivalent quantity, shall be measurable.

| Pin# | Symbol  | Description                                   | Pin# | Symbol | Description                                 |

|------|---------|-----------------------------------------------|------|--------|---------------------------------------------|

| 1    | RFU     | Reserved for future use <sup>4</sup>          | 34   | RFU    | Reserved for future use <sup>4</sup>        |

| 2    | RFU     | Reserved for future use <sup>4</sup>          | 33   | RFU    | Reserved for future use <sup>4</sup>        |

| 3    | MGC/AGC | MGC/AGC selection (optional)                  | 32   | SD     | Shutdown (optional)                         |

| 4    | MPD-C   | Monitor diode cathode (optional) <sup>3</sup> | 31   | VOA1   | VOA1 Adjust voltage (optional) <sup>2</sup> |

| 5    | MPD-A   | Monitor diode anode (optional) <sup>3</sup>   | 30   | VOA2   | VOA2 Adjust voltage (optional) <sup>2</sup> |

| 6    | PD-YI   | Photodiode bias voltage YI <sup>1</sup>       | 29   | PD-XQ  | Photodiode bias voltage XQ <sup>1</sup>     |

| 7    | PD-YI   | Photodiode bias voltage YI <sup>1</sup>       | 28   | PD-XQ  | Photodiode bias voltage XQ <sup>1</sup>     |

| 8    | PD-YQ   | Photodiode bias voltage YQ <sup>1</sup>       | 27   | PD-XI  | Photodiode bias voltage XI <sup>1</sup>     |

| 9    | PD-YQ   | Photodiode bias voltage YQ <sup>1</sup>       | 26   | PD-XI  | Photodiode bias voltage XI <sup>1</sup>     |

| 10   | PI-YI   | Peak indicator YI                             | 25   | PI-XQ  | Peak indicator XQ                           |

| 11   | GA-YI   | Gain adjust YI                                | 24   | GA-XQ  | Gain adjust XQ                              |

| 12   | OA-YI   | Output amplitude adjust YI                    | 23   | OA-XQ  | Output amplitude adjust XQ                  |

| 13   | VCC-Y   | Supply voltage amplifier Y                    | 22   | VCC-X  | Supply voltage amplifier X                  |

| 14   | GND     | Ground Reference                              | 21   | GND    | Ground Reference                            |

| 15   | OA-YQ   | Output amplitude adjust YQ                    | 20   | OA-XI  | Output amplitude adjust XI                  |

| 16   | GA-YQ   | Gain adjust YQ                                | 19   | GA-XI  | Gain adjust XI                              |

| 17   | PI-YQ   | Peak Indicator YQ                             | 18   | PI-XI  | Peak Indicator XI                           |

Table 4-1 Low speed electrical interface definition.

Notes:

- 1. PD-YI, PD-YQ, PD-XI, PD-XQ are each assigned two pins where either:

- a. Each one of the two pins independently supplies the bias voltage for one of the two differential photodiodes in the labeled Polarization / Phase channel; or

- b. The first of the two pins (6, 8, 27, 29) is connected to both of the differential photodiodes for the labeled Polarization / Phase channel and the other pin (7, 9, 26, 28) is not connected within the  $\mu$ ICR.

- 2. Pins 31 and 30 (VOA1 and VOA2) shall not be connected internally to ground. If separate VOA functions in the X- and Y-polarization channels are implemented, then the X channel shall be controlled by pin 31 (VOA1) and the Y channel shall be controlled by pin 30 (VOA2); both then being referenced to GND.

- 3. If independent monitor PDs are provided for the X- and Y-polarizations, the cathode of the X-polarization MPD shall be connected to pin 4 (MPD-C); the anode of the X-polarization MPD shall be connected to pin 5 (MPD-A); the cathode of the Y-polarization MPD shall be connected to pin 4 (MPD-C); and the anode of the Y-polarization MPD

shall be connected to GND. Internal circuitry providing equivalent functionality is acceptable.

4. Bandwidth Adjust controls – if available – should be present on pins 1, 2, 33, and 34 (marked as Reserved for Future Use). If only two pins are used for bandwidth control, the preference is to use pins 2 and 33.

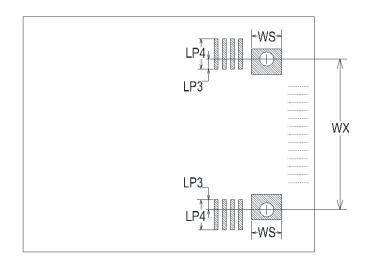

#### 4.2 Low Speed Electrical Interface in the Type 2 Mechanical Form Factor

The low speed interface for the Type 2 form factor is provided by a 34 pad flexible PCB connected to one side of the package body. The package interface is vendor-specific. The 34 pads on the host PCB are arranged in two rows of 17 pads as illustrated in Figure 4-1. Dimensional detail is provided in Figure 7-4 and Figure 7-5.

Figure 4-1 Low speed electrical interface in the Type 2 form factor.

The low speed electrical interface pin functionality is identical to the Type 1 implementation as specified in Table 4-1. Note that an equally valid alternative low speed interface pin definition implemented using an SPI bus is detailed in Section 8.

## 5 <u>Environmental and Operating Characteristics</u>

| Parameter                      |            | Unit | Min    | Тур | Max    | Note |

|--------------------------------|------------|------|--------|-----|--------|------|

| Operating fragmonat            | C-band     | THz  | 191.35 |     | 196.20 | 1    |

| Operating frequency            | L-band     | IIIZ | 186.00 |     | 191.50 | L    |

| TIA supply voltage             |            | V    | 3.14   | 3.3 | 3.47   |      |

| Photodiode bias voltage        | Option 3.3 | V    | 3.135  | 3.3 | 3.465  | 2    |

| Thorothoue bias voltage        | Option 5.0 | v    | 4.75   | 5.0 | 5.25   |      |

| Monitor photodiode bias        | Option 3.3 | V    | 3.135  | 3.3 | 3.465  | 2    |

| voltage                        | Option 5.0 | v    | 4.75   | 5.0 | 5.25   | 2    |

| VOA control voltage (optional) |            | V    | 0      |     | 9      | 3    |

| Operating temperature          | Standard   | ംറ   | -5     |     | 75     | 4    |

| Operating temperature          | Preferred  |      | -5     |     | 80     | 4    |

| Operating humidity (non-con    | densing)   | %RH  | 5      |     | 85     |      |

Basic operating characteristics are listed in Table 5-1.

Table 5-1 Operating characteristics.

Notes:

- 1. Minimum supported range. At least one of the two frequency bands shall be supported.

- 2. Vendor shall state which Bias Voltage Option or Options are allowed, both for Signal Photodiodes and Monitor Photodiodes.

- 3. The VOA shall be of type "normally bright".

- 4. The operating temperature is defined as the minimum/maximum of the  $\mu$ ICR case "hot zone" surface temperature.

# 6 <u>Electro-Optical Characteristics (Normative)</u>

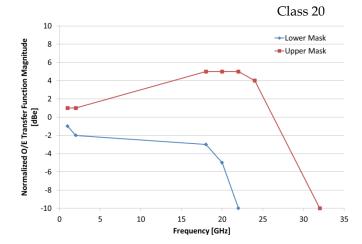

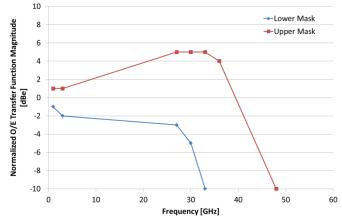

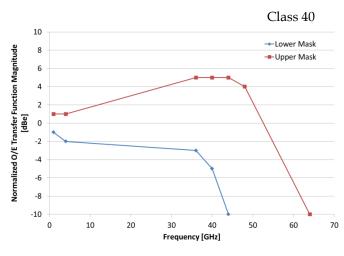

In this revision of the IA, electro-optical (EO) characteristics are provided for 3 Classes of  $\mu$ ICR (Class 20, 30 and 40), corresponding to devices having notional S<sub>21</sub> bandwidths of 20GHz, 30GHz, and 40GHz, respectively.

General EO characteristics common to all 3 Classes of  $\mu$ ICR are given in Section 6.1. The RF frequency response specifications specific to each Class of  $\mu$ ICR are given in Section 6.2. Other *Informative* EO characteristics for  $\mu$ ICRs are given in Appendix 11.

Revision 1.0 of the  $\mu$ ICR IA contained only *informative* EO specifications for a device with a notional 20GHz S<sub>21</sub> bandwidth. Implementations of a  $\mu$ ICR conforming to revision 1.0 and so identified, but not meeting all of the requirements presented herein, are still considered valid  $\mu$ ICR implementations.

| Parameter                                                         | Unit       | Min  | Тур  | Max | Note |     |

|-------------------------------------------------------------------|------------|------|------|-----|------|-----|

| Operating signal power                                            |            | dBm  | -18  | -10 | 0    |     |

| Local oscillator power                                            |            | dBm  |      |     | 16   | 1   |

| Maximum differential output                                       | swing      | mVpp | 700  |     |      | 2   |

| Minimum differential output                                       | swing      | mVpp |      |     | 300  | 2   |

| DC common mode rejection                                          | Sig to I&Q | dBe  |      |     | -20  | 3   |

| ratio (CMRR <sub>DC</sub> )                                       | LO to I&Q  | ube  |      |     | -16  | 5   |

| RF common mode rejection                                          | Sig to I&Q | dBe  |      |     | -16  | 3,4 |

| ratio (CMRR <sub>RF</sub> )                                       | LO to I&Q  | ube  |      |     | -14  | 5,4 |

| Low frequency cut-off                                             |            | MHz  |      |     | 1    | 5   |

| Phase error                                                       |            | 0    | -7.5 |     | +7.5 | 6   |

| Optical reflectance                                               |            | dB   |      |     | -27  | 7   |

| Skew between complimentary signals within a channel (informative) |            | ps   |      |     | 1    |     |

| Channel skew                                                      |            | ps   |      |     | 50   | 8   |

| X/Y skew variation                                                |            | ps   |      |     | 3.0  | 9   |

|                                                                   | Class 20   |      |      |     | 2.0  |     |

| I/Q skew variation                                                | Class 30   | ps   |      |     | 1.5  | 10  |

|                                                                   | Class 40   |      |      |     | 1.0  |     |

## 6.1 General Electro-Optical Characteristics

#### Table 6-1 Electro-optic characteristics (normative).

Notes:

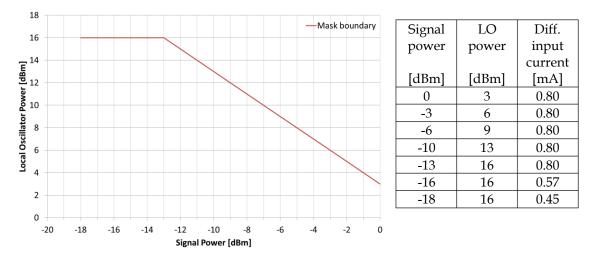

1. At high signal powers, the maximum desired local oscillator power is limited by the maximum TIA differential input current for linear operation. Figure 6-1 provides an informative example calculation for the allowed LO power as a function of the input Signal. In implementations with a VOA in the Signal path, the Signal power can be attenuated such that no adjustment to the LO power is required.

- 2. Peak to peak, differential, AC coupled output amplitude that can be achieved by controlling the output adjust (OA) in AGC mode, given sufficiently strong input Signal and LO powers.

- 3. CMRR =  $20 \cdot \log(|\Delta I| / \sum I)$ , where  $\Delta I$  is the difference in photocurrent between the PDs in a differential pair (XI, XQ, YI, or YQ) and  $\sum I$  is the sum of the photocurrents from the PDs in the same PD pair. Note CMRR may not be directly measureable by the customer if no individual PD (p,n) bias pins are available on the low speed electrical interface.

- 4. RF CMRR is measured at 20GHz, 30GHz, and 40GHz for Class 20, 30, and 40 μICRs, respectively. The single-port rejection ratio (SPRR) measurement technique can be used to provide a suitable representation of the RF CMRR. The limits for Class 30 and 40 μICRs may be revised in a future revision of the document as more component and system level performance data becomes available.

- 5. AC coupled.

- 6. Between XI and XQ and between YI and YQ.

- 7. Signal and LO ports. Per ITU-T G.959.1

- 8. Time difference between earliest and latest channel (XI, XQ, YI, YQ). Includes X/Y and I/Q skew variation.

- 9. Variation in the skew between X and Y over case temperature, wavelength, input optical power, amplifier gain, and aging. The time for a polarization is defined as the average of I and Q, and the time for an individual I or Q channel is the average of p and n.

- 10. Variation in the skew between XI and XQ or between YI and YQ over case temperature, wavelength, input optical power, amplifier gain, and aging. The time for an individual I or Q channel is the average of p and n. It is noted that the measurement accuracy of currently available skew measurement techniques may not be sufficient to confirm compliance to limits below 2.0ps.

The TIA differential input current [mA] is calculated as:

$$I_{diff,pp} = 8 \sqrt{R_{SIG} \cdot R_{LO} \cdot 10^{(P_{SIG,S} + P_{LO})/10}}$$

where  $R_{SIG}$  and  $R_{LO}$  are the Signal and LO PD responsivities [A/W],  $P_{SIG,S}$  is the Signal power [dBm] in a single polarization (S = X or Y), and  $P_{LO}$  is the local oscillator power [dBm]. Assuming a Signal responsivity of 0.10 A/W and an LO responsivity of 0.05 A/W, as well as a 0.80 mA peak to peak differential linear input dynamic range, then a mask for the maximum LO power as a function of Signal power can be calculated as shown in Figure 6-1.

Figure 6-1 Informative example: recommended maximum LO power as a function of Signal power for a  $\mu$ ICR with  $R_{SIG} = 0.10$  A/W,  $R_{LO} = 0.05$  A/W, and peak-to-peak differential linear input dynamic range of 0.80 mA.

#### 6.2 **RF Frequency Response**

#### 6.2.1 Measurement Methods

The  $\mu$ ICR optical-to-electrical S<sub>21</sub> transfer function and S<sub>22</sub> electrical return loss frequency responses shall be measured *differentially* to evaluate conformance to the RF masks in Section 6.2.2 and Section 6.2.3. For these measurements the  $\mu$ ICR shall be *soldered* to the measurement test fixture, and the collected data shall be de-embedded to the *RF reference point*. The *RF reference point* is defined as the point on the Host PCB RF traces that is 2.5mm beyond the maximum extent of the  $\mu$ ICR RF lead pad (for the Type 1 form factor), or 2.5mm beyond the maximum extent of the solder pad for the RF flexible PCB (for the Type 2 form factor).

The masks below show a *target* range for the optical-to-electrical  $S_{21}$  transfer function and  $S_{22}$  electrical return loss frequency responses, allowing for component to component variations. These masks may be revised in a future revision of the document as more component and system level performance data becomes available.

#### 6.2.2 O/E S<sub>21</sub> Transfer Function Masks

The ideal RF frequency response for the receiver chain of a coherent modem – consisting of the ICR, the differential signal traces between the ICR and the DSP ASIC, and the ADCs at the input of the ASIC – is a low pass response which is flat up to the targeted signal bandwidth and rolls off steeply beyond that. Given that the losses of the signal traces between the ICR and the DSP ASIC increase gradually with frequency, it is generally preferred to have the RF frequency response of the ICR to increase gradually with frequency up to the targeted signal bandwidth, and then roll off steeply.

The  $S_{21}$  transfer functions shall be measured at a TIA gain condition and  $\mu$ ICR temperature that is agreed with the customer. All  $S_{21}$  responses shall be normalized to the response at 1GHz. It is assumed that any TIA functionality that manipulates the  $S_{21}$  transfer function (i.e. bandwidth adjust functions) can be utilized to obtain compliance with the masks provided in this section.

| Frequency<br>[GHz] | Lower Mask<br>[dBe] | Upper Mask<br>[dBe] |

|--------------------|---------------------|---------------------|

| 1                  | -1                  | 1                   |

| 2                  | -2                  | 1                   |

| 18                 | -3                  | 5                   |

| 20                 | -5                  | 5                   |

| 22                 | -10                 | 5                   |

| 24                 |                     | 4                   |

| 32                 |                     | -10                 |

| Frequency<br>[GHz] | Lower Mask<br>[dBe] | Upper Mask<br>[dBe] |

|--------------------|---------------------|---------------------|

| 1                  | -1                  | 1                   |

| 3                  | -2                  | 1                   |

| 27                 | -3                  | 5                   |

| 30                 | -5                  | 5                   |

| 33                 | -10                 | 5                   |

| 36                 |                     | 4                   |

| 48                 |                     | -10                 |

| Frequency<br>[GHz] | Lower Mask<br>[dBe] | Upper Mask<br>[dBe] |

|--------------------|---------------------|---------------------|

| 1                  | -1                  | 1                   |

| 4                  | -2                  | 1                   |

| 36                 | -3                  | 5                   |

| 40                 | -5                  | 5                   |

| 44                 | -10                 | 5                   |

| 48                 |                     | 4                   |

| 64                 |                     | -10                 |

Figure 6-2 Normalized O/E  $S_{21}$  transfer function masks for the class 20, 30, and 40  $\mu ICR$  respectively.

#### 6.2.3 Electrical Return Loss Masks

| Frequency | Upper Mask |

|-----------|------------|

| [GHz]     | [dBe]      |

| 1         | -10        |

| 16        | -10        |

| 16        | -8         |

| 24        | -8         |

| 24        | -6         |

| 32        | -6         |

| Frequency | Upper Mask |

|-----------|------------|

| [GHz]     | [dBe]      |

| 1         | -10        |

| 24        | -10        |

| 24        | -8         |

| 36        | -8         |

| 36        | -6         |

| 48        | -6         |

| Frequency<br>[GHz] | Upper Mask<br>[dBe] |

|--------------------|---------------------|

| 1                  | -10                 |

| 32                 | -10                 |

| 32                 | -8                  |

| 48                 | -8                  |

| 48                 | -6                  |

| 64                 | -6                  |

# 7 <u>Mechanical</u>

#### 7.1 General Overview and Fiber Types

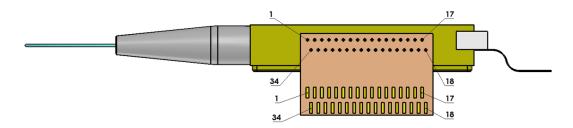

Both a primary and alternative electro-mechanical form factor are defined in this revision of the  $\mu$ ICR IA. For both form factors the fiber inputs and the RF electrical outputs are located on opposite ends of the package.

Parameter Unit Min Typ Max Note "Minimum bend radius" specification for 7.5 mm 1, 2, 3 PMF on Local Oscillator input PM fiber bend loss for 10 turns at 7.5mm dB 1 6 bend radius "Minimum bend radius" Option 1 5.0 3,4 specification for SMF on Signal mm Option 2 7.5 3,5 input SM fiber bend loss for 10 turns at 5.0mm (Option 1) or 7.5mm (Option 2) bend 1 dB 6 radius Fiber cladding diameter 125 μm Fiber coating diameter 250 μm

The input optical fiber types shall be as defined in Table 7-1.

#### Table 7-1 Input fiber characteristics.

#### Notes:

- 1. The polarization state in the PM fiber shall be aligned to the slow axis of the PM fiber.

- 2. The slow axis of the PM fiber shall be aligned to the connector key.

- 3. The PMF color shall be natural (transparent) and the SMF color shall be white (not natural or transparent).

- 4. The Option 1 SMF shall be compliant to ITU-T Recommendations G.657.B3 and G.652.D.

- 5. The Option 2 SMF shall be compliant to ITU-T Recommendations G.657.B2 and G.652.D.

- 6. μICR responsivity shall be measured with straight fibers and shall not include bend loss.

#### 7.2 Type 1 Mechanical Form Factor

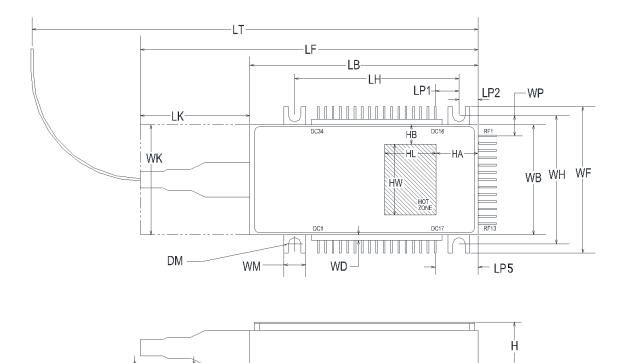

The primary electro-mechanical form factor (Type 1) uses a surface mount configuration with the low speed electrical interface signals applied from both the left and right sides of the package. The Type 1 mechanical drawing is shown in Figure 7-1 and the dimensions are provided in Table 7-2. Note that the mounting flanges in Figure 7-1 are optional and un-used DC pins are not required to be present. The Host PCB DC control pin landing pad locations are given in Figure 7-2. Note also the thermal transfer path for a Type 1 µICR shall be from the *Hot-Zone* defined in Figure 7-1 into the Host PCB.

CB-

HM

Figure 7-1 Mechanical drawing for Type 1 form factor.

Figure 7-2 Host PCB landing pad locations for low speed pins – Type 1 form factor.

Defined for Megtron 7 R-5785 E-glass thickness: 0.3mm, metallization thickness: 27µm

Figure 7-3 Informative host PCB landing pad dimensions for high speed pins – Type 1 form factor.

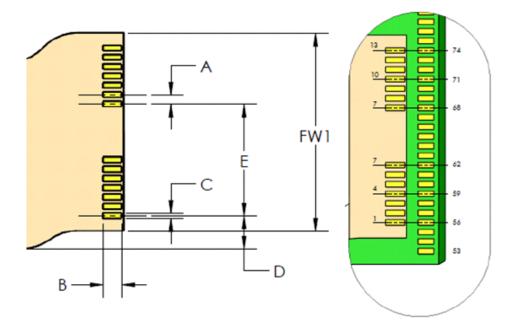

#### 7.3 Type 2 Mechanical Form Factor

The alternative electro-mechanical form factor (Type 2) employs flexible PCBs for both the RF and single-sided low speed electrical I/O interfaces. The Type 2 mechanical drawing is shown in Figure 7-4 and the dimensions are provided in Table 7-2. The use of flexible PCB in Type 2 allows for a customizable RF connection between a vendor-specific interface on the package and a customer-specific interface on the host PCB. This can provide routing, pitch adjustment and path equalization as needed. One possible adaptation of the low speed and RF interfaces to the CFP2-ACO module environment is illustrated in Figure 7-5 and Figure 7-6, with dimensions related to the mounting given in Table 7-2 and Table 7-3. Note the Type 2 form factor can allow for the direct connection of the  $\mu$ ICR *Hot Zone* to the heat sinking surface, for example in the use-case of a pluggable coherent module.

Figure 7-4 Mechanical drawing for Type 2 form factor.

Figure 7-5 Possible adaptation of the Type 2 form factor low speed and RF interfaces to the CFP2-ACO module environment.

Figure 7-6 Possible adaptation of the Type 2 form factor to the CFP2-ACO module environment – RF interface detail.

## 7.4 Type 1 and Type 2 Mechanical Form Factor Dimensions

Mechanical dimensions for the Type 1 and Type 2 form factors are combined together in Table 7-2. Table 7-3 provides possible dimensions for the adaptation of the Type 2 form factor low speed and RF interfaces to the CFP2-ACO module environment.

| 0   |                                                                                                                         | Тур | e 1 Dimen                    | sions | Туре | e 2 Dimen | sions | NT (             |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|-------|------|-----------|-------|------------------|

| Sym | Description                                                                                                             | Min | Nom                          | Max   | Min  | Nom       | Max   | Notes            |

| Н   | Package height                                                                                                          |     |                              | 6.0   |      |           | 6.0   |                  |

| LT  | Total length including 90 degree fiber bends                                                                            |     |                              | 58    |      |           | 55    |                  |

| LF  | Full length of package including fiber boots                                                                            |     |                              | 43    |      |           | 40    |                  |

| LB  | Length of package body                                                                                                  |     |                              | 27    | 21   |           | 25    |                  |

| LH  | Distance between mounting holes (optional)                                                                              |     | 18                           |       |      |           |       |                  |

| LP1 | Distance between mounting hole center and center of last DC pin (optional)                                              |     | 2.6                          |       |      | 5.4       |       |                  |

| LP2 | Distance between mounting hole center and RF end of package (optional)                                                  |     | 2.1                          |       | -    | -         | -     | Type 1           |

| LP3 | DC/Control pin PCB landing pad location relative to mounting hole center                                                |     | 1.0                          |       | -    | -         | -     | Type 1<br>Note 2 |

| LP4 | DC/Control pin PCB landing pad length                                                                                   |     | 3.0                          |       | -    | -         | -     | Type 1           |

| LP5 | Distance between center of last DC pin and the RF end of package                                                        |     | 4.7                          |       |      |           |       |                  |

| WF  | Width of package including mounting<br>flanges and DC pins                                                              |     |                              | 16    |      | 13.5      |       |                  |

| WH  | Distance between mounting foot cutout centers (optional)                                                                |     | 14                           |       | -    | -         | -     | Type 1           |

| WB  | Width of package body                                                                                                   |     | 12                           |       |      | 12        |       |                  |

| WP  | Distance between mounting foot cutout<br>center and first RF pin center (optional). RF<br>pins are centered in package. |     | 2.2                          |       | -    | -         | -     | Type 1<br>only   |

| HA  | Location of hot region relative to package end                                                                          | 3   |                              | 5     | 3    |           | 5     |                  |

| HB  | Location of hot region relative to package edge                                                                         | HW  | HW to be centered in package |       |      |           |       |                  |

| HW  | Width of hot region                                                                                                     |     |                              | WB    |      |           | WB    | Center           |

| Course | Description                                                  | Туре | e 1 Dimen   | sions | Туре | 2 Dimens    | sions | Natas            |

|--------|--------------------------------------------------------------|------|-------------|-------|------|-------------|-------|------------------|

| Sym    | Description                                                  | Min  | Nom         | Max   | Min  | Nom         | Max   | Notes            |

| HL     | Length of hot region                                         |      |             | 10    |      |             | 10    |                  |

| WK     | Width of boot area keep-out region                           |      |             | WB    |      |             | 10    | Type 2<br>Center |

| LK     | Length of boot area keep-out region                          | (r   | nax LF) - I | LB    | (n   | nax LF) - I | LB    | Max              |

| WM     | Width of mounting flanges (optional)                         | 2    | 2.4         | 3     | -    | -           | -     | Type 1           |

| HM     | Height of mounting flanges (optional)                        |      | 0.3         | 0.4   | -    | -           | -     | Type 1<br>Note 1 |

| CB     | Clearance under fiber boots                                  | 0.25 |             |       | -    | -           | -     | Type 1           |

| CB1    | Clearance between boot and cold side                         | -    | -           | -     | 0.25 |             |       | Type 2           |

| CB2    | Clearance between boot and hot side                          | -    | -           | -     | 0.15 |             |       | Type 2           |

| DM     | Diameter of mounting holes (optional)                        | 1.35 | 1.4         | 1.45  | -    | -           | -     |                  |

| WS     | Width of mounting foot PCB pad                               |      | 3.0         |       |      |             |       |                  |

| WD     | Edge of DC feed-through ceramics to edge of<br>package frame | 0    |             | 0.6   | -    | -           | -     |                  |

| WX     | Distance between PCB mounting hole center                    |      | 15          |       |      |             |       | Type 1           |

Table 7-2

Type 1 and Type 2 mechanical form factor dimensions (in mm).

#### Notes:

- 1. Optional mounting flanges can be either screw-down or solder type.

- 2. LP3 is offset towards the package body. Refer to Figure 7-2.

| <b>C</b> | Demonstration                                            | I   | Dimensio | n    |

|----------|----------------------------------------------------------|-----|----------|------|

| Sym      | Parameter                                                | Min | Nom      | Max  |

| А        | Pad pitch                                                |     | 0.8      |      |

| В        | Pad length (Contact length between flex pad and PCB pad) | 1.0 | 1.2      | 1.5  |

| С        | Pad width                                                |     | 0.35     |      |

| D        | Pad offset to package                                    |     | 2.13     |      |

| Е        | Pad offset pitch                                         |     | 7.2      |      |

| F        | DC Pad pitch                                             |     | 0.8      |      |

| FL1      | RF flex length formed state                              |     | 8.6      |      |

| FW1      | RF flex width on PCB                                     |     |          | 12.8 |

| G        | DC Pad row pitch offset                                  |     | 0.4      |      |

| J        | PCB Pad width                                            |     | 0.42     |      |

| K        | PCB Pad length                                           |     | 1.42     |      |

| L        | PCB DC pad width                                         |     | 0.42     |      |

| М        | PCB DC pad length                                        |     | 1.40     |      |

Table 7-3 Possible dimensions for the adaptation of the Type 2 form factor low speed and RFinterfaces to the CFP2-ACO module environment.

# 8 <u>Low Speed Electrical Interface Implemented using SPI</u> <u>Control</u>

An alternative implementation for the  $\mu$ ICR low speed electrical interface that uses SPI control is detailed herein, including the base required registers and command set. The  $\mu$ ICR is defined as the *Client* or *Slave* in the SPI interface with the terms used interchangeably.

#### 8.1 SPI Enabled Low Speed Electrical Interface Pin Assignment

The SPI enabled low speed electrical interface pin assignments are provided in Table 8-1. Pins 1, 2, 33 and 34 enable SPI communications to the  $\mu$ ICR. The SPI Reset is present on pin 32, providing synergy with the optional RF output shutdown on pin 32 in the all analog low speed interface given in Table 4-1. RF output shutdown in the SPI enabled interface is implemented by SPI control.

Pin 3 is released for *Future Use* because the MGC/AGC selection is implemented by SPI control. Pins 11, 16, 19 and 24 are also released for *Future Use* because both Gain Adjust in MGC mode and Output Adjust in AGC mode are provided by a single set of reconfigurable Analog Adjust pins (A<sub>i</sub>) on pins 12, 23, 15, and 20.

The monitor  $(M_i)$  pins 10, 25, 17 and 18 shall at a minimum be capable of monitoring the output peak detect signal and the gain control monitor voltage; however, they may optionally support other vendor-specific analog monitoring functions.

| #  | Symbol   | Description                                         |  | #  | Symbol  | Description                                 |

|----|----------|-----------------------------------------------------|--|----|---------|---------------------------------------------|

| 1  | SPI-MOSI | Master output, Slave (Client) input                 |  | 34 | SPI-CLK | Serial clock                                |

| 2  | SPI-MISO | Master input, Slave (Client) output                 |  | 33 | SPI-CS  | Slave (Client) select                       |

| 3  | RFU      | Reserved for future use                             |  | 32 | SPI-RST | SPI reset                                   |

| 4  | MPD-C    | Monitor diode cathode (optional) <sup>3</sup>       |  | 31 | VOA1    | VOA1 Adjust voltage (optional) <sup>2</sup> |

| 5  | MPD-A    | Monitor diode anode (optional) <sup>3</sup>         |  | 30 | VOA2    | VOA2 Adjust voltage (optional) <sup>2</sup> |

| 6  | PD-YI    | Photodiode bias voltage YI <sup>1</sup>             |  | 29 | PD-XQ   | Photodiode bias voltage XQ <sup>1</sup>     |

| 7  | PD-YI    | Photodiode bias voltage YI <sup>1</sup>             |  | 28 | PD-XQ   | Photodiode bias voltage XQ <sup>1</sup>     |

| 8  | PD-YQ    | Photodiode bias voltage YQ <sup>1</sup>             |  | 27 | PD-XI   | Photodiode bias voltage XI <sup>1</sup>     |

| 9  | PD-YQ    | Photodiode bias voltage YQ <sup>1</sup>             |  | 26 | PD-XI   | Photodiode bias voltage XI <sup>1</sup>     |

| 10 | M2       | Analogue Monitor YI<br>[Output_PkD or Gain Monitor] |  | 25 | M1      | Analogue monitor XQ                         |

| 10 | 1012     |                                                     |  | 23 | 1011    | [Output_PkD or Gain Monitor]                |

| 11 | RFU      | Reserved for future use                             |  | 24 | RFU     | Reserved for future use                     |

| 12 | A2       | Analog output amplitude or gain                     |  | 23 | A1      | Analog output amplitude or gain             |

|    |          | adjust YI                                           |  |    |         | adjust XQ                                   |

| 13 | VCC-Y    | Supply voltage amplifier Y                          |  | 22 | VCC-X   | Supply voltage amplifier X                  |

| 14 | GND      | Ground Reference                                    |  | 21 | GND     | Ground Reference                            |

| 15 | A3       | Analog output amplitude or gain                     |  | 20 | A0      | Analog output amplitude or gain             |

| 15 | AJ       | adjust YQ                                           |  | 20 | AU      | adjust XI                                   |

| 16 | RFU      | Reserved for future use                             |  | 19 | RFU     | Reserved for future use                     |

| 17 | М3       | Analogue Monitor YQ                                 |  | 18 | M0      | Analogue Monitor XI                         |

| 17 | 141.5    | [Output_PkD or Gain Monitor]                        |  | 10 | 1410    | [Output_PkD or Gain Monitor]                |

#### Table 8-1 SPI enabled low speed electrical interface pin assignment.

#### Notes:

- 1. PD-YI, PD-YQ, PD-XI, PD-XQ are each assigned two pin where either:

- a. Each one of the two pins independently supplies the bias voltage for one of the two differential photodiodes in the labeled Polarization / Phase channel; or

- b. The first of the two pins (6, 8, 27, 29) is connected to both of the differential photodiodes for the labeled Polarization / Phase channel and the other pin (7, 9, 26, 28) is not connected within the  $\mu$ ICR.

- 2. Pins 31 and 30 (VOA1 and VOA2) shall not be connected internally to ground. If separate VOA functions in the X- and Y-polarization channels are implemented, then the X channel shall be controlled by pin 31 (VOA1) and the Y channel shall be controlled by pin 30 (VOA2); both then being referenced to GND.

- 3. If independent monitor PDs are provided for the X- and Y-polarizations, the cathode of the X-polarization MPD shall be connected to pin 4 (MPD-C); the anode of the X-polarization MPD shall be connected to pin 5 (MPD-A); the cathode of the Y-polarization MPD shall be connected to pin 4 (MPD-C); and the anode of the Y-polarization MPD shall be connected to GND. Internal circuitry providing equivalent functionality is acceptable.

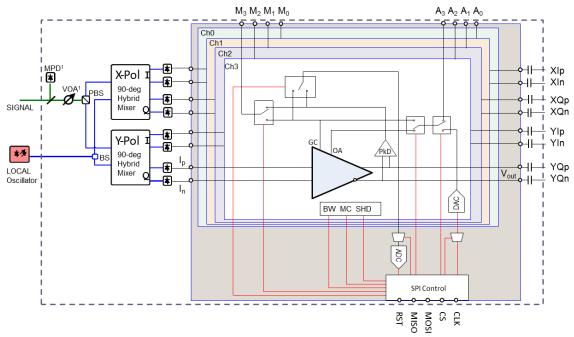

#### 8.2 Functional Diagram of µICR with SPI Interface

An example schematic functional diagram of a  $\mu$ ICR with SPI function is shown in Figure 8-1. The SPI control functions can either be implemented in the TIA or using a separate chip in combination with the TIAs. The output/monitor pin of a given channel is indicated as Mi and the control pin of the same channel is indicated as Ai, where i = 0 to 3 corresponding to XI, XQ, YI and YQ respectively.

The SPI interface allows the configuration of the Analogue Monitoring  $(M_i)$  and Analogue Adjust  $(A_i)$  pins depending on the desired monitoring / control mode, i.e. AGC or MGC mode in the case of input  $A_i$  pin, or at what point in the TIA is to be monitored by addressing the appropriate register as detailed in Section 8.7.

Figure 8-1 Schematic diagram of a µICR with SPI control.

#### Notes:

- 1. One configuration for the order of the VOA and MPD is shown. The configuration with the MPD followed by the VOA is an equally acceptable configuration. Configurations having VOA's and/or MPD's after the polarization beam splitter (one VOA/MPD per polarization) are also considered acceptable implementations.

- 2. The dash-line enclosed area represents the µICR outline.

- 3. M<sub>i</sub> are the analogue monitor pins.

- 4. A<sub>i</sub> are the analogue adjust pins.

#### 8.3 SPI Interface Voltage and Control Specifications

The SPI used is a full duplex high speed synchronous serial interface originally defined by Motorola. The key voltage and control specifications are summarized in Table 8-2.

| Parameter                     | Conditions      | I Init | Va                          | lue          |  |

|-------------------------------|-----------------|--------|-----------------------------|--------------|--|

| rarameter                     | Conditions      | Unit   | min                         | max          |  |

| CPI control voltago           | Logical 0       | V      |                             | 0.8          |  |

| SPI control voltage           | Logical 1       |        | 2                           |              |  |

| IO Standard                   | LVCMOS          | V      | 3                           | 3.6          |  |

| CLK cycle time                |                 | ns     | 50                          | 1000         |  |

| CLK frequency <sup>1</sup>    |                 | MHz    | 1                           | 20           |  |

| Time delay between asserting  |                 | 20     | 25                          |              |  |

| CSN and toggling CLK          |                 | ns     | 25                          |              |  |

| Data register width           | Address+Op-code | 1      | 16                          |              |  |

| Data register width           | Data block      | bit    | 1                           | 6            |  |

| Data register shift direction |                 |        | MSB                         | first        |  |

| Clock polarity                |                 |        | Idle state for              | CLK is low   |  |

|                               |                 |        | Data is late                | hed on the   |  |

| Clock phases                  |                 |        | leading edge                | of CLK, data |  |

|                               |                 |        | changes on the trailing edg |              |  |

| Client select state for data  |                 |        | Chip sele                   | ct low for   |  |

| transmission                  |                 |        | read/write                  | commands     |  |

| Client reset (via Reset pin)  |                 |        | Activ                       | e low        |  |

#### Table 8-2 SPI voltage and control specification.

Notes:

1. SPI control can be operated by any specific frequency within the Min/Max range.

#### 8.4 SPI Read / Write Datagram

Below is the data structure of the SPI command datagram.

|          |         | Register Address                                                     |         |         |         |        |         |         |        |        |        | O<br>co | •  | Data Block |        |   |   |         |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |

|----------|---------|----------------------------------------------------------------------|---------|---------|---------|--------|---------|---------|--------|--------|--------|---------|----|------------|--------|---|---|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Bit#     | 31      | 30                                                                   | 29      | 28      | 27      | 26     | 25      | 24      | 23     | 22     | 21     | 20      | 19 | 18         | 17     | 1 | 6 | 15      | 14      | 13      | 12      | 11      | 10      | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| Name     | A<br>14 |                                                                      | A<br>12 | A<br>11 | A<br>10 | A<br>9 | A<br>8  | A<br>7  | A<br>6 | A<br>5 | A<br>4 | A<br>3  |    | A<br>1     | A<br>0 | R | W | D<br>15 | D<br>14 | D<br>13 | D<br>12 | D<br>11 | D<br>10 | D<br>9 | D<br>8 | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 |

| Function |         | reserved $\begin{array}{c c} X/I/\\ Y Q \end{array}$ Select register |         |         |         |        |         |         | R      | W      | 7 Data |         |    |            |        |   |   |         |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |

| value    |         |                                                                      |         |         |         |        | 0/<br>1 | 0/<br>1 |        |        |        |         |    |            |        | 1 | 0 |         |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |

Table 8-3 SPI data telegram structure.

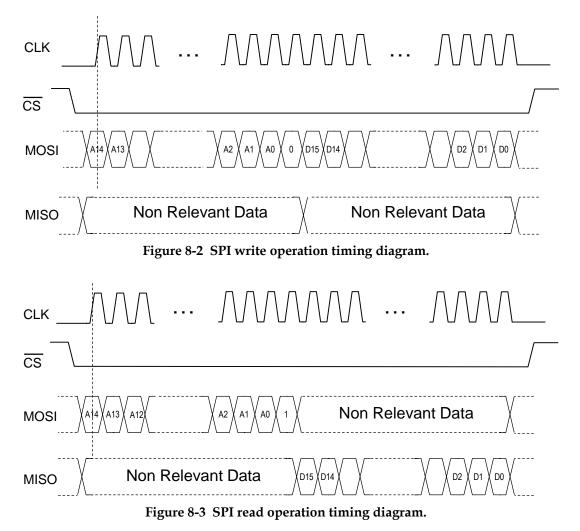

#### 8.5 SPI Read / Write Operation Timing Diagrams

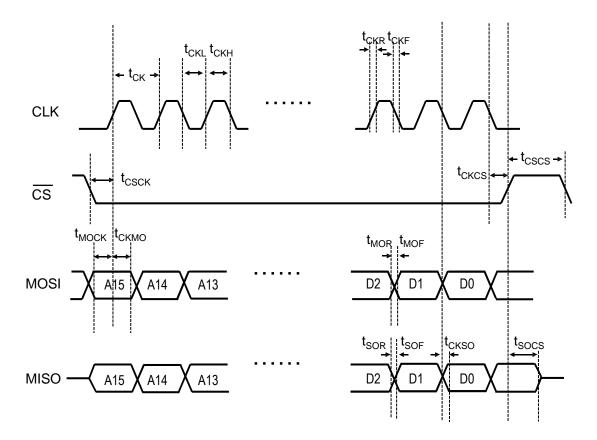

Figure 8-2 and Figure 8-3 detail the SPI write operation timing and the SPI read timing operation.

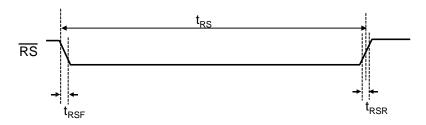

## 8.6 SPI Timing Specifications

The SPI timing specifications are summarized in Table 8-4 and illustrated in Figure 8-4 and Figure 8-5. The SPI client hardware reset is defined as asynchronous. After the reset, the TIA configuration should be returned to its default, with all outputs shutdown.

| Description                           | Condition                  | Countral          | Theit | Value             |      |  |  |

|---------------------------------------|----------------------------|-------------------|-------|-------------------|------|--|--|

| Description                           | Condition                  | Symbol            | Unit  | min.              | max. |  |  |

| CLK clock frequency                   |                            |                   | MHz   | 1                 | 20   |  |  |

| CLK clock period                      |                            | tcк               | ns    | 50                | 1000 |  |  |

| CLK peak-peak jitter                  |                            |                   | ps    |                   | 500  |  |  |

| CLK high time                         |                            | t <sub>CKH</sub>  | ns    | 20                | 550  |  |  |

| CLK low time                          |                            | t <sub>CKL</sub>  | ns    | 20                | 550  |  |  |

| CLK 10%-90% rise time                 | 15 - 18 pF capacitive load | t <sub>CKR</sub>  | ns    | 0.5               | 5    |  |  |

| CLK 10%-90% fall time                 |                            | tckf              | ns    | 0.5               | 5    |  |  |

| CSN to SPI CLK↑ setup time            |                            | tcsck             | ns    | 50                | 1000 |  |  |

| $CLK \downarrow$ to SPI CSN hold time |                            | tckcs             | ns    | 50                | 1000 |  |  |

| CLK ↓to SPI MISO valid time           | 15 - 18 pF capacitive load | t <sub>CKSO</sub> | ns    | 2                 | 11   |  |  |

| MISO 10%-90% rise time                | 15 - 18 pF capacitive load | tsor              | ns    | 0.5               | 5    |  |  |

| MISO 10%-90% fall time                |                            | tsof              | ns    | 0.5               | 5    |  |  |

| MOSI to SPI CLK↑ edge setup time      |                            | t <sub>MOCK</sub> | ns    | 8                 |      |  |  |

| MOSI to SPI CLK↑ edge hold time       |                            | tскмо             | ns    | 8                 |      |  |  |

| MOSI 10%-90% rise time                |                            | t <sub>MOR</sub>  | ns    | 0.5               | 5    |  |  |

| MOSI 10%-90% fall time                |                            | t <sub>MOF</sub>  | ns    | 0.5               | 5    |  |  |

| Min. SPI access inactive time         |                            | t <sub>CSCS</sub> | ns    | 5*t <sub>CK</sub> |      |  |  |

| RSN time                              |                            | t <sub>RS</sub>   | ns    | tск               |      |  |  |

| RSN10%-90% rise time                  | 15 - 18 pF capacitive load | t <sub>RSR</sub>  | ns    | 0.5               | 5    |  |  |

| RSN10%-90% fall time                  |                            | t <sub>RSF</sub>  | ns    | 0.5               | 5    |  |  |

Table 8-4 SPI read/write timing specifications.

Figure 8-4 SPI client read/write timing.

Figure 8-5 SPI client reset timing – asynchronous.

## 8.7 SPI Registers Specification

For each channel of the device, 32 16-bit registers are designated.

| Channel ID | Function | First address | Last address |

|------------|----------|---------------|--------------|

| 0          | XI       | N=0x0000      | 0x001F       |

| 1          | XQ       | N=0x0080      | 0x009F       |

| 2          | YI       | N=0x0100      | 0x011F       |

| 3          | YQ       | N=0x0180      | 0x019F       |

| Table 8-5 | General SPI | register | mapping. |

|-----------|-------------|----------|----------|

|-----------|-------------|----------|----------|

#### 8.7.1 General Information Registers

General Information Registers are accessible through Channel-0 only. These Registers contain TIA vendor and TIA part ID codes that provide unique identification for a specific SPI function implementation, thus enabling the user to map product specific parameters, performance, register locations, etc., for a given vendor's receiver. These register locations are defined by.

| Data             | Conditions      | Address | <bits></bits> | Default | Access <sup>1</sup> | Type | Notes          |

|------------------|-----------------|---------|---------------|---------|---------------------|------|----------------|

| TIA vendor<br>ID | Vendor USB code | 0x00    | <0:15>        |         | Ch0                 | RO   |                |

| RFU              | Reserved        | 0x01    | <0:15>        |         | Ch0                 | RO   |                |

| TIA part ID      | TIA ID          | 0x02    | <0:15>        |         | Ch0                 | RO   | Vendor defines |

| RFU              | Reserved        | 0x03    | <0:15>        |         | Ch0                 | RO   |                |

| Date or revision |                 | 0x04    | <0:15>        |         | Ch0                 | RO   | Vendor defines |