# **Integrable Tunable Laser Assembly MSA**

**OIF-ITLA-MSA-01.2**

June 26, 2008

Implementation Agreement created and approved by the Optical Internetworking Forum www.oiforum.com

The OIF is an international non profit organization with over 80 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements. With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with IEEE 802.1, IEEE 802.3ba, IETF, IP-MPLS Forum, IPv6 Forum, ITU-SG13, ITU-T SG15, MEF, ATIS-OPTXS, ATIS-TMOC, TMF and the XFP MSA Group.

For additional information contact:

The Optical Internetworking Forum, 48377 Fremont Blvd.,

Suite 117, Fremont, CA 94538

510-492-4040 (F) info@oiforum.com

www.oiforum.com

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

© 2001 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

# Table of Contents

| 1 | Table of Contents                                        | 3  |

|---|----------------------------------------------------------|----|

| 2 | List of Tables                                           |    |

| 3 | List of Figures                                          |    |

| 4 | Document Revision History                                |    |

| 5 | References and Conventions                               |    |

|   | 5.1 External Reference Documents                         |    |

|   | 5.2 Conventions Used in This Document                    |    |

| 6 | Introduction                                             |    |

|   | 6.1 Scope                                                |    |

|   | 6.2 Background                                           |    |

|   | 6.3 Communication Overview                               |    |

|   | 6.3.1 Physical Interfaces                                |    |

|   | 6.4 Command Overview                                     |    |

|   | 6.4.1 Command Execution Overlap                          |    |

|   | 6.4.2 Extended Addressing                                |    |

|   | 6.4.3 Data Types                                         |    |

|   | 6.4.3.1 Two Byte Data Values                             |    |

|   | 6.4.3.2 Multi-byte Fields                                |    |

|   | 6.4.4 Execution Error Field Conditions                   |    |

|   | 6.5 Command & Module Features                            |    |

|   | 6.5.1 Module Reset                                       |    |

|   | 6.5.2 Communication Error Detection                      |    |

|   | 6.5.2.1 Detection by Module                              |    |

|   | 6.5.2.2 Detection by Host                                |    |

|   | 6.5.3 Execution Error Detection                          |    |

|   | 6.5.4 Module Signaling Line                              |    |

|   | 6.5.5 Non-Volatile Default Configuration                 |    |

| 7 | Physical Layer & Electrical Characteristics              |    |

|   | 7.1 Assembly Electrical Interface                        |    |

|   | 7.1.1 Electrical Connector on User's Board               |    |

|   | 7.1.2 Pin Assignments                                    |    |

|   | 7.1.3 Electrical Characteristics                         |    |

|   | 7.2 Communication Interface                              | 24 |

| 8 | Transport Layer                                          |    |

| 0 | 8.1 Overview                                             |    |

|   | 8.2 Checksum                                             |    |

| 9 | Command Interface (Application Layer)                    |    |

| Э | 9.1 Command Format                                       |    |

|   | 9.1.1 In-Bound (Host to Module)                          |    |

|   | 9.1.2 Out-Bound (Module to Host)                         |    |

|   | 9.2 Register Summary                                     |    |

|   | 9.3 Command Description Format                           |    |

|   | 9.4 Generic Module Commands                              |    |

|   | 9.4.1 NOP/Status (NOP 0x00) [RW]                         |    |

|   | 9.4.2 Device Type (DevTyp 0x01) [R]                      |    |

|   | 9.4.3 Manufacturer (MFGR 0x02) [R]                       |    |

|   | 9.4.4 Model (Model 0x03) [R]                             |    |

|   | 9.4.5 Serial Number (SerNo 0x04) [R]                     | 39 |

|   | 9.4.6 Manufacturing Date (MFGDate0x05) [R]               | 40 |

|   | 9.4.7 Release (Release 0x06) [R]                         |    |

|   | 9.4.8 Release Backwards Compatibility (RelBack 0x07) [R] |    |

|   |                                                          |    |

|                          | dule Configuration (GenCfg 0x08) [RW]                |    |

|--------------------------|------------------------------------------------------|----|

| 9.4.10 IO Capabilit      | ies (IOCap 0x0D) [RW]                                | 45 |

|                          | ddressing Mode Registers (0x09-0x0B, 0x0E-0x10) [RW] |    |

|                          | ed Address Configuration (EAC 0x09 & 0x0E)           |    |

| 9.4.11.2 Extende         | ed Address (EA 0x0A & 0x0F)                          | 48 |

|                          | ed Address Access Register (EAR 0x0B & 0x10)         |    |

|                          | nse (LstResp 0x13) [R]                               |    |

|                          | configuration (DLConfig 0x14) [RW]                   |    |

|                          | tatus (DLStatus 0x15) [R]                            |    |

|                          | ommands                                              |    |

|                          | itusW (0x20, 0x21) [RW]                              |    |

|                          | shold (FPowTh, WPowTh 0x22, 0x23) [RW]               |    |

|                          | Threshold (FFreqTh, WFreqTh 0x24, 0x25) [RW]         |    |

|                          | reshold (FThermTh, WThermTh 0x26, 0x27) [RW]         |    |

|                          | ers (SRQT 0x28) [RW]                                 |    |

|                          | gers (FatalT 0x29) [RW]                              |    |

| 9.5.7 ALM Trigger        | rs (ALMT 0x2A) [RW]                                  | 63 |

| 9.6 Module Optical S     | Settings                                             | 64 |

| 9.6.1 Channel (Ch        | nannel 0x30) [RW]                                    | 64 |

|                          | er Set Point (PWR 0x31) [RW]                         |    |

| 9.6.3 Reset/Enab         | le (ResEna 0x32) [RW]                                | 67 |

| 9.6.4 Module Con         | figuration Behavior (MCB 0x33) [RW]                  | 69 |

| 9.6.5 Grid Spacing       | g (Grid 0x34) [RW]                                   | 70 |

| 9.6.6 First Channe       | el's Frequency (FCF1, FCF2 0x35 – 0x36) [RW]         | 71 |

| 9.6.7 Laser Frequ        | ency (LF1, LF2 0x40 - 0x41) [R]                      | 72 |

| 9.6.8 Optical Outp       | out Power (OOP 0x42) [R]                             | 73 |

| 9.6.9 Current Ten        | nperature (CTemp 0x43) [R]                           | 73 |

|                          | ilities                                              |    |

| 9.7.1 Fine Tune F        | requency Range (FTF 0x4F) [R]                        | 74 |

| 9.7.2 Optical Pow        | er Min/Max Set Points (OPSL, OPSH 0x50 - 0x51) [R]   | 75 |

| 9.7.3 Laser's First      | /Last Frequency (LFL1/2, LFH1/2 0x52-0x55) [R]       | 76 |

|                          | mum Grid Spacing (LGrid 0x56) [R]                    |    |

| 9.8 MSA Commands         | <b></b>                                              | 78 |

| 9.8.1 Module Curi        | rents (Currents 0x57) [R]                            | 78 |

| 9.8.2 Module Tem         | nperatures (Temps 0x58) [R]                          | 79 |

|                          | r (Dither(E,R,A,F) 0x59-0x5C) [RW] [Optional]        |    |

| 9.8.4 TBTF Warni         | ng Limits (TBTFL, TBTFH 0x5D, 0x5E) [RW]             | 82 |

| 9.8.5 Age Thresh         | old (FAgeTh, WAgeTh 0x5F, 0x60) [RW]                 | 83 |

| 9.8.6 Laser Age (A       | Age 0x61) [R]                                        | 84 |

| 9.8.7 Fine Tune F        | requency (FTF 0x62) [RW]                             | 85 |

| 9.9 Manufacturer Sp      | ecific (0x80-0xFE)                                   | 86 |

|                          | Register Behavior                                    |    |

| 10.1 Introduction        |                                                      | 87 |

| 10.2 StatusF/Status      | sW Register Definitions                              | 87 |

| 10.3 Status Bit Dete     | ermination Conditions and Behavior                   | 88 |

| 10.4 Effects of Alar     | m During Tuning (ADT) bit in MCB register (0x33)     | 90 |

| 11 Optical Specification | ns                                                   | 92 |

|                          | cteristics                                           |    |

|                          | meter Definitions                                    |    |

|                          | ncy Tuning Range                                     |    |

|                          | utput Power                                          |    |

|                          | Power Variation Across Tuning Range                  |    |

|                          | ncy Error to the ITU Grid                            |    |

| 11.1.1.5 Spectra         | ll Linewidth                                         | 92 |

| 11.1.1.6 SMSR            | (Side Mode Suppression Ratio)                        | 92 |

|                          |                                                      |    |

| 11.1.1.7 RIN (Relative Intensity Noise)                   | 92  |

|-----------------------------------------------------------|-----|

| 11.1.1.8 Source Spontaneous Emission                      |     |

| 11.1.1.9 Polarization Extinction Ratio                    |     |

| 11.1.1.10 Optical Attenuation                             | 93  |

| 11.1.2 Application Requirement 1 (Ultra Long Haul)        |     |

| 11.1.3 Application Requirement 2 (Long Haul)              |     |

| 11.1.4 Application Requirement 3 (Metro)                  |     |

| 11.2 Timing Specifications                                |     |

| 11.3 Module Warm Up Time                                  | 97  |

| 11.4 Frequency and Optical Power Transient Specifications | 97  |

| 12 Mechanical Specifications                              | 99  |

| 12.1 Integrable Assembly Mechanical Outline Dimensions    | 99  |

| 13 Appendix A: Open Issues / Current Work Items           |     |

| 14 Appendix B: List of Companies and Contributors         | 101 |

| 14.1 Technical Contributors (to the Original Document)    | 101 |

| 14.2 List of OIF Member Companies (at time of adoption)   | 101 |

| 15 Document Index                                         | 102 |

# 2 List of Tables

| Table 6.4-1: Example Reading Module Status                                 | 15 |

|----------------------------------------------------------------------------|----|

| Table 6.4-2: Extended Address Register Description                         | 16 |

| Table 6.4-3: Extended Address Register READ Example                        |    |

| Table 7.1-1 Pin Assignments                                                | 19 |

| Table 7.1-2 Pin Functions                                                  | 20 |

| Table 7.1-3: Electrical Characteristics                                    | 22 |

| Table 7.1-4: Absolute Maximum Ratings                                      | 23 |

| Table 7.2-1: Communication Byte Numbering                                  | 24 |

| Table 7.2-2 RS232 Physical Interface Pins                                  | 24 |

| Table 9.1-1: Packet Status Flags                                           |    |

| Table 9.2-1: Table of Registers (Commands)                                 | 31 |

| Table 9.4-1 Extended Address Space Mode Selection (EAM)                    | 48 |

| Table 9.4-2 Firmware Download Example                                      | 50 |

| Table 9.4-3 Firmware Upload Example                                        | 51 |

| Table 10.2-1: Status Fatal register 0x20 (StatusF) description             | 87 |

| Table 10.2-2: Status Warning register 0x21 (StatusW) description           | 87 |

| Table 10.2-3: SRQ Trigger register 0x28 (SRQT) description                 | 88 |

| Table 10.2-4: Fatal Trigger register 0x29 (FATALT) description             | 88 |

| Table 10.2-5: Alarm Trigger register 0x2A (ALMT) description               | 88 |

| Table 10.3-1: Determination conditions for each bit in the status register | 88 |

| Table 11.1-1: Optical Specification Requirement Matrix                     |    |

| Table 11.1-2: Optical Specifications (Application 1)                       |    |

| Table 11.1-3: Optical Specifications (Application 2)                       |    |

| Table 11.1-4: Optical Specifications (Application 3)                       |    |

| Table 11.2-1: Timing Specifications                                        | 97 |

| Table 11.3-1: Module Warm Up Time                                          | 97 |

# 3 List of Figures

| Figure 6.3-1: Three Layer Communication Diagram                                            | 14 |

|--------------------------------------------------------------------------------------------|----|

| Figure 6.4-1: Paradigms for Module Control                                                 | 15 |

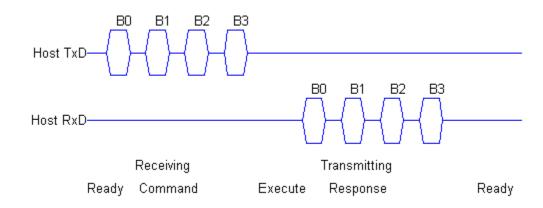

| Figure 7.2-1: RS232 Timing                                                                 | 25 |

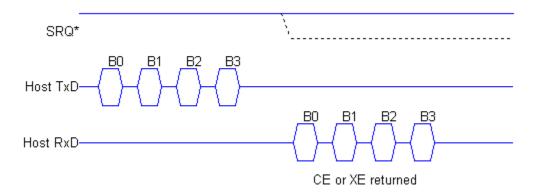

| Figure 7.2-2: RS232 Communication or Execution Error Timing                                | 25 |

| Figure 8.1-1: In-Bound (Host to Module) Frame                                              | 27 |

| Figure 8.1-2: Out-Bound (Module to Host) Frame                                             | 27 |

| Figure 8.1-3: Transport Layer Field Definitions                                            | 27 |

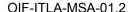

| Figure 11.4-1: Frequency and power transient mask. t <sub>1</sub> is manufacturer specific | 98 |

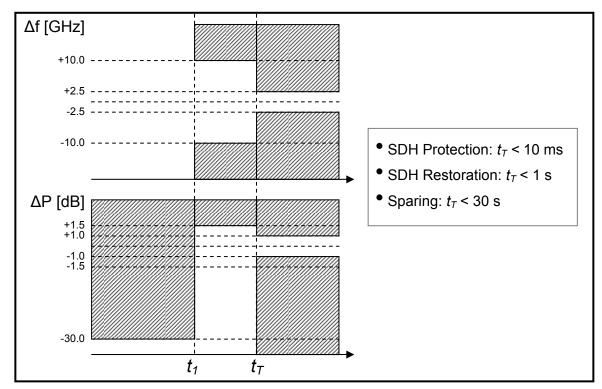

| Figure 12.1-1: Mechanical Outline Dimensions                                               | 99 |

| Figure 12.1-2: Mechanical Dimensions                                                       |    |

# 4 Document Revision History

| Version          | Date             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF-ITLAMSA-01.0 | 30 June 2004     | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Initial release  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OIF-ITLAMSA-01.1 | 22 November 2005 | Includes approved edits from oif2004.287.02 into working list.  • Modified Error! Reference source not found. removing the thread specification (Comment 1) for the transponder housing.  • Added LstRsp bit in Figure 8.1-1and Figure 8.1-3. Addeed description in Section 6.5.2.2. Marked LstResp as deprecated in Table 9.2-1. Elaborated on use of LstRsp bit in Section9.4.12. Includes updates from OIF2005.033.00:  • Add heat sink footnote in Table 7.1-4.  • Renamed FW to Release in Table 9.2-1.  • Corrected units from dBm to dB for F/WPowTh in Table 9.2-1.  • Changed de-asserted to asserted in 9.5.7 for clarification and consistency.  • Changed bit 26 of out bound frame in Figure 8.1-2 to 1 which is consistent with TL-MSA.  • Errata: fixed unsigned to signed for Registers 9.8.1 and 9.8.2.  • Modified connectors from FTM/CLM to ASP equivalents for GR1217 metallurgical compliance in 7.1.1. FTM-107-03*-DV replaced with ASP-115915-01. CLM-107-02*-D replaced with ASP-115915-01. CLM-107-02*-D replaced with ASP-113466-01.  • Modified SSE units from dBc/nm to dBc in 11.1.2, 11.1.3, and 11.1.4.  • Updated figures in section 12.1 for the 18.29mm flex connector length and added additional views for clarity. Changed Sparing Frequency Tuning Time Specification 11.2 from 15s to 30s. Changed Section 11.3 Module Warm Up Time from 30s to 60s.  Modified references section replacing G.692 to G694.1 as DWDM ITU description has been moved.  Modified minimum frequency to 186.0 THz in Sections 11.1.2.1, 11.1.3.1, and 11.1.4.1. Modified respective footnotes 49, 51, and 53 to state frequency range is informative not normative.  9.4.10 under detailed description – the word 'then' changed to 'when'.  9.4.13 Data Value Description – removed duplicate number 12, and replaced it with 13.  9.7.4 added '[R]' in title (since it is read only). |

|                  |                  | integer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                  | 9.8.2 – change the word currents to temperatures and unsigned to signed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OIF-ITLAMSA-01.2 | 26 June 2008 | Added DitherAA pin. See 7.1.2, Table 7.1-2, Table 7.1-3. Added FTF register (0x62) in Table 9.2. Added Section 9.8.7, FTF (0x62) register. Modified equations in Sections 9.6.7 (LF1/LF2), 9.6.1 (Channel), 9.6.5 (Grid) to include FTF setting, and scaled all units in equation to GHz. Added FTFR register (0x4F) in Table 9.2. Added Section 9.7.1, FTFR (0x4F) register. Added Section 9.7.1, FTR (0x4F) register. Added Section 9.7.1, FTR (0x4F) register. Updated data value description in Section 9.5.4 from 0x25/0x24 to 0x27/0x26. Updated electrical connectors to CLM-107-02-H-D-K-TR and ASP-124330-02 in Section 7.1.1 and 12. Added 2mm minimum bend radius to mechanical drawing in Section 12.1. Added protocol version and up revision to 2.0.0 on Page 10. Revised PV version number in example in Section 9.4.7, Release register, to 2.0.0. Deleted CRC-16 section and all references to [W/R]CRC as command had been deprecated in previous release. Removed User Data Storage (0xFF) register as command was deprecated in previous release. Removed Lock register (0x16) and all references to lock. Fixed typo in Section 9.6.8 (FCF1/FCF2) where text referred incorrectly to LF1/2 when it should be FCF1/2. Added Section 10 describing the behavior of alarm and status registers. Modified 3ll references to ALM* and FATAL* to either pointing to software bits ALM, FATAL respectively or removing reference as hardware lines do not exist in this MSA (only in tunable laser MSA). Modified Sections 9.5.7 (ALMT) and 9.6.4 (MCB) recommendation from 50x504 to 0x700 as fatal bits do not assert during funing. Clarified DLStatus 9.4.14 to state that IS_VALID is set once both TYPE and INT_CHECK are asserted. Statement added: "and with "INT_CHECK" equal to 1." Removed non-volatile support for gencfg register as CRC-16 no longer supported. See Section |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Working Group: Physical Link Layer

TITLE: Integrable Tunable Laser Assembly MSA (ITLA-MSA)

SOURCE: Raj Batra Karl Gass

Technical Editor Working Group Chair

Emcore Corporation Sandia National Laboratories

8674 Thornton Avenue P.O. Box 5800 MS-0874

Newark, CA 94560 Albuquerque, NM 87185

Phone: 510 896 2072 Phone: 505 844 8849

Email: raj\_batra@emcore.com Email: kgass@sandia.gov

DATE: 26 June 2008 PROTOCOL VERSION: PV:2.0.0

Project Name: Integrable Tunable Laser Assembly MSA (ITLA-MSA)

Project Number: OIF-0013

**Project Abstract:** This contribution contains the updated changes to MSA-IA-01.0 for the

Integrable Tunable Laser Assembly (ITLA) for integration into a 300-pin 3.5"x4.5" transponder. The changes incorporated are from oif2005.128.04 as approved in the technical committee principal ballot oif2005.372.00.

# 5 References and Conventions

# 5.1 External Reference Documents

The following documents should be read in conjunction with this specification

OIF-TLMSA-01.0 OIF Tunable Laser MSA Implementation Agreement

(www.oiforum.com)

300 Pin MSA 1) Reference Document for 300 PIN 10Gb Transponder

2) Reference Document for 300 PIN 40Gb Transponder 3) I<sup>2</sup>C Reference Document for 300 Pin MSA 10G and 40G

Transponder

GR-468 CORE General Reliability Assurance Requirements for Optoelectronic

Devices Used in Telecommunications Equipment

CENELEC EN50081-1 Electromagnetic Compatibility – Generic Emissions Standard

part 1: Residential, Commercial and Light Industry

EN50082-1 Electromagnetic Compatibility – Generic Immunity Standard part

1: Residential, Commercial and Light Industry

EN50081-1 Electromagnetic Compatibility – Generic Emissions Standard

part 2: Residential, Commercial and Light Industry

EIA RS-232D The RS232 Bus Specification

21CFR1040.10 Laser Safety

IEC 60825-1 Safety Of Laser Products Part1: Equipment Classification,

Requirements and Users Guide

G.694.1 Spectral grids for WDM applications: DWDM frequency grid

# 5.2 Conventions Used in This Document

Numeric Values:

5, 05 Decimal 0x05 Hexadecimal

Bit Numbering

Bit 0 is LSB<sup>1</sup>

<u>Operators</u>

& bitwise AND& logical AND| bitwise OR| logical OR

bitwise exclusive OR

bitwise not

>> right bit shift operator

Data Types

Unsigned short int 16 bit, big endian

Signed short int 15 bit + 1, two's complement, big endian

Character 7-bit ASCII character (0x00 to 0x7F) (\0 is the null character)

Printable character (0x20 to 0x7E)

String (ASCII) All strings are null terminated string (first character bits are 15:8)

<sup>1</sup> LSB: Least significant bit

Integrable Tunable Laser Assembly Multi Source Agreement

**Data Direction**

Out-bound Module to host transfer (Response packet) In-bound

Host to module transfer (Command from host)

Module

Module Refers to the integrable assembly as a module.

<u>Transponder</u>

Portion of housing to which external heat sink is attached Base Portion of housing with opening for 300 pin connector Lid

# 6 Introduction

# 6.1 Scope

This document is a Multi-Source Agreement for integrable tunable laser assemblies. It details a communication protocol, electrical interface, power supply, optical specifications, and a mechanical interface for use in telecommunications equipment operating in the C or L band.

# 6.2 Background

The OIF has completed two tunable laser projects. The first project resulted in the <u>Tunable Laser Implementation Agreement</u>, OIF-TL-01.1 began in April 2001 and was released in November 2002. A large number of contributors from a wide variety of consumers and suppliers of tunable lasers were involved in contributing and reviewing the first Implementation Agreement. It addressed the communication protocol, electrical interface and mechanical form factor interoperability for tunable continuous wavelength (CW) lasers. The document serves as a roadmap for future tunable device implementation agreements.

In February 2003, the OIF began a new fast track project, the <u>Tunable Laser MSA Implementation Agreement</u>. This MSA-IA builds upon the existing <u>Tunable Laser Implementation Agreement</u>, generating a more comprehensive specification of the optical, electrical, mechanical, and communication protocols. It was completed in May 2003.

In October 2003, the OIF began a new project, the Integrable Tunable Laser Assembly (ITLA) MSA Implementation Agreement to focus on standardization of a CW laser subassembly for integration into transponders for both the 3.5"x4.5" transponder as well as the small form factor transponder.

The OIF-IAs can be found at <a href="www.oiforum.com">www.oiforum.com</a> as document OIF-TL-01.1.pdf at <a href="http://www.oiforum.com/public/documents/OIF-TL-01.1.pdf">http://www.oiforum.com/public/documents/OIF-TL-01.1.pdf</a> and OIF-TLMSA-01.0.pdf at <a href="http://www.oiforum.com/public/documents/OIF-TLMSA-01.0.pdf">http://www.oiforum.com/public/documents/OIF-TLMSA-01.0.pdf</a>.

# 6.3 Communication Overview

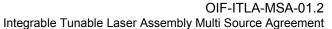

The following diagram (Figure 6.3-1) depicts the communication process.

Figure 6.3-1: Three Layer Communication Diagram

Assume the host has a request to transmit to the module (Host's Request). The request is first encoded as a 28-bit command packet in the Host Driver's application layer. The command is then framed as a 32-bit packet in the host driver's transport layer. The framing operation includes the addition of a BIP-4<sup>2</sup> checksum. Finally, the host driver's physical interface (RS232 shown) encodes the 32 bit packet as 4 ten bit<sup>3</sup> RS232 "characters" and transmits in across the TxD line to the module.

The module's physical layer receives 40 bits and de-codes them by removing the RS232 start and stop bits. The resulting 32-bit frame is delivered to the transport layer where checksum is checked for consistency. Assuming no error is generated, the 28-bit command packet is delivered to the module's application layer where the command is decoded and executed.

The command execution will generate a response when complete<sup>4</sup>. The response packet consists of 26 bits.

The response packet is delivered to the module's transport layer which frames the packet by pre-pending a checksum, communication error (CE). The resulting 32-bit packet is then delivered to the module's physical layer where it is then encoded as 40 bits.

The host then receives the 4 RS232 characters and performs the inverse operations as the packet moves up the host's layer hierarchy.

<sup>&</sup>lt;sup>2</sup> Bit Interleaved Parity (4 bits)

<sup>&</sup>lt;sup>3</sup> Note each byte to be transmitted by RS232 is encapsulated by a start and stop bit thus prepending 1 bit and post-pending 1 bit for a total of 10 bits for each byte to be transmitted.

<sup>&</sup>lt;sup>4</sup> Note that an initial response may also be generated for commands whose execution time exceeds the command response timeout period. The host can either poll for completion of the command or have pre-configured the module to issue a service request (SRQ) upon completion of the command.

#### 6.3.1 Physical Interfaces

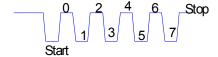

The communications interface supports only one physical layer protocol, RS232.

#### 6.4 Command Overview

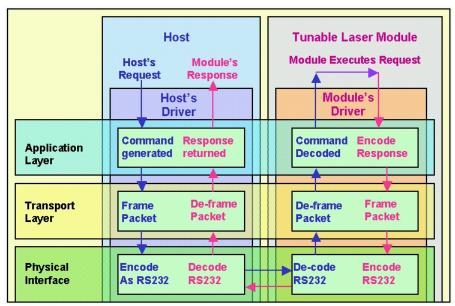

The commands to the module consist of a 9-bit operation followed by 2 bytes of optional data. Alternatively, the command can be thought of as one read/write bit followed by an 8-bit register number followed by 2 bytes of optional data. See Figure 6.4-1. The register paradigm will be used in this document.

Figure 6.4-1: Paradigms for Module Control

There are 256 directly accessible registers (0x00 to 0xFF) in the primary register address space. The OIF-IA allocates the first 32 registers (0x00 to 0x1F) for generic module operations for all module types. Another 96 registers (0x20-0x7f) are reserved for device type "CW Laser Int Assy". Finally, the remaining 128 registers (0x80-0xFF) are provided as manufacturing specific registers.

The following example shows how the module's status would be read.

**Table 6.4-1: Example Reading Module Status**

|   | Com                                                                                    | mand (Host to Mod | ule)                    | Response (Module to Host) |                |                   |

|---|----------------------------------------------------------------------------------------|-------------------|-------------------------|---------------------------|----------------|-------------------|

| # | Operation                                                                              | Register          | Data<br>Bytes<br>(15:0) | Status                    | Register       | Data Bytes (15:0) |

| 1 | Read                                                                                   | 0x20 (StatusF)    | 0x0000                  | 0x00 (Ok)                 | 0x20 (StatusF) | 0x0000            |

| ı | Note: Example shows that the module status is 0x0000 as returned in the response data. |                   |                         |                           |                |                   |

### 6.4.1 Command Execution Overlap

The application layer provides support for pending operations especially useful for operations that can take a significant period of time to complete<sup>5</sup>.

If a command is issued to the module that results in a long time to complete, the module will return a response packet within the specified time out period for the module and flag the operation as pending <sup>6</sup>. The interface is now free to respond to additional commands. The host can determine when the pending operation completes by polling the NOP register (0x00). The NOP register returns the pending operation status as well as any error conditions. Note that the module can be configured to generate an SRQ (Service Request) when a pending operation terminates operation in an error state. See §9.4.1 and §9.1.2.

<sup>&</sup>lt;sup>5</sup> Channel tuning is an example of a command which can take from 5ms to 15s to achieve depending on laser technology utilized.

<sup>&</sup>lt;sup>6</sup> Some other interfaces such as the 300-pin transponder MSA do not allow command execution overlap.

#### 6.4.2 Extended Addressing

Extended addressing provides an additional memory space (22 address bits) in addition to the primary 256 registers (8-bit address space).

The extended addressing feature consists of three registers described in Table 6.4-2.

**Fields** Register Description Defines the Defines basic configuration for the extended Configuration address space address high order address bits Address of field in either physical or virtual Defines the 16 low order address Address memory space bits Reading from this register returns data stored in this field 16 bits at a time Contents 16 bit data value Write to this register stores data into this field 16 bits at a time

**Table 6.4-2: Extended Address Register Description**

Once the configuration and address registers are configured, the host may issue a series of read or write commands to the (indirect contents register) thereby accessing the memory location pointed to by the indirect register. The locations may map to physical or virtual memory spaces.

The configuration register and address registers are usually pre-configured when one of the primary registers is accessed which holds an object longer than a 16-bit integer.

For example, the device type of the laser is stored in register. The DevTyp register (0x01) requires the use of the extended address register. Table 6.4-3 shows an example where the DevTyp register is read and the module returns the 8-character string "CW ITLA\0". The table shows a seventh entry showing what happens if the read extends beyond the available string length.

|   | Command (Host to Module)                                                                              |                |                         | Response (Module to Host) |                |                               |  |

|---|-------------------------------------------------------------------------------------------------------|----------------|-------------------------|---------------------------|----------------|-------------------------------|--|

| # | Operation                                                                                             | Register       | Data<br>Bytes<br>(15:0) | Status                    | Register       | Data Bytes (15:0)             |  |

| 1 | Read                                                                                                  | 0x01 (DevTyp)  | 0x0000                  | 0x02 (AEA-flag)           | 0x01 DevTyp    | 0x0008<br>(# bytes in string) |  |

|   | Note: When the Read is completed, registers (0x09, and 0x0A) are configured to point to proper field. |                |                         |                           |                |                               |  |

| 2 | Read                                                                                                  | 0x0B (AEA-EAR) | 0x0000                  | 0x00                      | 0x0B (AEA-EAR) | 0x4357 ("CW")                 |  |

| 3 | Read                                                                                                  | 0x0B (AEA-EAR) | 0x0000                  | 0x00                      | 0x0B (AEA-EAR) | 0x2049 (" I")                 |  |

| 4 | Read                                                                                                  | 0x0B (AEA-EAR) | 0x0000                  | 0x00                      | 0x0B (AEA-EAR) | 0x544C ("TL")                 |  |

| 5 | Read                                                                                                  | 0x0B (AEA-EAR) | 0x0000                  | 0x00                      | 0x0B (AEA-EAR) | 0x4100 ("A\0")                |  |

| 6 | Read                                                                                                  | 0x0B (AEA-EAR) | 0x0000                  | 0x01 (XE-flag)            | 0x0B (AEA-EAR) | 0x0000                        |  |

Table 6.4-3: Extended Address Register READ Example

Writing to an extended address field is handled in much the same way. The initial write causes the configuration and address registers to be preset to the appropriate values. Writing to the extended address register then stores the 16 bit values sequentially into the field.

#### 6.4.3 Data Types

All of the general registers hold 16-bit data values or serve as pointers to a sequence of bytes (extended addressing mode). All values are stored as big endian, two's complement<sup>7</sup>.

#### 6.4.3.1 Two Byte Data Values

Data is represented in the registers as either signed or unsigned 16 bit integers. Note that single byte values would be stored with the appropriate leading zeros.

Real values are stored with an implied decimal point location. For instance, the value "12.3 dBm" would be stored as 123<sub>10</sub> in a field and has an implied formatting of one decimal place.

#### 6.4.3.2 Multi-byte Fields

Fields holding data longer than 16 bits are stored as a sequence of bytes and accessed through the extended addressing register.

ASCII strings are terminated with a null. Note that the extended address register allows the host to read beyond a null termination but not beyond the maximum field size.

Integers, floats, or structures are stored as a sequence of bytes<sup>7</sup>.

#### 6.4.4 Execution Error Field Conditions

The reason for an execution error (XE) can be determined by reading the NOP/Status register (NOP 0x00). Bits 3:0 encode the error field value. The following table describes the error conditions.

| Error Field                                                                          | Symbol                                                                         | Meaning                                                                                                         |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| 0x00                                                                                 | OK                                                                             | Ok, no errors                                                                                                   |  |

| 0x01                                                                                 | RNI                                                                            | The addressed register is not implemented                                                                       |  |

| 0x02                                                                                 | RNW                                                                            | Register not write-able; register cannot be written (read only)                                                 |  |

| 0x03                                                                                 | RVE                                                                            | Register value range error; writing register contents causes value range error; contents unchanged <sup>8</sup> |  |

| 0x04                                                                                 | CIP                                                                            | Command ignored due to pending operation                                                                        |  |

| 0x05 CII Command ignored while module is initializing, warming invalid configuration |                                                                                | Command ignored while module is initializing, warming up, or contains an invalid configuration                  |  |

| 0x06                                                                                 | ERE                                                                            | Extended address range error (address invalid)                                                                  |  |

| 0x07                                                                                 | ERO                                                                            | Extended address is read only                                                                                   |  |

| 0x08                                                                                 | EXF                                                                            | Execution general failure                                                                                       |  |

| 0x09                                                                                 | CIE Command ignored while module's optical output is enabled (carryin traffic) |                                                                                                                 |  |

| 0x0A                                                                                 | IVC                                                                            | Invalid configuration, command ignored                                                                          |  |

| 0x0A-0x0E                                                                            |                                                                                | Reserved for future expansion                                                                                   |  |

| 0x0F                                                                                 | VSE                                                                            | Vendor specific error                                                                                           |  |

# 6.5 Command & Module Features

#### 6.5.1 Module Reset

The module provides four ways to accomplish reset.

| Reset Technique | Resulting Action |

|-----------------|------------------|

|                 |                  |

<sup>&</sup>lt;sup>7</sup> For instance, the number 256<sub>10</sub> (0x0100) is stored as the byte sequence 0x01, 0x00. The string "HI" is stored as the series of bytes: 0x48 ('H'), 0x49 ('I'), 0x00('\0').

<sup>&</sup>lt;sup>8</sup> Note that an RVE error can occur if a field can only take on certain discrete values and an invalid value is written. For instance, a particular module may only support 25GHz or 50GHz grid intervals. If an interval of 30GHz is written and is not supported, the module will return an RVE error code.

| Hardware | Module Select<br>(when MS* de-asserted and then<br>re-asserted (specifically the low<br>to high transition)) | Clears communication input buffers, may reset baud rate to default (See §7.2.1). Does not affect AEA registers. |  |

|----------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

|          | Reset (RST* low)                                                                                             | Traffic interrupting – reboots module.                                                                          |  |

| Software | ResEna (0x32) (SR Bit = 1)                                                                                   | Aborts transfers in progress (FW download, AEA transfers)                                                       |  |

| Soliware | ResEna (0x32) (MR Bit = 1)                                                                                   | Traffic interrupting – reboots module.                                                                          |  |

#### 6.5.2 Communication Error Detection

Communication error detection occurs on the module and host sides of the communication interface.

#### 6.5.2.1 Detection by Module

The module examines the in-bound packets (host to module) to see if the checksum (see §8.2) is consistent. An inconsistency results in a unprocessed response packet with the CE flag asserted in the out-bound packet.

When the host observes the CE flag, the last out-bound packet should be resent.

# 6.5.2.2 <u>Detection by Host</u>

The host examines the response packets for consistency by checking the checksum (see §8.2) for the out-bound packet (module to host). If the checksum is inconsistent, the host may request the module's last response to be retransmitted by setting the LstRsp bit in the Host to Module Packet. This can also be accomplished by reading the deprecated LstResp (0x13) register.

#### 6.5.3 Execution Error Detection

Execution errors occur when the module is unable to execute the requested command. The module encodes the XE flag bit (execution error flag) in the response packet. When the host detects an XE flag in the response packet, it can read the NOP (0x00) register to determine the error field condition. The reasons for failure to execute a command are enumerated in §6.4.4-Execution Error Field Conditions.

#### 6.5.4 Module Signaling Line

The module has one hardware line to signal its status, SRQ\*.

The SRQ\* line is used to signal fatal conditions, warning conditions, or other module service request needs such as an execution error (XE) for a command processing in the background (pending operation). The SRQ\* line, once asserted, remains asserted until the status register is cleared.

Alarm or fatal conditions can be determined by reading the status registers (See §9.5.1).

# 6.5.5 Non-Volatile Default Configuration

The command interface allows the current module configuration to be saved as the default configuration. The default configuration is restored upon hard reset (See §6.5.1 Module Reset) or upon power up. In the event of loss of power or hard reset during a save configuration request, the module's default configuration will remain unchanged. See (§9.4.9 General Module Configuration (GenCfg 0x08) [RW]).

# 7 Physical Layer & Electrical Characteristics

This section describes the electrical interfaces and the physical layer interface.

# 7.1 Assembly Electrical Interface

#### 7.1.1 Electrical Connector on User's Board

User's connector on transponder board: Samtec P/N CLM-107-02-H-D-K-TR<sup>9</sup> or equivalent.

Note: Connection from integrable assembly module made through flex-circuit cable with appropriate mating connector for the user's Samtec CLM-107-02-H-D-K-TR connector. The mating connector is ASP-124330-02<sup>10</sup> which is on the flex cable.

# 7.1.2 Pin Assignments

The pin assignments shown in Table 7.1-1. The pin functions are described in Table 7.1-2.

**PIN Name** PIN# PIN# **PIN Name** +3.3V Supply 1 2 DIS\* +3.3V Supply 3 4 SRQ\* Gnd MS\* 5 6 Gnd TxD 7 8 -5.2 Supply 9 10 RxD -5.2 Supply 11 12 RST\* OIF Reserved 13 DitherAA<sup>11</sup> 14

**Table 7.1-1 Pin Assignments**

www.oiforum.com

\_

<sup>&</sup>lt;sup>9</sup> This connector is equivalent to CLM 107-2-X-D with additional plating for GR1217 metallurgical compliance.

<sup>&</sup>lt;sup>10</sup> This connector is equivalent to ASP-119097-01 and FTMH-107-03-\*-DV with different plating and/or thicknesses. The mating height is 4.06mm with FTMH-107-03-X-DV. The mating height is further increased by the technique used to attach a cable to the connector. The flexi-PCB could add 0.1mm to 0.2mm in additional height.

<sup>&</sup>lt;sup>11</sup> Amplitude dither for trace tone functionality (TxTrace).

# **Table 7.1-2 Pin Functions**

| Pin Numbers | Symbol  | Туре                     | Name                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5,7         | GND     | Power                    | Ground                                    | Ground  Note: Ground pins are tied together internally to the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1,3         | PS+3.3V | Power                    | +3.3V Supply                              | 3.3V Power Supply Note: Pins are tied together internally to the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9,11        | PS-5.2V | Power                    | -5.2V Supply                              | -5.2V Power Supply Note: Pins are tied together internally to the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12          | RST*    | LVTTL input, active low  | Reset                                     | Purpose: Disables laser output and holds the module in RESET Initial State: Any – user application specific Action: Laser OFF, TEC OFF, Module CPU held in RESET, Communication protocol is OFF Resultant State: High, Must remain high for laser to operate Attributes: When active, lowest current draw from the module.                                                                                                                                                                                                                                                              |

| 2           | DIS*    | LVTTL input, active low  | Disable module's optical output           | Purpose: Provide hardware control to kill laser output. Initial State: Any – user application specific Action: High = laser output controlled by protocol; Low = laser output OFF Resultant State: When DIS* asserted, communication protocol is ON, software enable (SENA) reset. Attributes: Bypasses communication protocol to turn laser OFF. Reenabling of the laser requires setting SENA. Otherwise does not interfere with module settings.                                                                                                                                     |

| 4           | SRQ*    | LVTTL output, active low | Programmable<br>module service<br>request | Purpose: General purpose service request. Initial State: High (No service requested) Action: Generates request for service as required to report a variety of conditions by setting line low. SRQ* is asserted when the result of the status (0x20,0x21) OR'd with SRQT trigger (0x28) is non-zero. Resultant State: Communication protocol is ONSRQ* conditions can be read and cleared through interface Attributes: SRQ conditions (and limits) are software configurable and can be re-configured by the user through the interface. Status bits must be cleared to de-assert SRQ*. |

| Pin Numbers | Symbol          | Туре                                          | Name                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----------------|-----------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6           | MS*             | LVTTL input,<br>active low-high<br>transition | Module IO Select<br>(Reset<br>communications<br>interface) | Purpose: Provide hardware control to reset physical interface Initial State: Any – user application specific Action:High or LOW = No effect; Low to High transition – Reset communications interface, clear input buffers, terminate current packet Resultant State: Communication can be commenced upon deassertion with a new packet. Attributes: Provides ability to reset communications interface |

| 8           | TxD             | LVTTL output                                  | Module's Transmit<br>Data                                  | <b>Purpose</b> : Transmit outbound packets from module                                                                                                                                                                                                                                                                                                                                                 |

| 10          | RxD             | LVTTL input                                   | Module's Receive<br>Data                                   | Purpose: Receive inbound packets from host                                                                                                                                                                                                                                                                                                                                                             |

| 13          | OIF<br>Reserved | LVTTL input                                   | OIF Reserved                                               | No user connection Purpose: Provide for possible future expansion of communications interfaces                                                                                                                                                                                                                                                                                                         |

| 14          | DitherAA        | 2.5V p-p<br>sinusoidal,<br>analog input       | Dither amplitude analog signal                             | Purpose: Provide trace tone capability. AC coupled inside ITLA. Pull down to ground if not used.                                                                                                                                                                                                                                                                                                       |

# 7.1.3 Electrical Characteristics

**Table 7.1-3: Electrical Characteristics**

| Param                                                              | eter                      | Symbol          | Min   | Тур   | Max   | Unit                        |

|--------------------------------------------------------------------|---------------------------|-----------------|-------|-------|-------|-----------------------------|

| +3.3V Supply vo                                                    | ltage                     | $V_{cc}$        | 3.15  | 3.30  | 3.45  | V                           |

| +3.3V Supply cui                                                   | rrent                     | Icc             |       |       | 1500  | mA<br>(Peak <sup>12</sup> ) |

| -5.2V Supply volt                                                  | tage                      | $V_{EE}$        | 5.45  | -5.20 | -4.94 | V                           |

| -5.2V Supply cur                                                   | rent                      | I <sub>EE</sub> | -1200 | -1000 |       | mA<br>(Peak <sup>13</sup> ) |

| Power Dissipatio                                                   |                           | $P_D$           |       |       | 6.6   | W                           |

| Input voltage, lov                                                 | V                         | $V_{IL}$        | 0.0   |       | 0.8   | V                           |

| Input voltage, hig                                                 | jh                        | $V_{IH}$        | 2.0   |       | 3.45  | V                           |

| Output voltage, low                                                | (I <sub>OL</sub> = 4 mA)  | $V_{OL}$        | 0.0   |       | 0.6   | V                           |

| Output voltage, high                                               | (I <sub>OH</sub> = -4 mA) | $V_{OH}$        | 2.4   |       | Vcc   | V                           |

| Power supply no<br>(for power supplimodule)<br>(100Hz to 20MHz     | ed to the                 |                 |       |       | 1.0   | %rms                        |

| Analog Amplitude<br>(DitherAA) modu<br>(peak to peak).             |                           |                 | 0     | 1.25  | 2.5   | Vpp                         |

| Analog Amplitude voltage range pe swing. Accuracy manufacturer spe | ak to peak<br>is          |                 | 0     | 5     | 10    | %рр                         |

| Analog Amplitude                                                   |                           |                 | 10    |       |       | kΩ                          |

| (AC coupled circuitry in ITLA)                                     |                           |                 |       |       | 10    | pF                          |

| Analog amplitude dither -3dB band                                  |                           |                 | 10    |       | 1000  | kHz                         |

The instantaneous current cannot exceed 1.5 amps.

The absolute value of the instantaneous current cannot exceed 1.2 amps.

The dual supply configuration allows an ITLA to either draw all its power from a single supply or from both supplies as long as the total average power dissipation does not exceed P<sub>D</sub>.

The module must be able to withstand the following conditions without permanent damage.

**Table 7.1-4: Absolute Maximum Ratings**

| Parameter                                          | Symbol             | Min  | Max            | Unit |

|----------------------------------------------------|--------------------|------|----------------|------|

| Operating 'base of butterfly' temperature range 15 | T <sub>BTF</sub>   | -5   | +70            | °C   |

| Total power dissipation                            |                    |      | 6.6            | W    |

| Storage temperature range                          | T <sub>STORE</sub> | -40  | +85            | °C   |

| Storage relative humidity 16                       | RH                 | 5    | 95             | %    |

| Operating relative humidity 16                     | RH                 | 5    | 85             | %    |

| Signal pin voltage                                 |                    | -0.5 | $V_{CC} + 0.3$ | V    |

| Power Pin Voltage 3.3V supply                      |                    | -0.3 | 3.6            | V    |

| Power Pin Voltage -5.2V supply                     |                    | -5.5 | +0.3           | V    |