## OIF OPTICAL INTERNETWORKING FORUM

## **TFI-5: TDM Fabric to Framer Interface Implementation Agreement**

OIF-TFI-5-01.0

September 16, 2003

Implementation Agreement Created and Approved by the Optical Internetworking Forum www.oiforum.com

#### Contribution Number: oif2002.287.17

#### Working Group: Physical and Link Layer

#### TITLE: TFI-5: TDM Fabric to Framer Interface Implementation Agreement

DATE: September 16, 2003

#### SOURCE:

| Brian Von Herzen             | Mike Lerer             | Karl Gass                    |

|------------------------------|------------------------|------------------------------|

| TFI-5 Technical Editor       | PLL Chair              | PLL Vice Chair               |

| Xilinx, Inc./FPGA.com        | Xilinx, Inc./FPGA.com  | Sandia National Laboratories |

| 675 Fairview Drive, #246     | Box 636                | PO Box 5800, MS 0874         |

| Carson City, NV 89701        | Londonderry, NH 03053  | Albuquerque, NM 87185        |

| Phone: +1 775 790-5000       | Phone: +1 603 548 3704 | Phone: +1 505 844-8849       |

| Email: <u>Brian@FPGA.com</u> | Email: mlerer@fpga.com | Email: kgass@sandia.gov      |

|                              |                        |                              |

#### **Document Status:** Approved IA **Project Name:** TFI 5

**ABSTRACT:** This IA lists objectives for TFI-5 connects TDM fabrics to SONET/SDH and OTN Framers (TDM Fabric to Framer Interface or TFI-5), with line-side interface rates of up to OC-768, STM-256 or OTU-3. The interface supports synchronous time-division multiplexed switches that have a minimum granularity of STS-1 and above.

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

For additional information contact: The Optical Internetworking Forum, 39355 California Street, Suite 307, Fremont, CA 94538 510-608-5928 phone, <u>info@oiforum.com</u>

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

© 2003 Optical Internetworking Forum

## 1. Table of Contents

| 0.         | Cover Sheet1                                                                               | ł |

|------------|--------------------------------------------------------------------------------------------|---|

| 1.         | TABLE OF CONTENTS                                                                          | ł |

| 2.         | LIST OF FIGURES                                                                            | 3 |

| 3.         | LIST OF TABLES                                                                             | 7 |

| 4.         | DOCUMENT REVISION HISTORY                                                                  | 3 |

| 5.         | REFERENCES10                                                                               | ) |

| 6.         | INTRODUCTION11                                                                             | i |

| 7.         | REQUIREMENTS12                                                                             | 2 |

| 8.         | INTERFACE DEFINITION14                                                                     | 1 |

| 9.         | SIGNAL DEFINITION                                                                          | 5 |

| 10.        | DETAILED DESCRIPTION                                                                       | 3 |

|            | 10.1 TFI-5 Link Layer                                                                      | 2 |

|            | 10.2 TFI-5 Connection Layer       25         10.3 TFI-5 Mapping Layer       27             | 5 |

| 11.        | ELECTRICAL INTERFACE DEFINITION                                                            |   |

|            | 11.1 Differential Output Characteristics                                                   |   |

|            | 11.2 Differential Input Characteristics                                                    |   |

|            | 11.3 Jitter Requirements                                                                   | 3 |

|            | 11.4 Wander Requirements47                                                                 | 7 |

| 12.        | OPTICAL INTERFACE DEFINITION                                                               | ) |

|            | 12.1 Optical cable, cable plant specification and link budget51                            | I |

| APP<br>PHY | ENDIX A: MAPPING AND TRANSPORT OF ODU3 AND 10GIGE LAN<br>52                                |   |

|            | A.1 Asynchronous mapping of ODU3 into a C-4-272c for transport over 272<br>VC-4 / STS-3c's |   |

|            | A.2 Mapping of 10GE LAN PHY                                                                | 7 |

| APP        | ENDIX B: JITTER NOTES63                                                                    |   |

| APP        | ENDIX C SAMPLE APPLICATION                                                                 | 1 |

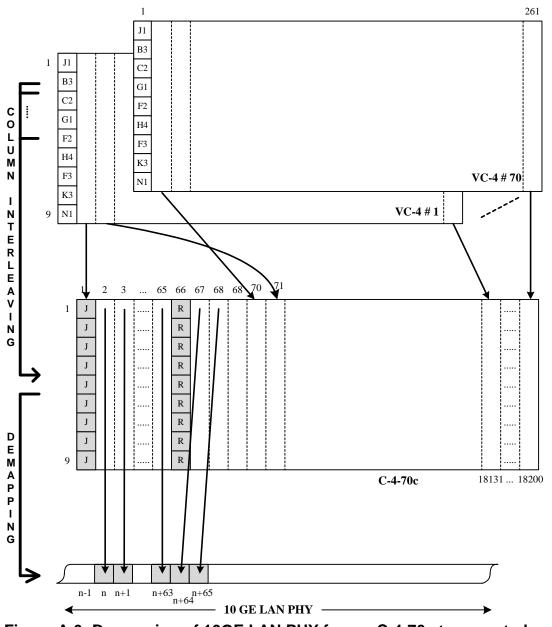

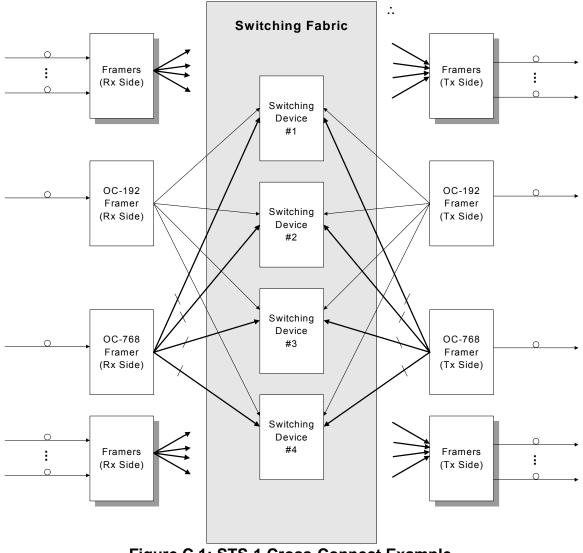

|            | C.1 STS-1 Cross-connect                                                                    | ł |

| APP        | ENDIX D: INTER-CONNECT CHARACTERISTICS                                                     | 5 |

|            | Connector Impedance                                                                        | 3 |

| Characteristic Impedance                   | 66 |

|--------------------------------------------|----|

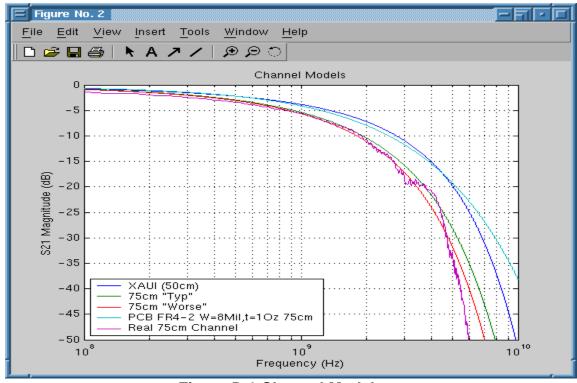

| Channel Model                              |    |

| APPENDIX E: CROSS TALK                     | 69 |

| APPENDIX F: TERMS AND DEFINITIONS GLOSSARY | 70 |

## 2. List of Figures

| FIGURE 8.1 TFI-5 SYSTEM REFERENCE MODEL                                                                    | .14         |

|------------------------------------------------------------------------------------------------------------|-------------|

| FIGURE 10.2 TFI-5 2.488 GBPS (STS-48) FRAME FORMAT (REQUIRED SUPPORT)                                      |             |

| FIGURE 10.3 TFI-5 3.1104 GBPS (STS-60) FRAME FORMAT (OPTIONAL SUPPORT)                                     |             |

| FIGURE 10.4 TFI-5 LAYERS                                                                                   |             |

| FIGURE 10.5 TFI-5 LAYERS EXAMPLE (AN STS-1 CROSS-CONNECT)                                                  |             |

| FIGURE 10.5.1 TFI-5 STATE DIAGRAM FOR OUT OF FRAME AND IN FRAME CONDITION                                  |             |

| TIGORE 10.3.1 TTI-5 STATE DIAGRAM FOR OUT OF TRAME AND IN TRAME CONDITION                                  |             |

| FIGURE 10.5.2 TFI-5 FRAME OFFSET TIMING                                                                    |             |

| FIGURE 10.5.2 TFI-5 FRAME OFFSET TIMING<br>FIGURE 10.6 TFI-5 CONNECTION MONITORING (CM) MULTI-FRAME FORMAT |             |

|                                                                                                            | .20         |

| FIGURE 10.7 EXAMPLE DISINTERLEAVING SHOWING BYTE ORDERING OF AN STS-768                                    | 20          |

|                                                                                                            | .30         |

| FIGURE 10.8 EXAMPLE OF DISINTERLEAVING SHOWING BYTE ORDERING OF AN STS-1                                   | -           |

| FRAME INTO 4 TFI-5 LINKS                                                                                   |             |

| FIGURE 11.1 TFI-5 APPLICATION MODEL FOR THE PURE ELECTRICAL INTERFACE, ALSO                                |             |

| CALLED THE INTRA-RACK SYSTEM                                                                               | -           |

| FIGURE 11.2 GENERAL SIGNAL DEFINITION                                                                      |             |

| FIGURE 11.3 TERMINATION AND SIGNALING                                                                      |             |

| FIGURE 11.4 IDSHORT, IOFF & VRPP TESTING                                                                   |             |

| FIGURE 11.5 RECEIVE EYE MASK                                                                               |             |

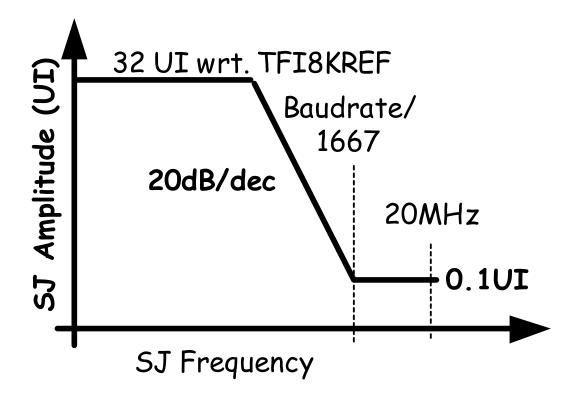

| FIGURE 11.6 SINUSOIDAL JITTER ALLOWABLE AMPLITUDE VS. FREQUENCY. NOTE THA                                  | ١T          |

| RELATIVE WANDER FROM ONE LANE TO ANOTHER CAN BE TWICE THE ABSOLUTE                                         |             |

| WANDER OF 32 UI SHOWN IN THIS DIAGRAM.                                                                     | .48         |

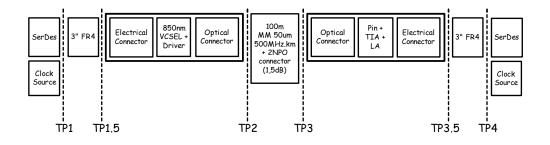

| FIGURE 12.1: ELECTRO-OPTICAL INTER-RACK APPLICATION MODEL                                                  | .49         |

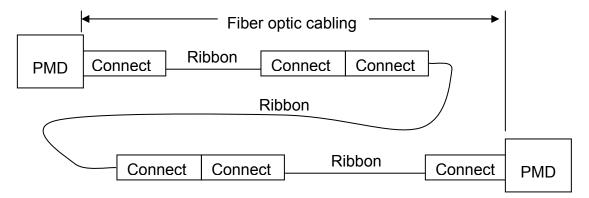

| FIGURE 12.2 FIBER OPTIC CABLING MODEL                                                                      | .51         |

| FIGURE A.1: BLOCK STRUCTURE FOR ODU3 MAPPING INTO C-4-272C                                                 | .54         |

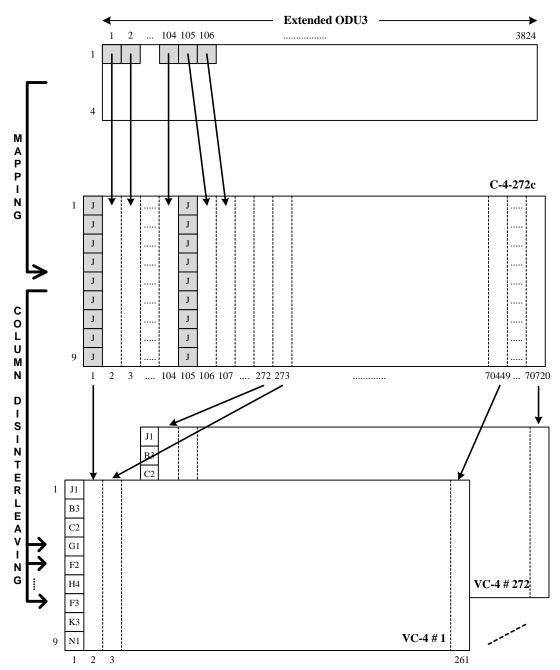

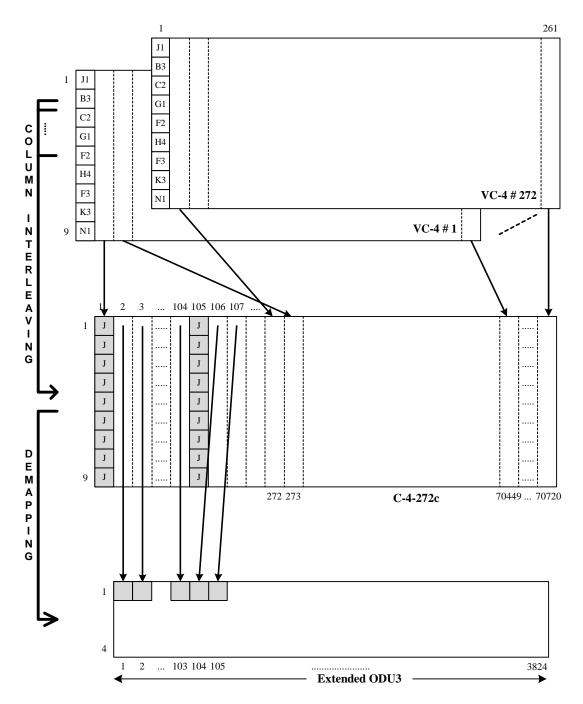

| FIGURE A.2: MAPPING OF ODU3 OVER C-4-272C FOR TRANSPORT OVER 272 VC-4's                                    | s <b>55</b> |

| FIGURE A.3: DEMAPPING OF AN ODU3 FROM A C-4-272C TRANSPORTED OVER 272                                      |             |

| VC-4's                                                                                                     | .56         |

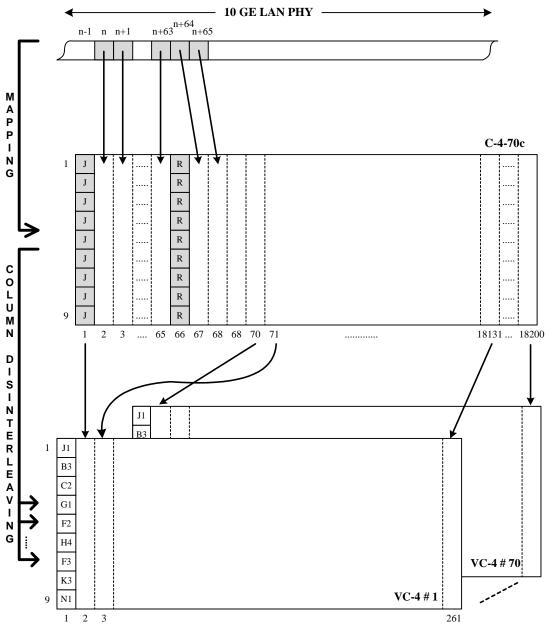

| FIGURE A.4: BLOCK STRUCTURE FOR 10GE LAN PHY MAPPING INTO C-4-70C                                          | .60         |

| FIGURE A.5: MAPPING OF 10GE LAN PHY OVER C-4-70C FOR TRANSPORT OVER 70                                     |             |

| VC-4's                                                                                                     |             |

| FIGURE A.6: DEMAPPING OF 10GE LAN PHY FROM A C-4-70C TRANSPORTED OVER                                      |             |

| VC-4's                                                                                                     |             |

| FIGURE C.1: STS-1 CROSS-CONNECT EXAMPLE                                                                    |             |

| FIGURE D.1 CHANNEL MODELS                                                                                  |             |

|                                                                                                            |             |

## 3. List of Tables

| 6<br>8<br>2 |

|-------------|

| 3           |

| 8           |

| 3           |

| 7           |

| С           |

| 1           |

| 7           |

| 7           |

|             |

| 9           |

| к<br>З      |

|             |

## 4. Document Revision History

- oif2002.287.00 19 May 2002 TFI-5 working group selected proposal OIF2002.122.2 as the Baseline document for TFI-5 from April 2002 OIF Plenary Meeting in Boston, MA.

- oif2002.287.01 No significant changes.

- oif2002.287.02 13 July 2002 TFI-5 Implementation Agreement Draft 1.1. Document revised to incorporate editorial and technical changes from the June 2002 TFI-5 Interim Meeting in San Jose, CA.

- oif2002.287.03: 01 Aug 2002 TFI-5 Implementation Agreement Draft 1.2. Document revised to incorporate editorial and technical changes from the July 30-Aug1 2002 OIF Meeting in Copenhagen DK.

- oif2002.287.04: Marked changes accepted after TFI-5 straw ballot.

- oif2002. 287.05 7 November 2002 TFI-5 Implementation Agreement Draft 1.3. Document revised to incorporate editorial changes from comments received from Straw Ballot #33. clean version

- oif2002. 287.06 7 November 2002 TFI-5 Implementation Agreement Draft 1.3. Same version as .05 but with change bars and changes highlighted.

- oif2002. 287.07 17 November 2002 TFI-5 Implementation Agreement Draft 1.4. Document revised to incorporate changes from the November 2002 TFI-5 Plenary Meeting in Orlando, FL.

- oif2002. 287.08 20 December 2002 TFI-5 Implementation Agreement Draft 1.5. Document revised to incorporate changes from the Straw Ballot of December 16, 2002.

- oif2002. 287.09 20 December 2002 TFI-5 Implementation Agreement Draft 1.5. Document revised to incorporate editorial changes from the TFI-5 conference call on December 20, 2002.

- oif2002. 287.10 12 February 2003 TFI-5 Implementation Agreement Draft 10. Document revised to incorporate technical changes from the TFI-5 interim meeting on 10 February 2003 and changes from the Los Angeles Plenary in February 2003.

- oif2002. 287.11 26 April 2003 TFI-5 Implementation Agreement Draft 11. Document revised to incorporate editorial and technical changes from the TFI-5 conference call on March 28 2003.

- oif2002. 287.12 6 May 2003 TFI-5 Implementation Agreement Draft 12. Document revised to incorporate technical change from the TFI-5 receiver sensitivity ad-hoc conference calls of March and April, 2003.

- oif2002. 287.13 4 July 2003 TFI-5 Implementation Agreement Draft 13. Document revised to incorporate technical changes from the TFI-5 Scottsdale Plenary in April 2003.

- oif2002. 287.14 29 July 2003 TFI-5 Implementation Agreement Draft 14. Document revised to incorporate editorial changes from the TFI-5 Straw Ballot #43.

- oif2002. 287.15 29 July 2003 TFI-5 Implementation Agreement Draft 15, Updated list of figures.

- oif2002. 287.16 29 July 2003 TFI-5 Implementation Agreement Draft 16, Updated appendix D labels.

- oif2002. 287.17 6 August 2003 TFI-5 Implementation Agreement Draft 17, minor editorial changes.

## 5. References

[1] Optical Internetworking Forum, OIF2001.149.14, "SxI-5: Electrical Characteristics of Common I/O for SFI-5 and SPI-5", November 2002.

[2] Optical Internetworking Forum, OIF-SFI5-01.0 - SerDes Framer Interface Level 5 (SFI-5): 40Gbps Interface for Physical Layer Devices.

[3] Optical Internetworking Forum, OIF-SPI5-01.1 - System Packet Interface Level 5 (SPI-5): OC-768 System Interface for Physical and Link Layer Devices.

[4] Telcordia, GR-253-CORE, Issue 3 Sept. 2000 – "Synchronous Optical Network (SONET) Transport System: Common Generic Criteria"

[5] ITU-T, Recommendation G.707, Oct. 2000 – "Network Node Interface For The Synchronous Digital Hierarchy (SDH)"

[6] ITU-T, Recommendation G.709, Feb. 2001 – "Network Node Interface for the Optical Transport Network (OTN)"

[7] ITU-T, Recommendation G.707, Amendment 2, 2002 – "Network Node Interface For The Synchronous Digital Hierarchy (SDH), Amendment 2"

[8] IEEE, 802.3ae-2002, "Information Technology - Local & Metropolitan Area Networks - Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications - Media Access Control Parameters, Physical Layers and Management Parameters for 10 Gb/s Operation"

[9] ANSI; T1.105, 2001; "Synchronous Optical Network (SONET) - Basic Description Including Multiplex Structure, Rates and Formats"

[10] IEEE standard 802.3ae-2002 (Amendment to IEEE Standard 802.3-2002)

## 6. Introduction

There are a number of vendors either offering or involved in offering TDM switching fabrics. Similarly, there are a number of vendors offering TDM framers, which interface to these switch fabrics. Traffic between the framer and the fabric is modeled after a SONET/SDH frame, and operates at the STS-48/STM-16 equivalent bit rate over the backplane. In order to ensure device interoperability across multiple vendor devices it is important that the electrical/optical jitter, and byte signaling protocols are compatible. This **T**DM Fabric to **F**ramer Interface (TFI-5) Implementation Agreement is intended to ensure interoperability through the specification of key functions and/or parameters. The key functions specified within this document include link integrity monitoring, connection management, and mapping mechanisms for both SONET/SDH and non-SONET/SDH clients. TFI-5 is an alternative framer interface compared to SPI-5 [3], which is targeted for packet/cell switch fabrics.

At the August 2001 OIF Plenary meeting, a project was approved to generate an Implementation Agreement called TFI-5 (TDM Fabric to Framer Interface) to connect SONET/SDH framers to TDM fabrics using I/O technologies [1] developed for SFI-5 [2] and SPI-5 [3].

#### 7. Requirements

The TFI-5 interface shall have the following requirements:

- Support SONET/SDH framers with line-side interfaces of OC-48/STM-16, OC-192/STM-64, and OC-768/STM-256.

- Support multi-channel framers with lower rate line-side interfaces with an aggregate bandwidth of N x OC-48/STM-16. (e.g. quad OC-12/STM-4).

- Support any standard compliant mix of non—concatenated, contiguously concatenated and virtually concatenated STS-1-SPE/higher order VC-3 and STS-3c-SPE/VC-4 payloads mapped within the above OC-Ns/STM-Ns.

- Support G.709 OTN framers with line-side interfaces of OTU1, OTU2, and OTU3 by mapping the ODU1, ODU2 and ODU3 into SONET/SDH-like frame formats.

- Support a line-side 10 GE WAN PHY interface as OC-192/STM-64 signal.

- Support for a line-side 10GE LAN PHY interface by mapping into a SONET/SDH-like frame format.

- Uses scrambling to ensure transition density.

- Support lane bandwidths of 2.488 Gbps and include a mechanism to support higher aggregate payload bandwidths across multiple lanes. All lanes are frequency locked to a common reference. Optionally, the TFI-5 link can also operate at a rate of 3.1104 Gbps (STS-60).

- Support byte interleaving.

- Supports de-skew between lanes originating from multiple framers or fabric devices. De-skew algorithm must operate without additional signal lanes.

- Support fabric constructed from multiple devices.

- TFI-5 device shall be capable of checking for errors.

- Capable of driving at least 30 inches of PCB with 2 connectors for intra-shelf environments and at least 100 meters over optics for inter-shelf environments.

- Capable of bit error rate of 10E-12 for PCB and for Optical links. Will have distance de-rating for better BER.

- Support DC coupling. AC coupling is optional.

- Provide a clear forward migration path to future fabrication processes.

- Wide availability of components.

## 8. Interface Definition

TFI-5 is a SONET/SDH-like backplane interface, either electrical or optical, connecting a framer to a TDM switch.

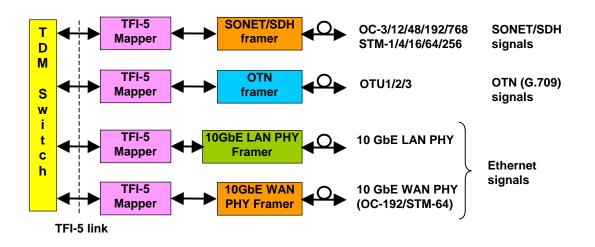

A system reference model is shown in Figure 8.1. A variety of framers, including SONET/SDH, OTN, 10GE WAN PHY and 10GE LAN PHY framers, are shown to operate simultaneously in the system. The transport of client signals through the TFI-5 system is fully specified, within the TFI-5 Implementation Agreement, for SONET and SDH signals (including the 10GE WAN PHY). The transport, through the TFI-5 system of OTN ODU1 and ODU2 clients are defined in Section 10.4. ODU3 and 10GE LAN PHY client mappings are proposed in Appendix A.

Figure 8.1 TFI-5 System Reference Model

As the services provided by the TFI-5 link in the Framer-to-Fabric direction, are identical to that provided in Fabric-to-Framer direction, there is only one definition of a TFI-5 link. It is applicable for either direction of traffic. Separate receive and transmit link definitions are unnecessary. All instantiations of the TFI-5 links in Figure 8.1 are identical: a 2.488 Gbps (or 3.1104 Gbps) link locked to a common system reference clock. The TFI-5 link has the following general characteristics:

- 1. A TFI-5 link is a point-to-point connection between a framer and a TDM switch fabric device.

- The format of a TFI-5 link, the TFI-5 frame, is a simplification from Telcordia GR-253-CORE [4], ANSI T1.105 [9] and ITU G.707 [5] SONET/SDH frame (see Section 10). A1/A2 bytes are used for framing, the X<sup>7</sup> + X<sup>6</sup> + 1 scrambling polynomial is used to ensure rich transition

density, B1 is used for link error monitoring, and B2 can be used for connection monitoring.

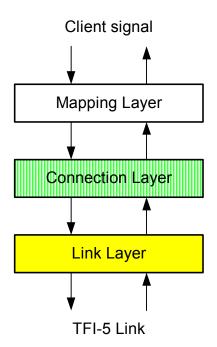

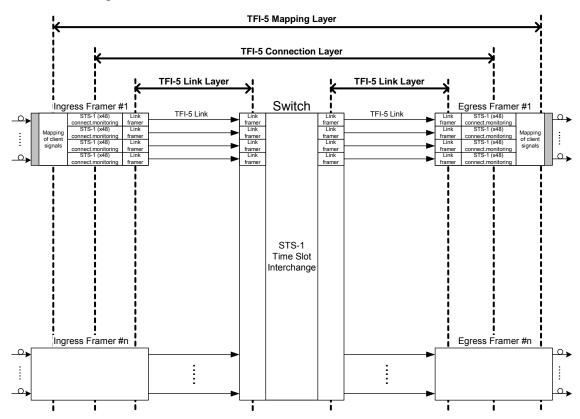

- 3. TFI-5 is defined using a layered approach. Three different layers are defined (see Figure 10.4): Link layer, Connection layer and Mapping layer. The Link layer is generated and terminated by the TFI-5 link source and sink devices and its extent is a TFI-5 link. The Connection layer is generated/ terminated by the framer and its extent is the connection of a tributary (an STS-1 time-slot) from the Ingress framer to the Egress framer, passing through the TDM switch fabric. The Mapping layer is also generated/terminated by the framer. It provides the transport of client signals over one or more Connection layer time-slots.

- 4. All TFI-5 links are frequency locked and all theTFI-5 frames need to be relatively frame aligned within the deskew window of the fabric. Methods of aligning client signals to the TFI-5 frame include pointer processing and multiplexing/demultiplexing and/or through a mapping process.

The use of TFI-5 to connect a framer to a framer, or a TDM switch to a TDM switch, is out of the scope of the TFI-5 Implementation Agreement, but is not precluded.

## 9. Signal Definition

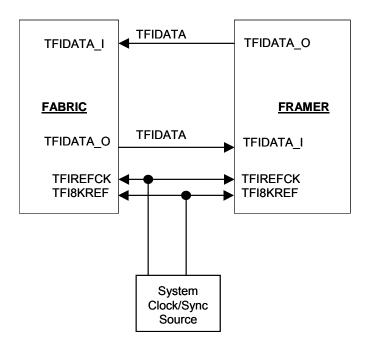

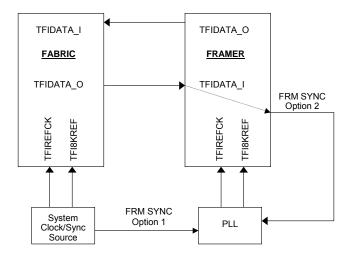

There are only three signals defined in TFI-5; a data signal (TFIDATA), a reference clock signal (TFIREFCK) and an 8kHz frame boundary reference (TFI8KREF). TFIREFCK and TFI8KREF shall be frequency locked to each other with a relative wander of less than +/- 4 UI of TFIREFCK. TFIDATA is differential CML. Examples of intra-shelf and inter-shelf system models are provided in Figures 9.1 and 9.2.

| Signal Name | Function                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TFIDATA     | The <b>TFI-5 Data</b> (TFIDATA) signal carries the data between<br>the Framer and the Switch Fabric. The same signal definition<br>is applicable to data transfer in the Framer to Fabric direction,<br>and the Fabric to Framer direction.                                                                                                                                                                    |  |  |  |  |  |  |

|             | ach TFIDATA link operates at 2.488 Gbps, corresponding to<br>ne standard SONET STS-48 rate and to the standard SDH<br>TM-16 rate. Optionally, each TFIDATA link can operate at a<br>ate of 3.1104 Gbps (STS-60), but support for the 3.1104<br>Bbps rate is not required. Each TFIDATA link transports TFI-5<br>ames (the frame format of TFIDATA). Each TFI-5 frame is<br>nodeled after a SONET / SDH stream. |  |  |  |  |  |  |

|             | TFIDATA is frequency locked to TFIREFCK.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| TFIREFCK    | The <b>TFI-5 Reference Clock</b> (TFIREFCK) signal provides timing reference to all the TFI-5 data (TFIDATA) signals in a system.                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|             | TFIREFCK is nominally a 155.52 MHz, 50% duty cycle clock.<br>Jitter characteristics of TFIREFCK do not directly concern<br>interoperability and are beyond the scope of this<br>implementation agreement.                                                                                                                                                                                                      |  |  |  |  |  |  |

|             | All TFIDATA signals in a system are frequency locked to TFIREFCK.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| TFI8KREF    | The <b>TFI-5 8kHz Frame Reference</b> (TFI8KREF) signal provides reference to frame boundaries for all the devices in a TFI-5 system.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|             | TFI8KREF is nominally a 50% duty cycle clock with a nominal frequency of 8kHz. TFIREFCK and TFI8KREF shall be frequency locked to each other with a relative wander of less than +/- 4 UI of TFIREFCK.                                                                                                                                                                                                         |  |  |  |  |  |  |

#### Table 9.1 TFI-5 Signal Summary

Figure 9.1 TFI-5 Intra-shelf system model

Figure 9.2 TFI-5 Inter-shelf system model with two example clocking implementations.

## 10. Detailed Description

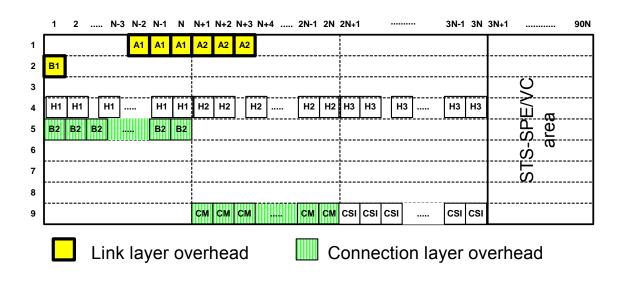

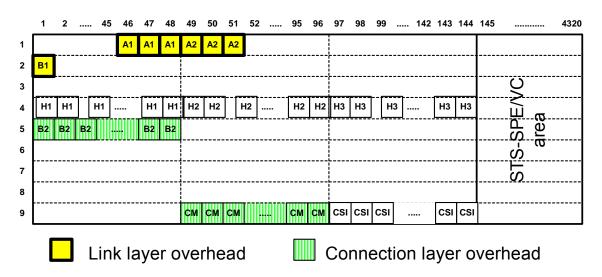

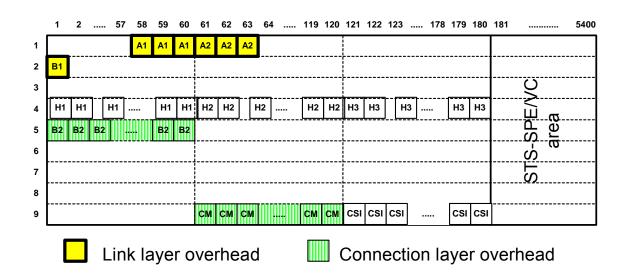

TFI-5 is a SONET/SDH-based backplane interface, either electrical or optical, connecting a framer to a TDM switch fabric. TFI-5 uses a frame-based protocol. Figure 10.1 shows the format of a generic TFI-5 frame, where parameter N is the number of STS-1 time-slots (N = 48 or 60). The colors depicting bytes in figures 10.1, 10.2, and 10.3 correspond with the layers shown in figure 10.4.

Figure 10.1 TFI-5 Frame Format (Generic)

Figure 10.2 shows the TFI-5 2.488 Gbps frame format (N = 48). This frame has the same dimensions as a standard SONET STS-48 or SDH STM-16 frame (9 rows of 4320 columns) and shall be supported for interoperability.

Figure 10.3 shows the TFI-5 3.1104 Gbps frame format (N = 60). This frame has the same dimensions as a SONET STS-60 or SDH STM-20 frame (9 rows of 5400 columns). Support of the TFI-5 3.1104 Gbps rate and frame format is optional.

Figure 10.2 TFI-5 2.488 Gbps (STS-48) Frame Format (required support)

#### Figure 10.3 TFI-5 3.1104 Gbps (STS-60) Frame Format (optional support)

There are three layers defined for TFI-5: Link, Connection and Mapping. Figure 10.4 shows the hierarchical relation between the layers.

The TFI-5 Link layer defines the operations performed and the information generated/terminated by the TFIDATA link source and sink devices. The TFI-5 Link layer is generated and terminated at each TFI-5 link.

- The TFI-5 Connection layer enables monitoring of the end-to end connection of each STS-1 time-slot from Ingress framer to Egress framer, passing through the TDM switch fabric.

- The TFI-5 Mapping layer performs the association and mapping of client signals to one or more STS-1 time-slots of the Connection layer. In order to carry client signals with bandwidths greater than that of a single TFI-5 link, the TFI-5 Mapping Layer can group a set of STS-1 time-slots transported in different TFI-5 links (inverse multiplexing).

Figure 10.5 shows the extent of each TFI-5 layer using a simplified STS-1 cross-connect model. This simplified model separates the Ingress framers (receivers) and the Egress framers (transmitters) in order to simplify the description.

Figure 10.4 TFI-5 Layers

Implementation Agreement: OIF-TFI5-0.1.0 TFI-5 TDM Fabric to Framer Interface

Figure 10.5 TFI-5 Layers Example (an STS-1 cross-connect)

#### 10.1 TFI-5 Link Layer

The Link layer is generated and terminated at each TFI-5 link. The Link layer is independent of the client payload that forms the data stream multiplexed across a group of TFI-5 links. The Link layer embodies the electrical signaling and link rate specifications, link framing, link scrambling, link error monitoring and frame deskew functions. The Link layer operates on each link independently.

The Period of transmission of a TFI-5 frame is 125  $\mu$ s. Two different baud rates are defined: the standard SONET/SDH 2.488 Gbps transmission rate and an optional 3.1104 Gbps transmission rate. Support of the 3.1104 Gbps transmission rate is not required.

The TFI-5 2.488 Gbps frame format is shown in Figure 10.2. The TFI-5 frame format for the optional rate 3.1104 Gbps is shown in Figure 10.3. The bytes and bits are transmitted as defined in [14, 15, 24]: the order of transmission of the TFI-5 frame bytes (Figures 10.2 and 10.3) is first from left to right and then from top to bottom. Within each byte the most significant bit is transmitted first.

The overhead bytes A1, A2 and B1 as shown in figure 10.1, 10.2 and 10.3 are used by the Link layer for frame delineation and supervision purposes. These bytes are generated by each TFI-5 link transmitter (TFI-5 link source device) and terminated by each TFI-5 link receiver (TFI-5 link sink device).

#### 10.1.1 TFI-5 Frame Delineation (A1A2 bytes)

The TFI-5 frame shall contain three A1/A2 pairs (three A1 bytes followed by three A2 bytes) located in the first row. The three A1 bytes are located in columns N-2, N-1 and N, and the three A2 bytes are located in columns N+1, N+2 and N+3 (N = 48, 60). The source device of a TFI-5 link shall insert this 6-byte sequence. The A1 bytes carry the value 0xF6 and the A2 bytes carry the value 0x28.

The sink device of the TFI-5 link locates the TFI-5 frame boundaries by searching for the framing pattern contained In the A1 and A2 bytes as defined above. Implementations of TFI-5 framers may frame on a subset of the 3 A1 and 3 A2 bytes.

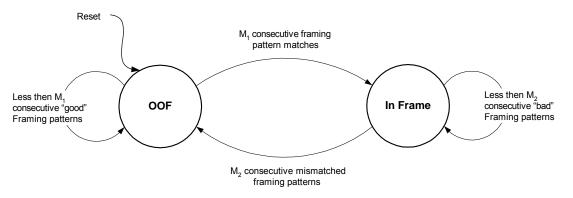

Upon startup or reset the sink device goes to the OOF (Out Of Frame) state (Figure 10.5.1). The sink device shall transition from the OOF state to the INF (In-Frame) state after finding the framing pattern, one TFI-5 frame apart (125  $\mu$ s), for M<sub>1</sub> consecutive frame times. M<sub>1</sub> is defined to be 2 frames in this standard. Once in the INF state, the sink device shall continue to monitor for correct alignment. The sink device of the TFI-5 link shall transition from the INF state to the OOF state if the framing pattern is not found (at least one

incorrect bit) during  $M_2$  consecutive frames.  $M_2$  is defined to be less than or equal to 5 frames in this standard.

#### Figure 10.5.1 TFI-5 State Diagram for Out of Frame and In Frame Conditions

When the sink device of a TFI-5 link is in the OOF state it shall alert the downstream element by overwriting to "all ones" all of the bytes in the Connection and Mapping Layers.

#### 10.1.2 TFI-5 Frame Scrambling

TFI-5 links are scrambled to ensure rich transition density. The TFI-5 link is scrambled with the SONET/SDH polynomial of  $X^7 + X^6 + 1$ . The scrambling is done in the same way as for a standard SONET/SDH frame, as per [14, 15, 24]:

- The residue of the scrambler is initialized to all ones on the mostsignificant bit of the byte in row 1 and column [3\*N]+1 (N = 48, 60) of the TFI-5 frame: this is the first SPE byte of a SONET/SDH frame

- The scrambler is disabled for the bytes located in columns 1 to 3\*N (N = 48, 60) of the first row: this is the whole first SOH row of a SONET/SDH frame.

As an option, it is possible to enable the scrambling of the bytes in columns 1 to N-3 and N+4 to  $3^*N$  (N = 48, 60) of the first row. The bytes in columns N-2 to N+3 (N = 48, 60) are never scrambled, but the scrambler shall continue to run during these byte positions. When this option is enabled, columns 1 to N-3 and N+4 to  $3^*N$  (N = 48, 60) of the first row of the current TFI-5 frame are scrambled with the scrambler running from the reset in the previous TFI-5 frame. This optional "STS-768-like" scrambling mode can be used to assure an adequate number of transitions when the positions in columns 1 to N-3 and N+4 to  $3^*N$  of the first row of the TFI-5 frame are used by the Mapping layer.

When bytes 1 to N-3 and bytes N+4 to 3N are used by the Mapping layer, and the standard SONET/SDH mode of scrambling is enabled, the content of these bytes must be compliant with ITU-T G.957 Appendix II: Consecutive Identical Digits (CID).

Scrambling by all devices in a TFI-5 system should utilize the standard SONET scrambling unless all devices on the link support the optional scrambling mode. For applications that use bytes 1 to N-3 and bytes N+4 to 3N as Mapping layer bytes where sufficient transition density cannot be ensured, it is a requirement to support the STS-768-like scrambling mode.

#### 10.1.3 TFI-5 Link Error Monitoring (B1 byte)

TFI-5 links can be monitored using bit-interleaved (BIP-8) parity for transmission errors. The definition of the B1 byte is lifted directly from [14, 15, 24]. The B1 byte is located in the first column of the second row of the TFI-5 frame (see Figure 10.1) and carries a BIP-8 code using even parity. The BIP-8 is calculated over all the bytes in the previous TFI-5 frame after scrambling and is placed in the B1 byte of the current frame before scrambling.

In order to allow fault isolation the BIP-8 shall be calculated and inserted in the B1 byte by the source device of every TFI-5 link. The sink device of every TFI-5 link shall monitor the B1 byte.

#### 10.1.4 TFI-5 Link Deskew

All TFI-5 links in a system have a 2.488 Gbps standard rate (or optionally a 3.1104 Gbps rate) and are frequency locked to a common clock reference (TFIREFCK). In order to be able to properly time-slot exchange different client payloads from multiple TFI-5 links across the fabric interfaces, the frame boundaries of the source links shall be closely aligned.

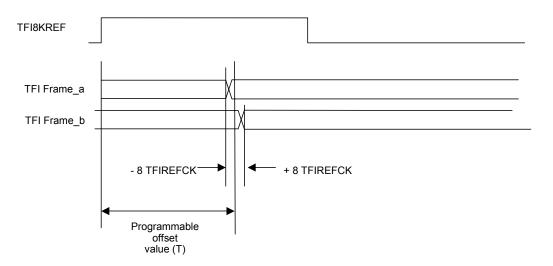

The start of a TFI-5 frame has a relative offset from the rising edge of TFI8KREF of (T) TFIREFCK cycles. T shall have a range of 1 full TFI8KREF cycle, and settable in increments of 8 TFIREFCK cycles or finer. The framer shall output the first <u>A2 byte (byte N+1)</u>of the frame at offset (T) with a timing accuracy of +/- 8 TFIREFCK cycles. Programmable offset (T) only applies to framers. The accuracy applies to both TFI-5 framers and switch fabrics.

Figure 10.5.2 TFI-5 frame offset timing

When a set of TFI links contains client payloads that are to be switched or multiplexed together, the sink device receiving these links shall be able to tolerate total (skew + relative\_wander/2) of at least 48 bytes. The arrival time between the earliest and latest arriving functional links at the sink device shall be less than 48 bytes.

Methods of achieving the standard TFI-5 alignment include pointer processing (retiming), multiplexing/inverse-multiplexing and mapping.

#### 10.2 TFI-5 Connection Layer

The TFI-5 Connection layer is defined for each of the N STS-1 time-slots (N = 48, 60) transported inside a TFI-5 frame. The Connection layer extends endto-end from the ingress framer to the egress framer. Optionally it provides for the following services for each STS-1 time-slot: supervision of errors and supervision of connectivity. The TFI-5 Connection layer uses the B2 and CM (Connection Monitoring) bytes as shown in Figures 10.1, 10.2 and 10.3 for these purposes.

#### 10.2.1 TFI-5 Connection Error Monitoring (B2 byte)

Connection error monitoring is optional. The N B2 bytes (see Figure 10.1) are carried in columns 1 to N (N = 48, 60) of the fifth row of the TFI-5 frame (see Figure 10.1). These are the same positions as the B2 bytes in a standard SONET/SDH frame. One B2 byte is allocated in each STS-1 timeslot for a Connection layer bit-error monitoring function. Each B2 byte is a Bit

Interleaved Parity 8 code (BIP-8) using even parity. Each BIP-8 code is computed over all bits of the previous frame of the STS-1 time-slot (before Link layer scrambling) except the associated STS-1 time-slot bytes located in columns 1 to 3\*N (N=48,60) of the first three rows of the TFI-5 frame. This BIP-8 code is placed in the B2 position of the current STS-1 time-slot. This is the same definition as for the standard SONET/SDH B2 bytes, where B2 is calculated over all bits of the Line OH and the Envelope Capacity of the previous STS-1 time-slot. If connection error monitoring is not used the B2 byte positions can be used by the TFI-5 Mapping layer. When connection error monitoring is implemented, a TFI-5 compliant device supporting this option shall provide means to disable B2 insertion at the source and B2 monitoring at the sink.

### 10.2.2 TFI-5 Connection Connectivity Monitoring (CM byte)

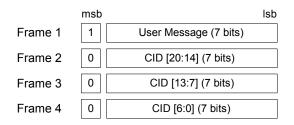

Connection connectivity monitoring is optional. The N CM bytes (see Figure 10.1) are carried in columns N+1 to  $2^{N}$  of the ninth row of the TFI-5 frame (N = 48, 60). These are the same positions as the M0/M1/Z2 bytes in a standard SONET/SDH frame. The CM format is shown in Figure 10.6. The CM bytes allow the monitoring of each constituent STS-1 time-slot for switch misconnections.

#### Figure 10.6 TFI-5 Connection Monitoring (CM) multi-frame format

The CM multi-frame spans four TFI-5 frames and carries a 7-bit User Message field and a 21-bit Connection Identifier (CID). Setting the most significant bit of the CM byte high shall identify the first frame in the CM multiframe. The most significant bit of the CM bytes of the 3 remaining frames shall be set low.

When CM is implemented, the CID field shall be configurable by system software at the TFI-5 source device and shall be readable by system software at the sink device to uniquely identify every constituent STS-1 time-slot within every TFI-5 link within a system.

When CM is implemented, the TFI-5 sink process shall be able to monitor the CID field by comparing its value to the value of the expected CID in order to detect misconnections at the switch fabric. Persistence shall be used to prevent bit errors from causing connection management mismatches.

If connection connectivity monitoring is not used the CM byte positions can be used by the TFI-5 Mapping layer. When connection connectivity monitoring is implemented, a TFI-5 compliant device supporting this option shall provide means to disable CM insertion at the source and CM monitoring at the sink.

#### 10.2.3 TFI-5 Connection forward defect indication

In case of a TFI-5 link failure (Loss of signal, out of frame) the down stream signal (connection and mapping layer) is set to "all ones". This condition can be detected by a "1111 1111" code in the CSI bytes if CSI is supported. The generation of client signal specific forward defect indications (e.g. SONET/SDH AIS, ODU-FDI) has to be done in the egress framer and is outside the scope of the TFI-5 specification.

#### 10.2.4 TFI-5 Connection open indication

If an STS-1 time-slot at the output of the TDM switch fabric is not connected to any input STS-1 time-slot all Connection and Mapping layer bytes of this time-slot shall be set to zero. This condition can be detected by a "0000 0000" code in the CM bytes if CM is supported. The generation of the client signal specific unequipped or open connection signal (e.g. STS-SPE/VC Unequipped, ODU Open Connection Indication) has to be done on the egress framer and is outside the scope of the TFI-5 specification.

#### 10.3 TFI-5 Mapping Layer

The TFI-5 Mapping layer provides the transport of the client signals over one or more TFI-5 Connection layer time-slots. All the bytes of the TFI-5 frame that are not used by the Link and Connection layer are available for the Mapping layer (see Table 10.1).

If bytes of the TFI-5 frame are not used by the Mapping, Connection or Link layer they shall be undefined except for the bytes 1 to N-3 in row 1 which shall be set to 0xF6 and the byte N+4 to 2\*N in row 1 which shall be set to 0x28.

The basic mapping scheme uses the SONET/SDH structure as defined in [14,15,24].

Non-SONET/SDH client signals can be transported across the TFI-5 by mapping them inside a concatenated group of SONET/SDH STS-3c SPEs/VC-4s. As all the TFI-5 signals are frame aligned and the payload frames are also aligned to a fixed pointer offset, no specific overhead for alignment is required within TFI-5 for transporting non-SONET/SDH clients.

| Туре                                                                                                                                 | Name         | Positions                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------|

| Bytes that belong to the Link                                                                                                        | A1           | Columns N-2 to N of the 1st row                |

| Layer                                                                                                                                | A2           | Columns N+1 to N+3 of the 1st row              |

|                                                                                                                                      | B1           | Column 1 of the 2 <sup>nd</sup> row            |

| Bytes that are optionally                                                                                                            | B2           | Columns 1 to N of the 5th row                  |

| used by the Connection layer<br>otherwise they may be used<br>by the Mapping Layer                                                   | СМ           | Columns N+1 to 2*N of the 9th row              |

| Bytes that are optionally<br>used for Client Status<br>Indication otherwise they<br>may be used for other<br>Mapping Layer functions | CSI          | Columns 2N+1 to 3*N of the 9 <sup>th</sup> row |

| Bytes that are optionally                                                                                                            | -            | Columns 1 to N-3 of the 1 <sup>st</sup> row    |

| used by the Mapping layer<br>otherwise they default to<br>0xF6, 0x28, respectively                                                   | -            | Columns N=4 to 2*N of the 1 <sup>st</sup> row  |

| Bytes that belong to the<br>Mapping layer for payload<br>transport                                                                   | All<br>other |                                                |

| Table 10.1 | Layer Assignments of | TFI-5 bytes |

|------------|----------------------|-------------|

|------------|----------------------|-------------|

#### TFI-5 Client Status Indication (CSI byte)

Client Status Indication is optional. The Client Status Indication (CSI) bytes provide a mechanism for the framer to report the status of client signals and/or to send commands to the switch fabric. This information can be used to control protection switching on the switch fabric. The encoding of CSI is unique for each client type as the alarms and conditions are dissimilar.

Client Status Indication (CSI) is provided in a single byte (E2 byte in SONET/SDH) for each STS-1. The CSI bytes (see Figure 10.1) are carried in columns 2\*N+1 to 3\*N of the ninth row of the TFI-5 frame (N = 48, 60). The CSI byte shall be provisioned to the E2 SONET/SDH Transport Overhead (TOH) byte. Tables 10.2 and 10.3 show the relevant byte assignments:

The following rules apply to the generation and interpretation of CSI when it is implemented:

1. CSI codes are assigned in order of alarm/condition priority. (High priority alarm/conditions have high CSI code values).

2. The framer sets the CSI codes in all time-slots associated with each client to the same value

#### 10.3.1 Mapping of SONET/SDH client signals

As a default SONET/SDH STS-1-SPE, STS-3c-SPE, STS-Nc-SPE, VC-4, VC-4Xc and higher order VC-3 are mapped into TFI-5 time-slots. For certain applications the transport of SONET/SDH TOH/SOH over the TFI-5 system can be supported.

10.3.1.1 Mapping of SONET/SDH STS-SPEs/higher order VCs clients

SONET/SDH STS-SPEs/higher order VCs clients are transported in a TFI-5 signal in the same way as they are transported in a STS-N/STM-N signal (see [14,15, 24]). An STS/AU structure, as defined in [5], is aligned to the TFI-5 frame, is constructed with the STS-SPE/higher order VC and pointer. (In this section, the term "STS/AU structure" is equivalent to SDH AU structure.) If the client is not already aligned to the TFI-5 frame or differs from the TFI-5 bit rate, pointer justification is required.

Note: SONET does not define a structure that is the equivalent to the SDH AU structure. In SONET terms the AU structure consists of the STS envelope capacity and the related H1, H2 and H3 pointer bytes in the TOH.

The STS/AU structure is mapped into the H1, H2, H3 pointer bytes and STS-SPE/VC payload area of the TFI-5 frame (see Figure 10.1).

An STS-1/AU-3 is mapped into a single TFI-5 time-slot.

- An STS-3c/AU-4 is mapped into 3 TFI-5 time-slots.

- Contiguous concatenated STS-3\*Nc/AU-4-Nc signals are mapped into 3\*N time-slots of a TFI-5 frame.

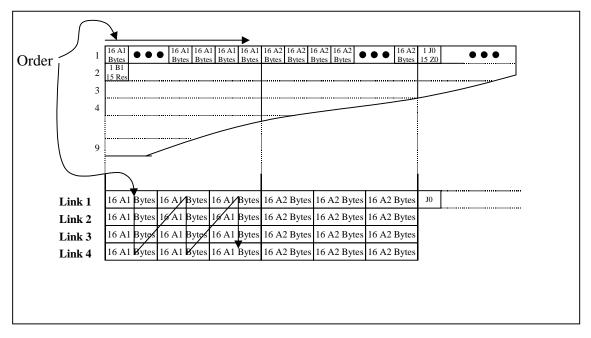

- A STS/AU structure that exceeds the capacity of a single TFI-5 signal is mapped to time-slots in several TFI-5 signals (disinter leaving). Figure 10.7 shows an example of mapping a STS-768 client onto a set of 16 TFI-5 links. After alignment to the TFI-5 frame, client bytes are taken in sets of 16 and placed onto TFI-5 links. Namely, bytes 1-16 are placed on TFI-5 link #1, bytes 17-32 on TFI-5 link #2, and bytes 241-256 on TFI-5 link #16. Figure 10.8 shows an example of mapping an STS-192/STM-64 client into a set of 4 TFI-5 links. After alignment to the TFI-5 frame, client bytes are taken in sets of 16 and placed onto TFI-5 links. Namely, bytes 1-16 are placed on link #1, bytes 17-32 are placed on link #2, and bytes 49-64 are placed on link #4. See ITU-T G.707.

A STS/AU structure can use time-slots in different TFI-5 signals even if the structure doesn't exceed the capacity of a TFI-5 signal.

TFI-5 requires neither special processing nor overhead to carry virtually concatenated clients.

- Virtual concatenated signals are treated as individual STS-SPE/VC signals.

- A TFI-5 system supports any standard mixture of non-concatenated, contiguous and virtually concatenated signals.

- The STS-SPE/VC transported in a TFI-5 signal can come from several OC-N/STM-N signals (e.g. 4 OC-12 interfaces are supported by a TFI-5).

- The time-slot assignment in the TFI-5 signal may follow the time-slot assignment in the OC-N/STM-N interface signal. This assignment is not followed, for example, for framers with time-slot interchange.

| Orde       | er | 1                 | 44                  | 45 46                      |      | 47            | 48             | 49             | 50             | 51             | 52             | 53                   |           | 96                   | 9   | 7 |  |

|------------|----|-------------------|---------------------|----------------------------|------|---------------|----------------|----------------|----------------|----------------|----------------|----------------------|-----------|----------------------|-----|---|--|

| 1          | Ł  | oytes ·····       | 6 reserved<br>bytes | 16 A1 16 A1<br>bytes bytes |      | 6 A1<br>oytes | 16 A1<br>bytes | 16 A2<br>bytes | 16 A2<br>bytes | 16 A2<br>bytes | 16 A2<br>bytes | 16 reserved<br>bytes |           | 16 reserved<br>bytes | 1 J |   |  |

| 2          |    | 1 B1<br>eserved   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 3          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 4          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 5          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 6          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 7          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| 8          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| <b>e</b> / |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

| N          |    |                   |                     |                            |      |               |                |                |                |                |                |                      |           |                      |     |   |  |

|            |    |                   | /                   | 1                          | /    |               |                |                |                |                |                |                      |           |                      |     |   |  |

| Link 1     |    | 16 reserved bytes |                     | 16 reserved bytes          | /16  | reserved      | bytes          | 16 A           | 2 bytes        | 16 re          | eserved bytes  | 5 16                 | 6 reserve | d bytes              | JO  |   |  |

| Link 2     |    | 16 reserved bytes |                     | 6 reserved bytes           | / 16 | reserved      | bytes          | 16 A           | 2 bytes        | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 3     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 A           | 2 bytes        | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 4     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 A           | 2 bytes        | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 5     |    | 16 reserved bytes | /                   | 6 reserved bytes           | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 6     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 7     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 8     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 9     |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 10    |    | 16 reserved bytes |                     | 16 reserved bytes          | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 11    |    | 16 reserved bytes |                     | 6 reserved bytes           | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | served bytes   | 5 16                 | 6 reserve | d bytes              |     |   |  |

| Link 12    |    | 16 reserved bytes |                     | 6 reserved bytes           | 16   | reserved      | bytes          | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 13    |    | 16 reserved bytes |                     | 6 reserved bytes           |      | 16 A1 byte    | es             | 16 rese        | rved bytes     | 16 re          | served bytes   | 5 16                 | 6 reserve | d bytes              |     |   |  |

| Link 14    |    | 16 reserved bytes |                     | 6 eserved bytes            |      | 16 A1 byte    | es             | 16 rese        | rved bytes     | 16 re          | served bytes   | s 16                 | 6 reserve | d bytes              |     |   |  |

| Link 15    |    | 6 reserved bytes  |                     | 6 reserved bytes           | 1    | 16 A1 byte    | es             | 16 rese        | rved bytes     | 16 re          | served bytes   | 5 16                 | 6 reserve | d bytes              |     |   |  |

| Link 16    |    | 16 reserved bytes |                     | 16 reserved bytes          |      | 16 A1 byte    | es             | 16 rese        | rved bytes     | 16 re          | eserved bytes  | s 16                 | 6 reserve | d bytes              |     |   |  |

Figure 10.7 Example disinterleaving showing byte ordering of an STS-768 frame into 16 TFI-5 links

#### Figure 10.8 Example of disinterleaving showing byte ordering of an STS-192 frame into 4 TFI-5 links

10.3.1.2 TOH/SOH bytes

SONET section/line overhead (TOH), SDH regenerator/multiplex section overhead (SOH) and AU pointer bytes may be transported via a TFI-5 frame using the bytes 1 to 3\*N in row 1 to 3 and 5 to 9 that are not used by the Link or Connection layers.

- The TOH/SOH bytes may be assigned to the same positions as in a standard SONET/SDH frame or use different positions (e.g. if the position is used by TFI-5). This is transparent to the TFI-5 signal and outside the scope of this implementation agreement.

- TOH/SOH bytes from a OC-N/STM-N signal may be distributed over several TFI-5 signals.

- A TFI-5 signal may transport TOH/SOH bytes from several OC-N/STM-N interfaces.

- Alignment of the TOH/SOH bytes to the TFI-5 clock is normally required. This alignment process is not standardized and outside the scope of the TFI-5 specification.

Note that the bytes in column 1 to 3\*N belong to specific STS-1 time-slots of the TFI-5 Connection layer and take the same route as these time-slots in a TFI-5 system.

#### 10.3.1.3 CSI coding for SONET/SDH clients

SONET/SDH status are encoded into the CSI byte as shown in Table 10.2 below.

| CSI Code  | Alarm/Condition                                   |

|-----------|---------------------------------------------------|

| 1111 1111 | TFI-5 Link Loss of Signal                         |

| 1111 1111 | TFI-5 Link Loss of Frame                          |

| 1111 1110 | Software Force - Away                             |

| 1111 1101 | Software AIS Insert                               |

| 1111 1100 | Software Force-To                                 |

|           | Loss of Signal (LOS)                              |

|           | Loss of Frame (LOF)                               |

|           | Section Trace Identifier Mismatch (TIM-S)         |

|           | Line AIS (AIS-L)                                  |

|           | Signal Fail (SF-L) / Excessive BER (EXC-MS)       |

|           | Path AIS (AIS-P) / Concat AIS (AISC-P)            |

|           | Loss of Pointer (LOP) / Loss of Concat Ind (LOPC) |

|           | Unequipped Signal Label (UNEQ)                    |

|           | Path Trace Identifier Mismatch (TIM-P)            |

|           | Payload Label Mismatch (PLM)                      |

|           | Signal Fail (SF-P) / Excessive BER (EXC-P)        |

|           | PDI-P code 28                                     |

|           | PDI-P code 27                                     |

|           |                                                   |

|           | PDI-P code 1                                      |

|           | Signal Degrade (SD-P)                             |

|           | Signal Degrade (SD-L)                             |

| 0000 0001 | No Alarm                                          |

| 0000 0000 | Reserved                                          |

## Table 10.2 Client Status Indication (CSI) Coding for SONET/SDH clients

• The blank CSI code values are user programmable.

• Above each alarm/condition with a blank code point, there may be a user defined CSI alarm/condition entry. These may be used for augmenting the listed alarms/conditions with other simultaneously occurring alarms/conditions (e.g. Path alarm with SD-L).

• Generation of the CSI byte for alarms/conditions with blank code points are application dependent.

#### 10.3.2 Mapping of OTN clients

The ODU1, ODU2 and ODU3 signals of the OTN (see [6]) are supported by a TFI-5 system. ITU-T defines the use of Virtual Concatenation for the transport of an OTN entity over SDH paths. Diverse routing of the VC-4-Xv's (X=17,68) requires large deskew buffers and H4 byte processing. Within the TFI-5 system, however, the differential delay between the different VC-4's (members of a group) is limited to 48 bytes. Therefore, the transport of an ODUk through a TFI-5 system does not require the implementation <u>of any virtual concatenation mechanisms such as differential delay compensation and H4 processing as defined in [14,15, 24]. Table 10.3 shows the C-4-Xc structure used for mapping and the number of STS-3c/VC-4's time-slots required for transport of the different ODUk signals within the TFI-5 system.</u>

| Client<br>Signal | Nominal Bit Rate<br>(Mb/Sec) | ITU-T<br>Mapping | # STS-3c/VC-<br>4's time-slots<br>required for<br>transport<br>within TFI-5<br>system |

|------------------|------------------------------|------------------|---------------------------------------------------------------------------------------|

| ODU1             | 2498.775126                  | C-4-17c          | 17                                                                                    |

| ODU2             | 10037.273924                 | C-4-68c          | 68                                                                                    |

| ODU3             | 40319.218983                 | C-4-272c         | 272                                                                                   |

# Table 10.3 Transport of OTN entities over TFI-5 link(s) via STS-3c/VC-4 Time-slots

#### 10.3.2.1 Mapping of a ODU1 client signal

The transport of a ODU1 client signal across a TFI-5 shall be done by mapping the ODU1 into a C-4-17c as defined in [7] and by transporting this concatenated container over 17 STS-3c-SPE/VC-4. The active offset of the VC-4 shall be 522 (pointer offset value) for ODU1 mappings.

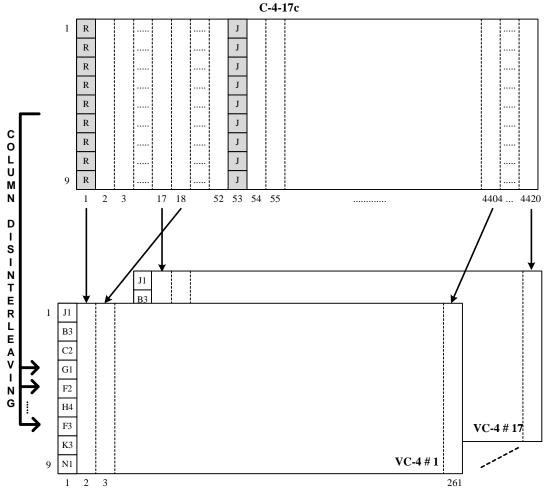

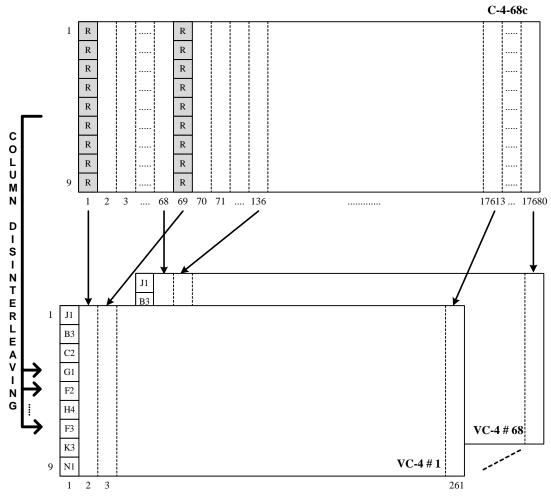

Figure 10.4.2 details how the C-4-17c structure carrying an ODU1 after being mapped is transported through a TFI-5 system using 17 STS-3c/VC-4 timeslots: the C-4-17c concatenated structure is column disinterleaved over the 17 STS-3c/VC-4 time-slots. The 17 VC-4's generated in this way are <u>aligned</u> to the pointer value of 522 and then transported over any combination of TFI-5 links. The first column of the STS-3c/VC-4 time-slots (equivalent bytes J1, B3, C2, etc... in a SONET/SDH frame) are unused (see Figure 10.4.2) and have undefined value. The STS-3c/VC-4 time-slots can be striped over multiple TFI-5 links, or multiplexed and carried over 1 or more links. See Section 10.2.2 for information on the Connectivity Monitoring (CM byte).

Figure 10.4.2: Disinterleaving of a C-4-17c for transport over TFI-5 link(s) using 17 STS-3c/VC-4 time-slots

Figure 10.4.3 details the reconstruction of the C-4-17c from the 17 STS-3c/VC-4 time-slots (received from any combination of TFI-5 links). The 17 STS-3c/VC-4 time-slots, are column interleaved to obtain the C-4-17c.

Figure 10.4.4: Interleaving of a C-4-17c from 17 STS-3c/VC-4 time-slots

10.3.2.2 Mapping of a ODU2 client signal

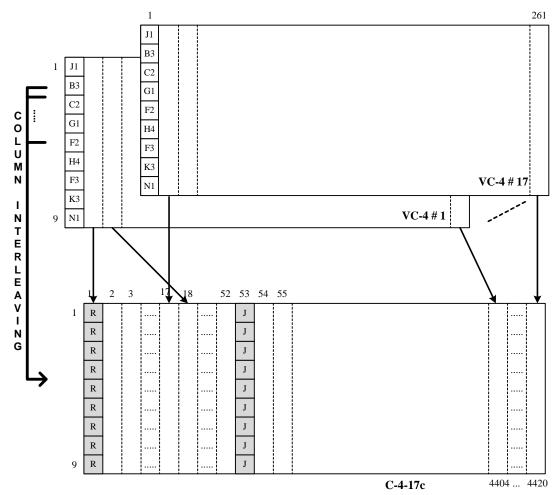

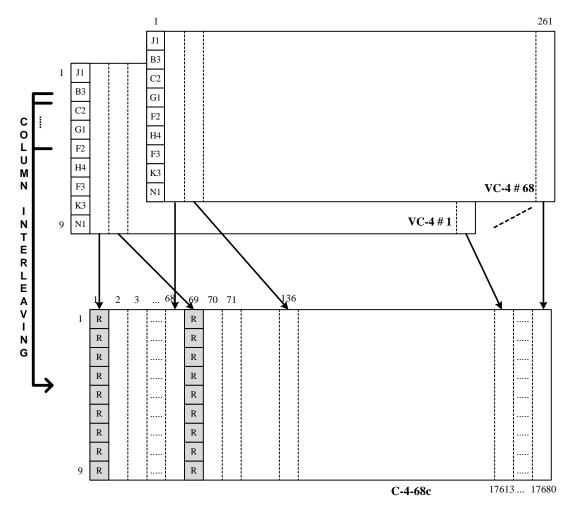

The transport of a ODU2 client signal across a TFI-5 shall be done by mapping the ODU2 into a C-4-68c as defined in [7] and by transporting this concatenated container over 68 STS-3c-SPE/VC-4. The active offset of the VC-4 shall be 522 (pointer offset value) for ODU2 mappings.

Figure 10.4.5 details how the C-4-68c structure carrying an ODU2 after being mapped is transported through a TFI-5 system using 68 STS-3c/VC-4 timeslots: the C-4-68c concatenated structure is column disinterleaved over the 68 STS-3c/VC-4 time-slots. The 68 STS-3c/VC-4's generated in this way are aligned to the pointer value of 522 and then transported over any combination of TFI-5 links. Columns 3N+N (N=48,60) of the TFI-5 frame (Equivalent bytes J1, B3, C2, etc... in a SONET/SDH frame) are unused (see Figure 10.1) and have undefined value. The STS-3c/VC-4 time-slots can be striped over multiple TFI-5 links, or multiplexed and carried over 4 or more links. For OTN client mappings, the POH overhead bytes are undefined. See Section 10.2.2 for information on the Connectivity Monitoring (CM byte).

Figure 10.4.5: Disinterleaving of a C-4-68c for transport over TFI-5 link(s) using 64 STS-3c/VC-4 time-slots

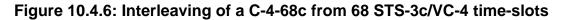

Figure 10.4.6 details the reconstruction of the C-4-68c from the 68 STS-3c/VC-4 time-slots (received from any combination of TFI-5 links). The 68 STS-3c/VC-4 time-slots, are column interleaved to obtain the C-4-68c.

#### 10.3.2.3 Mapping of a ODU3 client signal

The transport of a ODU3 client signal across a TFI-5 shall be done by mapping the ODU3 into a C-4-Xc (a possible mapping is given in Appendix A.1) and by transporting this concatenated container over n STS-3c-SPE/VC-4. The active offset of the VC-4 shall be 522 (pointer offset value) for ODU3 mappings.

10.3.2.4 CSI Coding for OTN clients

OTN status is encoded into the CSI byte as shown in Table 10.4 below.

| CSI Code  | Alarm/Condition                                    |

|-----------|----------------------------------------------------|

| 1111 1111 | TFI-5 Link Loss of Signal                          |

| 1111 1111 | TFI-5 Link Loss of Frame                           |

| 1111 1110 | Software Force - Away                              |

| 1111 1101 | Software AIS Insert                                |

| 1111 1100 | Software Force-To                                  |

|           | Loss of Signal (LOS)                               |

|           | OTUk AIS (AIS-OTUk)                                |

|           | Loss of Frame (LOF)                                |

|           | Loss of Multi-Frame (LOM)                          |

|           | OTUk Trail Trace Identifier Mismatch<br>(TIM-OTUk) |

|           | OTUk Signal Fail / Excessive BER (SF-<br>OTUk)     |

|           | ODU Open Connection Indication (OCI-<br>ODUk)      |

|           | ODUk Locked Defect (LCK-ODUk)                      |

|           | ODUk AIS (AIS-ODUk)                                |

|           | ODUk Trail Trace Identifier Mismatch<br>(TIM-ODUk) |

|           | ODUk Signal Fail / Excessive BER (SF-<br>ODUk)     |

|           | ODUk Signal Degrade (SD-ODUk)                      |

|           | OTUk Signal Degrade (SD-ODUk)                      |

| 0000 0001 | No Alarm                                           |

| 0000 0000 | Reserved                                           |

#### Table 10.4: Client Status Indication (CSI) Coding for OTN clients.

• The blank CSI code values are user programmable.

• Above each alarm/condition with a blank code point, there may be a user defined CSI alarm/condition entry. These may be used for augmenting the listed alarms/conditions with other simultaneously occurring alarms/conditions

• Generation of the CSI byte for alarms/conditions with blank code points are application dependent.

#### 10.3.3 Mapping of Ethernet clients

10 GE signals as defined in [8] are supported by a TFI-5 system.

#### 10.3.3.1 Mapping of 10 GbE LAN PHY

The transport of a 10 GbE LAN PHY client signal across a TFI-5 shall be done by mapping the 10 GbE LAN PHY into a C-4-Xc (a possible mapping is given in Appendix A.2) and by transporting this concatenated container over n STS-3c-SPE/VC-4. The active offset of the VC-4 shall be 522 (pointer offset value) for 10GE LAN PHY mappings. For 10 GbE LAN PHY mappings, the POH overhead bytes are undefined.

10.3.3.2 Mapping of 10 GbE WAN PHY

The 10 GbE WAN PHY is based on a OC-192/STM-64 signal with a STS-192c-SPE/VC-4-64c. It is treated like standard SONET/SDH signals in a TFI-5 system.

## 11. Electrical Interface Definition

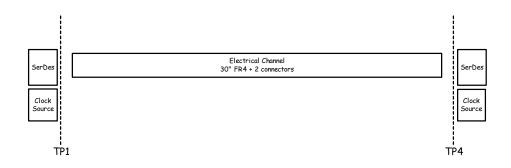

This section describes the signaling that allows for TFI-5 link operation at 2.488 Gbps to 3.11 Gbps. The specification defines the characteristics required to communicate between an TFI-5 driver and an TFI-5 receiver using copper signal traces across a communication backplane consisting of approximately 30 inches (76 cm) of total PCB trace including two connectors. The characteristic impedance of the signal traces is nominally 100 ohms differential. Connections are point-to-point and signaling is unidirectional. TFI-5 devices from different manufacturers shall be inter-operable.

# Figure 11.1 TFI-5 application model for the pure electrical interface, also called the intra-rack system.

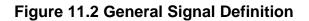

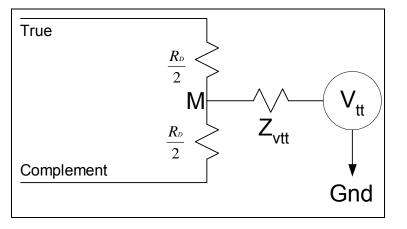

Differential signaling conventions are shown in Figure 11.2 below. The differential amplitude represents the value of the voltage between the true and complement signals. Peak-Peak voltage is defined as  $2^*(V_{high} - V_{low})$ . The common mode voltage is the average of  $V_{high}$  and  $V_{low}$ .

#### **11.1 Differential Output Characteristics**

Output parameters that can be derived from other specified parameters may not be explicitly specified. The use of external DC blocking capacitors is optional. Any loss or jitter caused by these capacitors must be accounted for as part of the allocation for the printed circuit board on which the capacitors reside.

The frequency dependent attenuation of the inter-connection media degrades the signal and thus produces inter-symbol interference or data dependent jitter. Given this and the receiver eye mask, transmit emphasis shall be required.

All TFI-5 output drivers shall meet all the parameters of Table 11.1. The receiver eye mask is provided in Figure 11.6 and Table 11.3 and assumes the TFI-5 channel model (See the Channel Model Section below). This allows maximum design flexibility while still guaranteeing interoperability. Transmitter interoperability shall be tested using the methodology described in the OIF CEI IA section 2.2.3

| Symbol            | Parameter                         | Max  | Min  | Units | Comments                                                                                                                                                                                                                                                                                                               |

|-------------------|-----------------------------------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vod               | Output<br>Differential<br>Voltage | 1.4  |      | Vppd  | Min is implied given channel and receiver eye mask                                                                                                                                                                                                                                                                     |

| Voh               | Output High<br>Voltage            | 2.3  |      | V     | AC coupled. If DC coupled parameter can be calculated from Vod and Vcm.                                                                                                                                                                                                                                                |

| Vol               | Output Low<br>Voltage             |      | -0.1 | V     | AC coupled. If DC coupled parameter can be calculated given Vod and Vcm.                                                                                                                                                                                                                                               |

| V <sub>CM</sub>   | Output Common<br>Mode Voltage     | Vtt  | 0.62 | V     | $(V_{high} + V_{low}) / 2$ . When using a load of<br>Figure 11.3 with 1.05V< $V_{tt}$ <1.35, 75<<br>$R_D$ <125 ohms, 0 <zvtt<30 ohms.<br="">Ground in Figure 11.3 is to be the<br/>same potential as the driver ground.<br/>(see note 1) Parameter is unspecified<br/>if DC blocking capacitors are present.</zvtt<30> |

| T <sub>DRF</sub>  | Driver Rise/Fall<br>Time          |      | 50   | ps    | At 20% - 80% into 100 ohm load                                                                                                                                                                                                                                                                                         |

| IDSHORT           | Short<br>Circuit Current          | 70   | -70  | mA    | Resulting DC current from a forced voltage when the Tx is powered on or off. See note 2 and Figure 11.5.                                                                                                                                                                                                               |

| UI <sub>D</sub>   | Unit Interval                     | 402  | 321  | ps    | 2.488 Gbps to 3.11 Gbps,<br>±100 ppm                                                                                                                                                                                                                                                                                   |

| R <sub>SE</sub>   | Single-ended output impedance     | 62.5 | 37.5 | Ohm   | at DC                                                                                                                                                                                                                                                                                                                  |

| R <sub>D</sub>    | Differential<br>Impedance         | 125  | 75   | Ohm   | at DC                                                                                                                                                                                                                                                                                                                  |

| RL <sub>SE</sub>  | Single-ended<br>return loss       |      | 7.5  | dB    | From 0.004*baud rate to 0.75*baud rate                                                                                                                                                                                                                                                                                 |

| RL <sub>OUT</sub> | Differential return loss          |      | 7.5  | dB    | From 0.004*baud rate to 0.75*baud rate                                                                                                                                                                                                                                                                                 |

#### Table 11.1: TFI-5 Output Characteristics

#### <u>Notes</u>

- 1. The Vtt values take into account a maximum of +/-50mv ground shift between transmit and receiver. If higher values in ground shift are within the system, then AC coupling should be used.

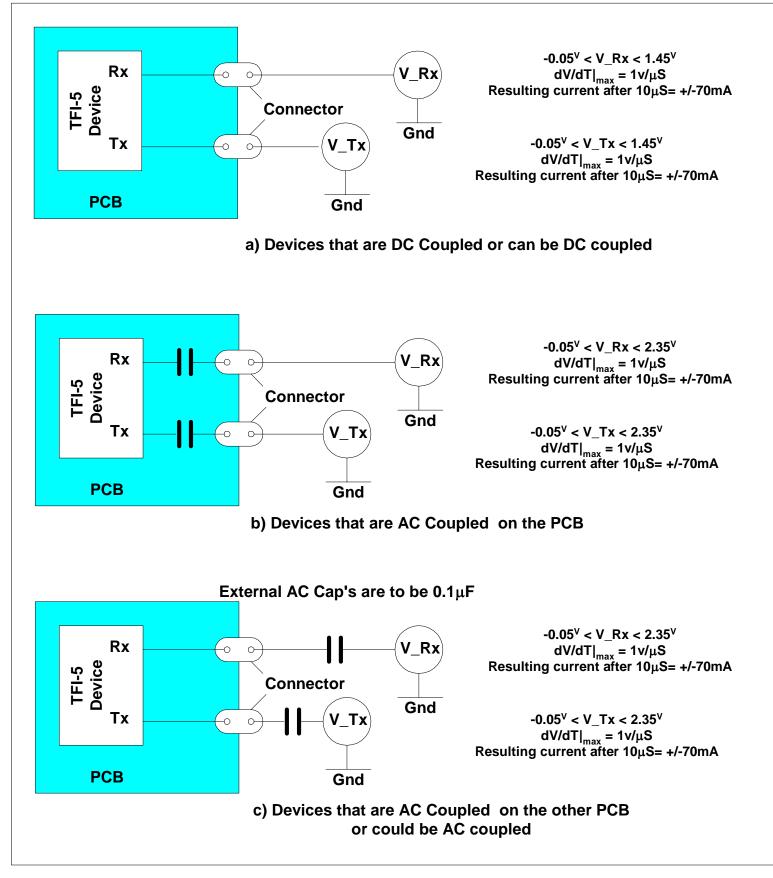

- Current after 10μS to any voltage between –0.05 and 1.45V if DC coupling allowed or required, or between –0.05 and 2.35V if AC coupling allowed or required. The time 0μS is defined as the instant when the applied voltage is turned on. dV/dT changes within this range are to be below 1V/μS. See Figure 11.5 for more info.

#### **11.2 Differential Input Characteristics**

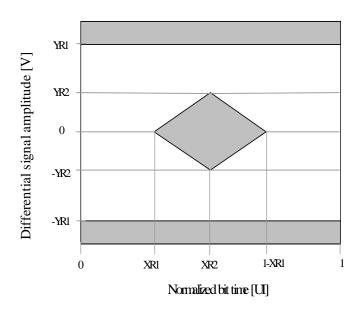

All TFI-5 input receivers shall meet all the parameters of Table 11.2, Figure 11.3 and Figure 11.5. Also the receive eye mask of Table 11.3 and Figure 11.6 must be met.

| Symbol                                    | Parameter                           | Max  | Min   | Units                                                                                                                       | Comments                                                                                                                                                         |

|-------------------------------------------|-------------------------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>tt</sub>                           | Termination<br>Voltage              | 1.30 | 1.10  | V                                                                                                                           | Parameter unspecified if DC blocking<br>capacitors are present                                                                                                   |