# **COMMON MANAGEMENT INTERFACE SPECIFICATION (CMIS)**

Rev 3.0 September 18, 2018 (From QSFP-DD MSA)

## **OIF LEGAL NOTICES**

#### THIRD PARTY SPECIFICATION

THIS [STANDARD/SPECIFICATION] (THE "SPECIFICATION") WAS DEVELOPED, APPROVED, AND ORIGINALLY PUBLISHED BY **QSFP-DD MSA** (WWW.QSFP-DD.COM/), WHICH HAS CONCLUDED ITS WORK ON THIS SPECIFICATION. THE SPEFICIATION IS BEING PROVIDED BY OPTICAL INTERNETWORKING FORUM (OIF), WITH PERMISSION FROM QSFP-DD MSA, AS A CONVENIENCE TO OIF MEMBERS AND VISITORS. OTHER THAN THE AFOREMENTIONED PERMISSION, OIF IS NOT AFFILIATED WITH AND DOES NOT ENDORSE QSFP-DD MSA OR THIS SPECIFICATION, AND PUBLICATION OF THIS SPECIFICATION SHOULD NOT BE CONSTRUED AS AN ENDORSEMENT. FOR INFORMATION ABOUT QSFP-DD MSA, PLEASE CONTACT INFO@QSFP-DD.COM.

BECAUSE THIS IS A THIRD PARTY SPECIFICATION, THE SPECIFICATION WAS NOT REVIEWED OR APPROVED UNDER THE OIF DEVELOPMENT PROCESS, AND IS NOT GOVERNED BY THE OIF INTELLECTUAL PROPERTY RIGHTS ("IPR") POLICY. ACCORDINGLY, NEITHER OIF NOR ANY OF ITS MEMBERS ACTING IN THAT CAPACITY HAVE COMMITTED TO GRANTING ANY LICENSES OR MADE ANY OTHER COMMITMENTS OR DISCLOSURES REGARDING THIS SPECIFICATION OR ANY PATENT CLAIMS OR OTHER IPR THAT MIGHT BE INFRINGED BY IMPLEMENTATION OF THE SPECIFICATION.

## **NO WARRANTIES**

THIS SPECIFICATION IS BEING OFFERED AND PROVIDED "AS IS" AND WITHOUT ANY WARRANTY WHATSOEVER, AND IN PARTICULAR, ANY WARRANTY OF NON-INFRINGEMENT IS EXPRESSLY DISCLAIMED. THE AUTHORS OF THIS SPECIFICATION HAVE DISCLAIMED ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS SPECIFICATION. TO THE GREATEST EXTENT PERMITTED BY LAW, OIF HEREBY DISCLAIMS ALL EXPRESS, IMPLIED AND STATUTORY WARRANTIES, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF TITLE, NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. WITHOUT LIMITING THE FOREGOING, OIF DOES NOT WARRANT THAT THIS DOCUMENT SPECIFICATION IS COMPLETE OR WITHOUT ERROR AND DISCLAIMS ANY WARRANTIES TO THE CONTRARY, NOTHING IN THIS SPECIFICATION CREATES ANY WARRANTIES WHATSOEVER REGARDING THE SUITABILITY OR NON-SUITABILITY OF A PRODUCT OR A SERVICE FOR CERTIFICATION UNDER ANY CERTIFICATION PROGRAM OF OIF OR ANY THIRD PARTY. ANY USE OF THIS SPECIFICATION SHALL BE MADE ENTIRELY AT THE IMPLEMENTER'S OWN RISK, AND NEITHER OIF, NOR ANY OF ITS MEMBERS OR SUBMITTERS OR THEIR RELATED PARTIES, SHALL HAVE ANY LIABILITY WHATSOEVER TO ANY IMPLEMENTER OR THIRD PARTY FOR ANY DAMAGES OF ANY NATURE WHATSOEVER, DIRECTLY OR INDIRECTLY, ARISING FROM THE USE OF THIS SPECIFICATION.

#### **PERMISSIONS**

ACCORDING TO THE SPECIFICATION, YOU ARE AUTHORIZED TO DOWNLOAD, REPRODUCE, AND DISTRIBUTE THIS SPECIFICATION. ALL OTHER RIGHTS ARE RESERVED. THE PROVISION OF THIS SPECIFICATION SHOULD NOT BE CONSTRUED AS THE GRANTING OF ANY RIGHT TO PRACTICE, MAKE, USE, OR OTHERWISE DEVELOP PRODUCTS THAT ARE BASED ON THE SPECIFICATION. ANY AND ALL IPR RELATED TO THIS SPECIFICATION AND THE DESIGNS DISCLOSED WITHIN, EXCEPT FOR THE RIGHTS EXPRESSLY MENTIONED ABOVE, ARE RESERVED BY THE RESPECTIVE OWNERS OF THE RELEVANT IPR.

#### **PATENTS**

OIF DRAWS ATTENTION TO THE FACT THAT THE SPECIFICATION OR ELEMENTS THEREOF MAY BE THE SUBJECT OF IPR (OF THE DEVELOPING ORGANIZAZION, ITS MEMBERS OR CONTRIBUTORS, OR THIRD PARTIES), WHICH MAY BE INFRINGED BY IMPLEMENTATION OF THE SPECIFICATION OR ELEMENTS THEREOF. OIF IS NOT AND SHALL NOT BE RESPONSIBLE FOR IDENTIFYING ANY OR ALL SUCH IPR.

#### THIRD PARTY RIGHTS

NOTWITHSTANDING AND WITHOUT LIMITING THE GENERALITY OF THE FOREGOING, OIF ASSUMES NO RESPONSIBILITY TO COMPILE, CONFIRM, UPDATE OR MAKE PUBLIC ANY THIRD PARTY ASSERTIONS OF PATENT OR OTHER IPR THAT MIGHT NOW OR IN THE FUTURE BE INFRINGED BY AN IMPLEMENTATION OF THIS SPECIFICATION IN ITS CURRENT, OR IN ANY FUTURE FORM. IF ANY SUCH RIGHTS ARE ASSERTED OR ARE DESCRIBED IN THE SPECIFICATION OR BY OIF, OIF TAKES NO POSITION AS TO THE VALIDITY OR INVALIDITY OF SUCH ASSERTIONS, OR THAT ALL SUCH ASSERTIONS THAT HAVE OR MAY BE MADE ARE SO DESCRIBED.

BY REVIEWING THIS SPECIFICATION, YOU ACKNOWLEDGE AND AGREE TO ALL OF THE FOREGOING, AND AGREE TO INDEMNIFY AND HOLD HARMLESS OIF AND ITS EMPLOYEES, OFFICERS, DIRECTORS AND MEMBERS FROM ANY CLAIMS, DAMAGES, LOSSES, COSTS, AND EXPENSES ARISING FROM OR IN CONNECTION WITH YOUR USE OF THE SPECIFICATION.

# Common Management Interface Specification

for

## 8X/16X PLUGGABLE TRANSCEIVERS

Rev 3.0 September 18, 2018

Abstract: This document defines the Common Management Interface Specification (CMIS) for pluggable modules such as QSFP Double Density (QSFP-DD), OSFP and COBO. This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules and transceivers.

## POINTS OF CONTACT:

| Tom Palkert              | Mark Nowell           | Scott Sommers              |

|--------------------------|-----------------------|----------------------------|

| Technical Editor         | Co-Chair              | Co-Chair                   |

| Molex                    | Cisco                 | Molex                      |

| 2222 Wellington Court    | 170 West Tasman Dr    | 2222 Wellington Court      |

| Lisle, IL 60532-1682     | San Jose, CA 95134    | Lisle, IL 60532-1682       |

| Ph: +1 (952)-200-8542    | Ph: +1 (613)-254-3391 | Ph: +1 (630)-527-4317      |

| tom.palkert at molex.com | mnowell at cisco.com  | scott.sommers at molex.com |

## Limitation on use of Information:

This specification is provided "AS IS" with NO WARRANTIES whatsoever and therefore the provision of this specification does not include any warranty of merchantability, noninfringement, fitness for a particular purpose, or any other warranty otherwise arising out of any proposal, specification or sample. The authors further disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

## Permissions:

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The provision of this document should not be construed as the granting of any right to practice, make, use or otherwise develop products that are based on the document. Any and all IP rights related to this document and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the respective owners of those IP rights.

# Change History:

| Revision | Date         | Changes              |

|----------|--------------|----------------------|

| 1.0      | June 2017    | First public release |

| 2.7      | Feb 27 2018  | Working draft        |

| 3.0      | September 18 | CMIS public release  |

# Foreword

The development work on this specification was done by the QSFP-DD, OSFP and COBO advisory group. Further revisions of the CMIS shall be backwards compatible to Revision 3.0.

# CONTENTS

| 1 Management Interface                                                      | 5   |

|-----------------------------------------------------------------------------|-----|

| 1.1 Introduction                                                            | 5   |

| 1.2 Definitions and Acronyms                                                | 6   |

| 1.3 Management Interface Timing Specifications and Protocol                 | 8   |

| 1.3.1 Introduction                                                          |     |

| 1.3.2 Management Interface Timing Specification                             |     |

| 1.3.3 Signal Interface                                                      |     |

| 1.3.4 Serial Interface Protocol                                             |     |

| 1.3.5 Read/Write Operations                                                 |     |

| 1.3.6 Timing for Soft Control and Status Functions                          | 16  |

| 1.4 Module State Machine                                                    |     |

| 1.4.1 Module Init Modes                                                     |     |

| 1.4.2 Module Power Mode and Module and Data Path State Machine interactions |     |

| 1.4.3 Reset State                                                           |     |

| 1.4.4 MgmtInit State<br>1.4.5 ModuleLowPwr State                            |     |

| 1.4.6 ModulePwrUp state                                                     |     |

| 1.4.7 ModuleReady State                                                     |     |

| 1.4.8 ModulePwrDn State                                                     |     |

| 1.4.9 Fault State                                                           | 24  |

| 1.5 Application/Data Path Overview                                          | 24  |

| 1.5.1 Host Electrical and Module Media Lane Background                      |     |

| 1.5.2 Application Advertising Methodology                                   |     |

| 1.5.3 Data Path State Machine                                               |     |

| 1.5.4 Control Set Overview                                                  | 37  |

| 1.5.5 Signal Integrity Control Field Background                             | 40  |

| 1.6 Interrupt Flag Conformance per State                                    | 42  |

| 1.6.1 Module Flag Conformance per State                                     | 42  |

| 1.6.2 Lane-Specific Flag Conformance per State                              | 43  |

| 1.7 Module Memory Map                                                       |     |

| 1.7.1 Register default values                                               |     |

| 1.7.2 Lower Page 00h                                                        |     |

| 1.7.3 Upper Page 00h                                                        |     |

| 1.7.4 Upper Page 01h                                                        |     |

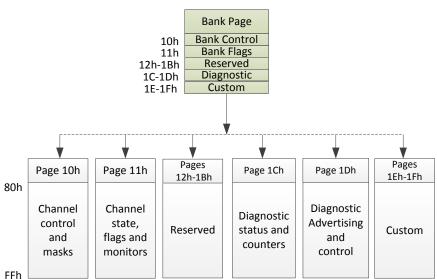

| 1.7.5 Upper Page 02h<br>1.7.6 Upper Page 10h                                |     |

| 1.7.7 Upper Page 11h                                                        |     |

|                                                                             |     |

| 2 Appendix A - Form Factor Signal Names                                     | 115 |

| 3 Appendix B - Host-Module Initialization Example Flows                     | 115 |

| 3.1 Software Init Mode (INITMODE=1) Default                                 | 116 |

| 3.2 Module power-down sequence example                                      | 119 |

| 4 Appendix C - Media advertising codes                                      | 122 |

|        |     | Passive copper cable assembly state behaviors                               |    |

|--------|-----|-----------------------------------------------------------------------------|----|

|        |     | Active module state behaviors                                               |    |

|        |     | Module State Changed flag behaviors                                         |    |

|        |     | Module Application Advertising format for one application                   |    |

|        |     | 400GBASE-DR4 Application Advertising Example                                |    |

| Table  | 6-  | 400G-SR8 Transceiver Application Advertising Example                        | 30 |

|        |     | 8x50G AOC Application Advertising Example                                   |    |

|        |     | Data path state behaviors for active modules                                |    |

| Table  | 9-  | Data Path State Change flag behaviors for active modules                    | 34 |

| Table  | 10- | Control field dependency on Explicit Control bit                            | 38 |

| Table  | 11- | Tx Input Eq control relationship to Tx Adaptive Input Eq Enable             | 40 |

|        |     | Fixed Tx Input Equalization Codes                                           |    |

| Table  | 13- | Rx Output Emphasis Codes                                                    | 41 |

| Table  | 14- | Rx Output Amplitude Codes                                                   | 41 |

|        |     | Module Flag Conformance                                                     |    |

|        |     | Lane-Specific Flag Conformance                                              |    |

|        |     | Lower Page Overview (Lower Page)                                            |    |

|        |     | Identifier and Status Summary (Lower Page)                                  |    |

|        |     | Module State Encodings                                                      |    |

|        |     | Lane Flag Summary (Lower Page)                                              |    |

|        |     | Module Flags (Lower Page, active modules only)                              |    |

|        |     | Module Monitors (Lower Page, active modules only)                           |    |

|        |     | Module Global and Squelch Mode Controls (Lower Page, active modules only)   |    |

|        |     | Module Level Flag Masks (Lower Page, active modules only)                   |    |

|        |     | Byte 85 Module Type Encodings                                               |    |

|        |     | Application Advertising Fields (Lower page)                                 |    |

|        |     | Upper Page 00 Overview (Page 00h)                                           |    |

|        |     | Identifiers (Page 00h)                                                      |    |

|        |     | Date Code (Page 00h)                                                        |    |

|        |     | Module Power Class and Max Power (Page 00h)                                 |    |

|        |     | Cable Assembly Length (Page 00h)                                            |    |

|        |     | Media Connector Type (Page 00h)                                             |    |

|        |     | Copper Cable Attenuation (Page 00h)                                         |    |

|        |     | Media lane interface implementation (Page 00h)                              |    |

|        |     | Far end cable lane groups advertising codes (Page 00h)                      |    |

|        |     | Media Interface Technology encodings                                        |    |

|        |     | Upper Page 01 Overview (Page 01h)                                           |    |

|        |     |                                                                             |    |

|        |     | Module Firmware and Hardware Revisions (Page 01h)                           |    |

|        |     | Supported Fiber Link Length (Page 01h)                                      |    |

|        |     | Implemented Management Interface Features Advertising (Page 01h)            |    |

|        |     | State Duration Encoding (Page 01h)                                          |    |

|        |     | Module Characteristics Advertising (Page 01h)                               |    |

|        |     | Implemented Controls Advertisement (Page 01h)                               |    |

|        |     | Implemented Flags Advertisement (Page 01h)                                  |    |

|        |     | Implemented Monitors Advertisement (Page 01h)                               |    |

|        |     | Implemented Signal Integrity Controls (Page 01h)                            |    |

|        |     | Media Lane Assignment Advertising (Page 01h)                                |    |

|        |     | Additional Application Advertising Fields (Page 01h)                        |    |

|        |     | Upper Page 02 Overview (Page 02h)                                           |    |

|        |     | Module-Level Monitor Thresholds (Page 02h)                                  |    |

|        |     | Lane-specific Monitor Thresholds (Page 02h, active modules only)            |    |

|        |     | Upper Page 16 Overview (Page 10h)                                           |    |

|        |     | Data Path Power control (Page 10h, active modules only)                     |    |

|        |     | Lane-specific Control Fields (Page 10h, active modules only)                |    |

|        |     | Staged Control Set 0, Apply Controls (Page 10h, active modules only)        | 83 |

| Table  | 56- | Staged Control Set 0, Application Select Controls (Page 10h, active modules |    |

| only). |     |                                                                             | 84 |

| Table  | 57- | Staged Control Set 0, Tx Controls (Page 10h, active modules only)           | 85 |

| Table  | 58- | Staged Control Set 0, Rx Controls (Page 10h, active modules only)           | 86 |

|          | - Staged Control Set 1, Apply Controls (Page 10h, active modules only)           | 88  |

|----------|----------------------------------------------------------------------------------|-----|

|          | - Staged Control Set 1, Application Select Controls (Page 10h, active modules    |     |

|          |                                                                                  |     |

|          | - Staged Control Set 1, Tx Controls (Page 10h, active modules only)              |     |

|          | - Staged Control Set 1, Rx Controls (Page 10h, active modules only)              |     |

|          | - Lane-Specific Flag Masks (Page 10h, active modules only)                       |     |

|          | - Upper Page 17 Overview (Page 11h)                                              |     |

|          | - Data Path State Indicator, per lane (Page 11h) (see Table 66)                  |     |

|          | - Data Path State Indicator Encodings                                            |     |

|          | - Lane-Specific State Changed Flags (Page 11h)                                   |     |

|          | - Lane-Specific TX Flags (Page 11h)                                              |     |

|          | - RX Flags (Page 11h, active modules only)                                       |     |

|          | - Lane-Specific Monitors (Page 11h, active modules only) 1                       |     |

|          | - Configuration Error Code registers (Page 11h, active modules only) 1           |     |

|          | - Configuration Error Codes (Page 11h, active modules only) 1                    | 04  |

|          | - Indicators for Active Control Set, Application Selected (Page 11h, active      | _   |

|          | only)1                                                                           |     |

|          | - Indicators for Active Control Set, Tx Controls (Page 11h, active modules only) |     |

|          |                                                                                  |     |

|          | - Indicators for Active Control Set, Rx Controls (Page 11h, active modules only) |     |

|          |                                                                                  | 07  |

|          | - Module Media Lane to Module Media Wavelength and Fiber mapping (Page 11h,      |     |

|          | odules only)1                                                                    |     |

|          | - Form Factor Signal Name Associations                                           |     |

|          | - Module Host Electrical Interfaces Codes                                        |     |

|          | - 850 nm MM media interface advertising codes                                    |     |

|          | - SM media interface advertising codes                                           |     |

|          | - Passive Copper Cable interface advertising codes                               |     |

|          | - Active Cable assembly media interface advertising codes                        |     |

| Table 83 | - Base-T media interface advertising codes 1                                     | 2.7 |

|          |                                                                                  |     |

| Eigune 1 | : Module Current Address Read Operation                                          | 1 0 |

|          | : Module Random Read                                                             |     |

| _        | Sequential Address Read Starting at Module Current Address                       |     |

|          | Sequential Address Read Starting at Module Current Address                       |     |

|          | : Module Write Byte Operation                                                    |     |

|          | : Module Sequential Write Operation                                              |     |

|          | : Module State Machine                                                           |     |

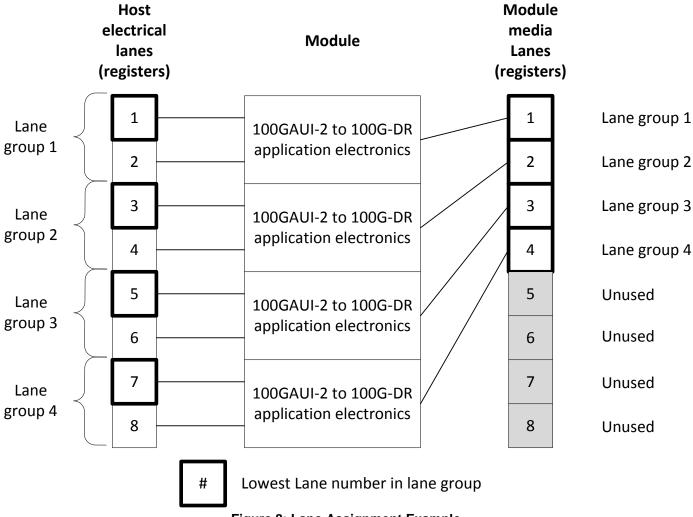

|          | : Lane Assignment Example                                                        |     |

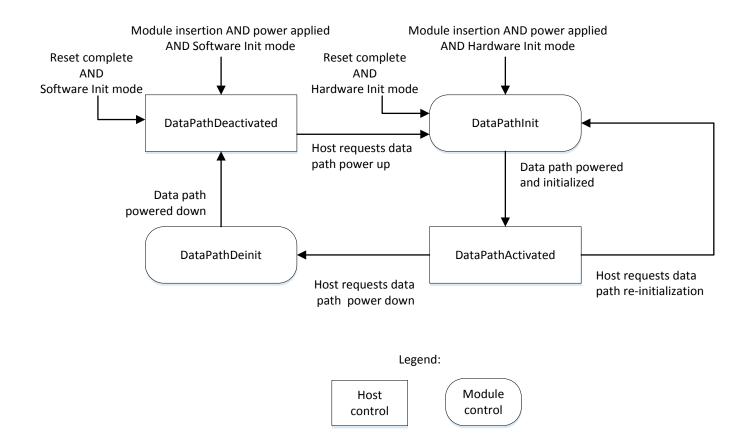

|          | : Data Path State Machine                                                        |     |

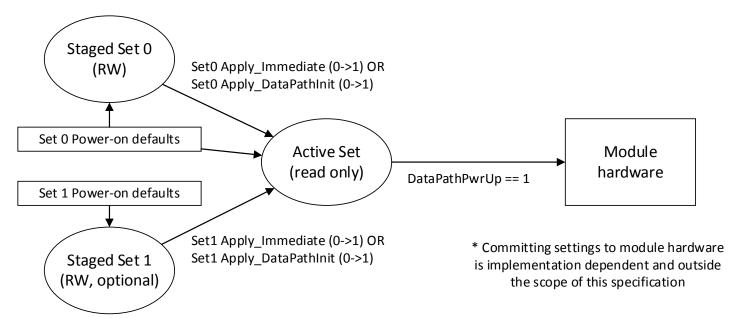

|          | 0: Control Set Data Flow Diagram                                                 |     |

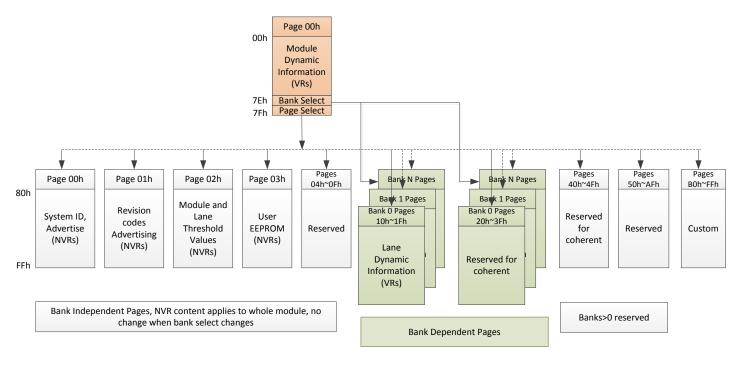

| _        | 1: CMIS Module Memory Map                                                        |     |

|          | - CIIIO IICAGIC IICAGI IIIAPIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                      | - J |

# 1 Management Interface

## 1.1 Introduction

This specification defines the Common Management Interface Specification (CMIS) for QSFP-DD, OSFP and COBO in order to enable flexible use of modules and cable assemblies (hereafter referred to as modules unless cable assemblies are specifically mentioned) by the user. It shares some similarities with the management interfaces used in other form factors such as QSFP, SFP, and CFP. This specification supports a module with 8 host electrical lanes. Support for modules with more host lanes is possible (in increments of up to 8 lanes) by a bank selection feature (which allows several instances of an

adressable page to exist in the paged register map). Due to this new mechanism this specification is not backwards compatible with SFF-8636. Some host ports may support both 4-channel and 8-channel devices; when a 4-channel device is inserted into such a port the appropriate memory map (e.g. SFF-8636) must be used. This case is outside the scope of this document.

The host-to-module interactions needed to initialize active modules are presented in two state machines. A module-level state machine defines the initialization of the management interface as well as control of the module-wide power mode. A data path-specific state machine defines the host and module interactions and behaviors needed for power up and initialization of the data path(s) in the module.

The CMIS is intended to cover a wide range of possible module functionalities and applications, ranging from cable assemblies to coherent DWDM modules. The CMIS is designed with the intent not to burden the simple cases but to provide a common set of management interactions and a common register map.

In some modules, multiplexing of the high speed signals between the host electrical interface and the module media interface may occur in the module. In this specification, all references to lane numbers are based on the electrical connector interface lanes, unless otherwise indicated. In cases where a status or control aspect is applicable only to lanes after multiplexing or demultiplexing has occurred, the status or control is intended to apply to all lanes in the data path, unless otherwise indicated. Symmetry is expected between the Tx and the Rx hardware structure; for example Tx lanes that are multiplexed in the Tx are demultiplexed in the Rx. Each Application selected by the host is applied to the same Tx and Rx host electrical lanes.

# 1.2 Definitions and Acronyms

ACK: Acknowledge

ASCII: American Standard Code for Information Interchange: the numerical representation of a character

CDR: clock and data recovery

Checksum: a number derived from a block of digital data for the purpose of detecting errors.

CLEI: (Common Language Equipment Identification) code is a 10-byte field that contains the vendor's CLEI code in ASCII characters (see www.commonlanguage.com)

Custom: Custom fields and formats are defined by the module manufacturer and may be unique to a specific vendor.

Data Path: Host electrical and module media lanes grouped together into a logical concept. A data path is intended to represent a group of lanes that will be powered up or down and initialized together.

DFB: Distributed Feedback Laser

DWDM: Dense Wavelength Division Multiplexing

EML: Externally Modulated Laser

Flat Memory: Single 256-byte memory implemented without paging

FP: Fabry-Perot Laser

NACK: Not Acknowledge

NV: Non-Volatile memory: a type of memory that can retrieve stored information even after having been power cycled

OM2: cabled optical fiber containing 50/125 um multimode fiber with a minimum overfilled launch bandwidth of 500 MHz-km at 850 nm and 500 MHz-km at 1300 nm as IEC 60793-2-10 Type Ala.1 fiber.

OM3: cabled optical fiber containing 50/125 um laser optimized multimode fiber with a minimum overfilled launch bandwidth of 1500 MHz-km at 850 nm and 500 MHz-km at 1300 nm as well as an effective laser launch bandwidth of 2000 MHz-km at 850 nm in accordance with IEC 60793-2-10 Type Ala.2 fiber.

OM4: cabled optical fiber containing 50/125 um laser optimized multimode fiber with a minimum overfilled launch bandwidth of 3500 MHz-km at 850 nm and 500 MHz-km at 1300 nm as well as an effective laser launch bandwidth of 4700 MHz-km at 850 nm in accordance with IEC 60793-2-10 Type Ala.3 fiber.

OM5: cabled optical fiber containing 50/125 um laser optimized multimode fiber with a minimum overfilled launch bandwidth of 3500 MHz-km at 850 nm, 1850 MHz-km at 953 nm and 500 MHz-km at 1300 nm as well as an effective laser launch bandwidth of 4700 MHz-km at 850 nm and 2470 MHz-km at 953 nm in accordance with IEC 60793-2-10 Type Ala.4 fiber.

OMA: Optical Modulation Amplitude: The difference between two optical power levels, of a digital signal generated by an optical source, e.g., a laser diode.

OSNR: Optical Signal to Noise Ratio: The ratio between the optical signal power and the noise power in a given bandwidth.

OUI: Organizationally Unique Identifier: A unique vendor code assigned by the IEEE

Pave: Average Power: The average optical power

Post-cursor equalization: Rx output means used to reduce post-cursor ISI

Pre-cursor equalization: Rx output means used to reduce pre-cursor ISI

Pulse Amplitude Modulation, four levels (PAM4): a modulation scheme where two bits are mapped into four signal amplitude levels to enable transmission of two bits per symbol.

Rx: an electronic component (Rx) that converts an input signal (optical or electrical) to an electrical (retimed or non-retimed) output signal.

SDA: bidirectional Serial Data line

SCL: bidirectional Serial Clock line

SNR: Signal to Noise Ratio: The ratio of signal power to the noise power, expressed in decibels

TEC: Thermal Electric Cooler

TWI: Two Wire Interface

tWR: Time required to complete a single or sequential write to non-volatile memory.

Tx: a circuit (Tx) that converts an electricalinput signal to a signal suitable for the communications media (optical or electrical).

VCSEL: Vertical Cavity Surface Emitting Laser

WDM: Wavelength Division Multiplexing

## 1.3 Management Interface Timing Specifications and Protocol

## 1.3.1 Introduction

The management interface between Host and Module consists of a serial communications interface and small set of discrete hardware signals described in Appendix A - Form Factor Signal Names. The communication interface allows the Host to access registers in the Module. It is described in detail in the remainder of this section.

Communication between Host and Module is done via a Two Wire serial Interface(TWI). Detailed electrical specifications and TWI timing are given in the appropriate hardware/module specification.

## 1.3.2 Management Interface Timing Specification

The management interface timing requirements are defined in the appropriate hardware specification. The TWI address of the module is 1010000X (A0h). The host shall initially address the module using a 0-400 kHz SCL clock speed. If a higher management interface speed is supported, (See Table 18) the host may switch to the 0-1MHz SCL clock speed.

In order to allow access to multiple modules on the same TWI bus, some form factors include and require the module to support a module select signal, (ModSelL). For these form factors, before initiating a TWI bus communication, the host shall provide setup time on the ModSelL line of all modules on the TWI bus. The host shall not change the ModSelL line of any module until the TWI bus communication is complete and the hold time requirement is satisfied.

## 1.3.3 Signal Interface

The TWI shall consist of a master and slave. The host shall be the master and the module shall be the slave. Control and data are transferred serially. The master shall initiate all data transfers. Data can be transferred from the master to the slave and from the slave to the master. The TWI shall consist of clock (SCL) and data (SDA) signals. The master utilizes SCL to clock data and control information on the TWI bus. The master and slave shall latch the state of SDA on the positive transitioning edge of SCL. The SDA signal is bi-directional. During data transfer, the SDA signal shall transition when SCL is low. A transition on the SDA signal while SCL is high shall indicate a stop or start condition.

## 1.3.4 Serial Interface Protocol

## 1.3.4.1 Operational States and State Transition

## 1.3.4.1.1 Start

A high-to-low transition of SDA with SCL high is a START condition. All TWI bus operations shall begin with a START condition.

## 1.3.4.1.2 Stop

A low-to-high transition of SDA with SCL high is a STOP condition. All TWI bus operations shall end with a STOP condition

## 1.3.4.1.3 Acknowledge

After sending each 8-bit word, the side driving the TWI bus releases the SDA line for one bit time, during which the monitoring side of the TWI bus is allowed to pull SDA low (zero) to acknowledge (ACK) that it has received each word. Write data operations shall be acknowledged by the slave for all bytes. Read data operations shall be acknowledged by the master for all but the final byte read, for which the master shall respond with a non-acknowledge (NACK) by permitting SDA to remain high and followed by a STOP.

## 1.3.4.1.4 Clock Stretching

To extend the TWI data transfer the slave asserts clock low. This should be initiated while the clock is low. This can be used by the slave to delay completion of the operation.

## 1.3.4.2 Reset TWI

## 1.3.4.2.1 Power On Reset

The interface shall enter a reset state upon application of power.

#### 1.3.4.2.2 TWI Protocol Reset

Synchronization issues may cause the master and slave to disagree on the specific bit location currently being transferred, the type of operation or even if an operation is in progress. The TWI protocol has no explicitly defined reset mechanism. The following procedure may force completion of the current operation and cause the slave to release SDA.

- a) The master shall provide up to nine SCL clock cycle (drive low, then high) to the slave

- b) The master shall monitor SDA while SCL is high on each cycle.

- c) If the slave releases SDA, it will be high and the master is then free to initiate a START operation for the next transaction

- d) If SDA remains low after a full nine clock cycles the TWI protocol reset has failed

#### 1.3.4.2.3 Reset Signal

Some implementations may include a reset signal. If provided, upon assertion of the reset signal the TWI shall transition to the reset state.

#### 1.3.4.3 TWI Binary Frame Format

## 1.3.4.3.1 Read/Write Controls

After the start condition, the first 8-bit word of a TWI bus operation shall consist of '1010000' followed by a read/write control bit.

The least significant bit indicates if the operation is a data read or write. A read operation is performed if this bit is high and a write operation is executed if this bit is set low. Upon completion of the control word transmission the slave shall assert the SDA signal low to acknowledge delivery (ACK) of the control/address word.

#### 1.3.4.3.2 Address and Data

Following the read/write control bit, addresses and data words are transmitted in 8-bit words. Data is transferred with the most significant bit (MSB) first. Multiple Byte transactions shall be transmitted in increasing byte address order over the TWI.

## 1.3.5 Read/Write Operations

# 1.3.5.1 Slave Memory Address Counter (Read and Write Operations)

All TWI slaves maintain an internal data word address counter containing the last address accessed during the latest read or write operation, incremented by one. The address counter is incremented whenever a data word is received or sent by the slave. This

address remains valid between operations as long as power to the slave is maintained. Upon loss of power to or reset of the module or upon transactions not terminated by a Stop condition, the slave address counter contents may be indeterminate. The address roll-over during read and writes operations is from the last byte of the 128-byte memory page to the first byte of the same page.

The host shall use single 2-byte reads to retrieve all 16-bit data, to guarantee data coherency. The module shall prevent the host from acquiring partially updated multi-byte data during a 2-byte read. Data consistency for accesses to more than two bytes requires an application level interaction protocol using fields in the register map. It is not guaranteed by the basic R/W interaction primitives.

## 1.3.5.2 Read Operations

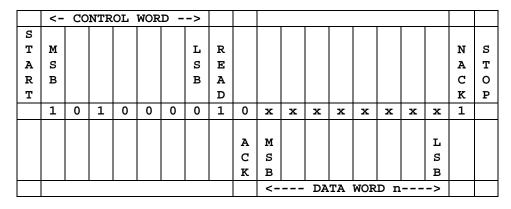

#### 1.3.5.2.1 Current Address Read

A current address read operation requires only the slave address read word (10100001) be sent. Once acknowledged by the slave, the current address data word is serially clocked out. The transfer is terminated when the master responds with a NACK and a STOP instead of an acknowledge.

|                            |       | <-          |   | CON | TRO | L W | ORD |             | ->               |             |             |   |    |    |     |     |   |             |                  |                  |

|----------------------------|-------|-------------|---|-----|-----|-----|-----|-------------|------------------|-------------|-------------|---|----|----|-----|-----|---|-------------|------------------|------------------|

| M<br>A<br>S<br>T<br>E<br>R | START | M<br>S<br>B |   |     |     |     |     | L<br>S<br>B | R<br>E<br>A<br>D |             |             |   |    |    |     |     |   |             | N<br>A<br>C<br>K | S<br>T<br>O<br>P |

|                            |       | 1           | 0 | 1   | 0   | 0   | 0   | 0           | 1                | 0           | x           | x | x  | x  | x   | x   | x | x           | 1                |                  |

| S<br>L<br>A<br>V<br>E      |       |             |   |     |     |     |     |             |                  | A<br>C<br>K | M<br>S<br>B |   |    |    |     |     |   | L<br>S<br>B |                  |                  |

|                            |       |             |   |     |     |     |     |             |                  |             | \<br>\      |   | DA | TA | WOR | D - |   | ->          |                  |                  |

Figure 1: Module Current Address Read Operation

## 1.3.5.2.2 Random Read

A random read operation requires a dummy write operation to load in the target byte address. This is accomplished by the following sequence: The target 8-bit data word address is sent following the device address write word (10100000) and acknowledged by the slave. The master then generates another START condition (aborting the dummy write without incrementing the counter) and a current address read by sending a device read address (10100001). The slave acknowledges the device address and serially clocks out the requested data word. The transfer is terminated when the master responds with a NACK and a STOP instead of an acknowledge.

|   |   | <- | -CO | NTR | OL | WOR | D - | -> |   |   | <i< th=""><th>BYTI</th><th>E OI</th><th>FSI</th><th>ET A</th><th>ADDI</th><th>RESS</th><th>3&gt;</th><th></th></i<> | BYTI | E OI | FSI | ET A | ADDI | RESS | 3> |   |

|---|---|----|-----|-----|----|-----|-----|----|---|---|---------------------------------------------------------------------------------------------------------------------|------|------|-----|------|------|------|----|---|

| M |   |    |     |     |    |     |     |    |   |   |                                                                                                                     |      |      |     |      |      |      |    |   |

| Α | s |    |     |     |    |     |     |    | W |   |                                                                                                                     |      |      |     |      |      |      |    |   |

| S | T | M  |     |     |    |     |     | L  | R |   | M                                                                                                                   |      |      |     |      |      |      | ь  |   |

| T | Α | S  |     |     |    |     |     | S  | I |   | S                                                                                                                   |      |      |     |      |      |      | S  |   |

| E | R | В  |     |     |    |     |     | В  | Т |   | В                                                                                                                   |      |      |     |      |      |      | В  |   |

| R | Т |    |     |     |    |     |     | Р. | E |   |                                                                                                                     |      |      |     |      |      |      | Р. |   |

|   |   |    |     |     |    |     |     |    |   |   |                                                                                                                     |      |      |     |      |      |      |    |   |

|   |   | 1  | 0   | 1   | 0  | 0   | 0   | 0  | 0 | 0 | x                                                                                                                   | x    | х    | x   | х    | x    | х    | х  | 0 |

| S |   |    |     |     |    |     |     |    |   |   |                                                                                                                     |      |      |     |      |      |      |    |   |

| L |   |    |     |     |    |     |     |    |   | A |                                                                                                                     |      |      |     |      |      |      |    | A |

| A |   |    |     |     |    |     |     |    |   | C |                                                                                                                     |      |      |     |      |      |      |    | C |

| v |   |    |     |     |    |     |     |    |   | K |                                                                                                                     |      |      |     |      |      |      |    | K |

| E |   |    |     |     |    |     |     |    |   |   |                                                                                                                     |      |      |     |      |      |      |    |   |

|   |   |    | -   | •   | •  |     |     |    | - |   |                                                                                                                     |      |      |     |      |      |      | •  |   |

Figure 2: Module Random Read

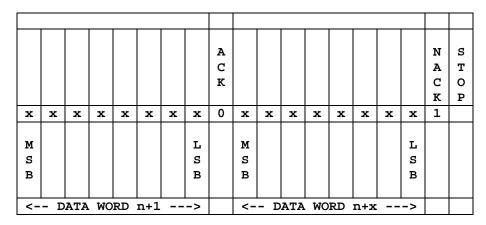

# 1.3.5.3 Sequential Read

Sequential reads are initiated by either a current address read (see Figure 3) or a random address read (see Figure 4). To specify a sequential read, the host responds with an acknowledge (instead of a STOP) after each data word. As long as the module receives an acknowledge, it shall serially clock out sequential data words. The sequence is terminated when the host responds with a NACK and a STOP instead of an acknowledge.

|                       |                       | <-          | CO | NTR | OL | WOR | D - | ->          |                  |             |             |   |    |    |     |     |   |             |             |

|-----------------------|-----------------------|-------------|----|-----|----|-----|-----|-------------|------------------|-------------|-------------|---|----|----|-----|-----|---|-------------|-------------|

| M<br>A<br>S<br>T<br>E | S<br>T<br>A<br>R<br>T | M<br>S<br>B |    |     |    |     |     | L<br>S<br>B | R<br>E<br>A<br>D |             |             |   |    |    |     |     |   |             | A<br>C<br>K |

|                       |                       | 1           | 0  | 1   | 0  | 0   | 0   | 0           | 1                | 0           | x           | x | x  | x  | x   | x   | x | x           | 0           |

| S<br>L<br>A<br>V<br>E |                       |             |    |     |    |     |     |             |                  | A<br>C<br>K | M<br>S<br>B |   |    |    |     |     |   | L<br>S<br>B |             |

|                       |                       |             |    |     |    |     |     |             |                  |             | <b>'</b> -  |   | DA | TA | WOR | D n |   | ->          |             |

Figure 3: Sequential Address Read Starting at Module Current Address

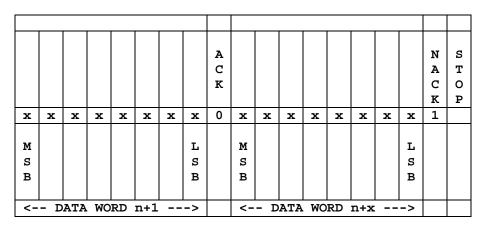

# 1.3.5.3.1 Sequential Read from Random Start Address

|                            |                       | <-          | CO | NTR | OL. | WOR | D - | ->          |                  |             | <i< th=""><th>ЗҮТІ</th><th>E OI</th><th>FSI</th><th>ET 2</th><th>ADDI</th><th>RESS</th><th>3&gt;</th><th></th></i<> | ЗҮТІ | E OI | FSI | ET 2 | ADDI | RESS | 3>          |             |

|----------------------------|-----------------------|-------------|----|-----|-----|-----|-----|-------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------|------|------|-----|------|------|------|-------------|-------------|

| M<br>A<br>S<br>T<br>E<br>R | S<br>T<br>A<br>R<br>T | M<br>S<br>B |    |     |     |     |     | L<br>S<br>B | W<br>R<br>I<br>T |             | M<br>S<br>B                                                                                                         |      |      |     |      |      |      | L<br>S<br>B |             |

|                            |                       | 1           | 0  | 1   | 0   | 0   | 0   | 0           | 0                | 0           | x                                                                                                                   | x    | x    | x   | x    | x    | x    | x           | 0           |

| S<br>L<br>A<br>V<br>E      |                       |             |    |     |     |     |     |             |                  | A<br>C<br>K |                                                                                                                     |      |      |     |      |      |      |             | A<br>C<br>K |

|                            |                       |             |    |     |     |     |     |             |                  |             |                                                                                                                     |      |      |     |      |      |      |             |             |

|   | <- | CO | NTR | OL | WOR | D - | -> |   |   |    |   |    |    |     |     |   |    |   |

|---|----|----|-----|----|-----|-----|----|---|---|----|---|----|----|-----|-----|---|----|---|

| S |    |    |     |    |     |     |    |   |   |    |   |    |    |     |     |   |    |   |

| T | M  |    |     |    |     |     | L  | R |   |    |   |    |    |     |     |   |    | A |

| A | ន  |    |     |    |     |     | s  | E |   |    |   |    |    |     |     |   |    | C |

| R | В  |    |     |    |     |     | В  | A |   |    |   |    |    |     |     |   |    | K |

| T |    |    |     |    |     |     |    | D |   |    |   |    |    |     |     |   |    |   |

|   | 1  | 0  | 1   | 0  | 0   | 0   | 0  | 1 | 0 | ×  | × | x  | x  | x   | ×   | x | ×  | 0 |

|   |    |    |     |    |     |     |    |   |   |    |   |    |    |     |     |   |    |   |

|   |    |    |     |    |     |     |    |   | A | M  |   |    |    |     |     |   | L  |   |

|   |    |    |     |    |     |     |    |   | С | S  |   |    |    |     |     |   | S  |   |

|   |    |    |     |    |     |     |    |   | K | В  |   |    |    |     |     |   | В  |   |

|   |    |    |     |    |     |     |    |   |   |    |   |    |    |     |     |   |    |   |

|   |    |    |     |    |     |     |    |   |   | <- |   | DA | TA | WOR | D n |   | -> |   |

Figure 4: Sequential Address Read Starting with Random Module Read

## 1.3.5.4 Write Operations

A write operation requires an 8-bit data word address following the device address write word (10100000) and acknowledgement. Upon receipt of this address, the slave shall again respond with a zero (ACK) to acknowledge and then clock in the first 8-bit data word. Following the receipt of the 8-bit data word, the slave shall output a zero (ACK) and the master must terminate the write sequence with a STOP condition for the write cycle to begin. If a START condition is sent in place of a STOP condition (i.e. a repeated START per the TWI specification) the write is aborted and the data received during that operation is discarded. Upon receipt of the proper STOP condition, the slave enters an internally timed write cycle, tWR, to internal memory. (See appropriate Hardware specification for tWR timing) The slave disables its management interface input during this write cycle and shall not respond or acknowledge subsequent commands until the internal memory write is complete. Note that TWI 'Combined Format' using repeated START conditions is not supported on write commands.

|                            |                  | <-          | CO | NTR | OL | WOR | D - | ->          |                       |             | <i< th=""><th>ЗҮТІ</th><th>E OI</th><th>FFSI</th><th>ST Z</th><th>ADDI</th><th>RESS</th><th>3&gt;</th><th></th><th>٧</th><th></th><th>D</th><th>ATA</th><th>. WO</th><th>RD</th><th></th><th>-&gt;</th><th></th><th></th></i<> | ЗҮТІ | E OI | FFSI | ST Z | ADDI | RESS | 3>          |             | ٧           |   | D | ATA | . WO | RD |   | ->          |             |                  |

|----------------------------|------------------|-------------|----|-----|----|-----|-----|-------------|-----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------|-------------|-------------|---|---|-----|------|----|---|-------------|-------------|------------------|

| M<br>A<br>S<br>T<br>E<br>R | S<br>T<br>A<br>R | M<br>S<br>B |    |     |    |     |     | L<br>S<br>B | W<br>R<br>I<br>T<br>E |             | M<br>S<br>B                                                                                                                                                                                                                    |      |      |      |      |      |      | L<br>S<br>B |             | M<br>S<br>B |   |   |     |      |    |   | L<br>S<br>B |             | S<br>T<br>O<br>P |

|                            |                  | 1           | 0  | 1   | 0  | 0   | 0   | 0           | 0                     | 0           | x                                                                                                                                                                                                                              | x    | x    | х    | x    | x    | x    | x           | 0           | x           | x | x | x   | x    | x  | x | x           | 0           |                  |

| S<br>L<br>A<br>V<br>E      |                  |             |    |     |    |     |     |             |                       | A<br>C<br>K |                                                                                                                                                                                                                                |      |      |      |      |      |      |             | A<br>C<br>K |             |   |   |     |      |    |   |             | A<br>C<br>K |                  |

|                            |                  |             |    |     |    |     | •   | •           | •                     |             |                                                                                                                                                                                                                                |      |      | •    |      |      |      |             |             |             |   |   |     |      | •  |   |             |             |                  |

**Figure 5: Module Write Byte Operation**

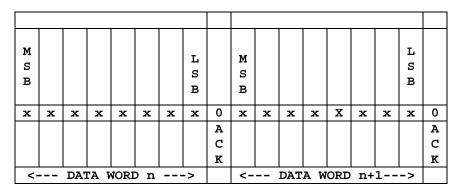

## 1.3.5.4.1 Sequential Write

The TWI slave shall support a sequential byte write of up to eight bytes without repeatedly sending slave address and memory address information. In a sequential write, the host should not include in the sequence a mixture of volatile and non-volatile registers. It should be noted that at the end of each 128 byte page, the next address rolls over to the first byte of the same page.

A sequential write is initiated the same way as a single byte write, but the host master does not send a stop condition after the first word is clocked in. Instead, after the slave acknowledges receipt of the first data word, the master can transmit additional data words: seven additional words for non-volatile memory and volatile memory. The slave shall send an acknowledge after each data word received. The slave may act on write data after generating the acknowledge or it may buffer the write transaction.

The master must terminate the sequential write sequence with a STOP condition. Upon receipt of the proper Stop condition, for writes to non-volatile memory, the slave may enter an internally timed write cycle, tWR, to internal memory. The slave may disable its management interface input during this write cycle and may not respond or acknowledge subsequent commands until the internal memory write is complete. If there is no proper STOP condition, the results of the sequential write are unpredictable.

Note that TWI 'combined format' using repeated START conditions is not supported on write commands.

|                            |       | <-          | CO | NTR | OL | WOR | D - | ->          |                  |             | <i< th=""><th>ЗҮТІ</th><th>E OI</th><th>FSI</th><th>ET 2</th><th>ADDI</th><th>RESS</th><th>3&gt;</th><th></th></i<> | ЗҮТІ | E OI | FSI | ET 2 | ADDI | RESS | 3>          |             |

|----------------------------|-------|-------------|----|-----|----|-----|-----|-------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------|------|------|-----|------|------|------|-------------|-------------|

| M<br>A<br>S<br>T<br>E<br>R | START | M<br>S<br>B |    |     |    |     |     | L<br>S<br>B | W<br>R<br>I<br>T |             | M<br>S<br>B                                                                                                         |      |      |     |      |      |      | L<br>S<br>B |             |

|                            |       | 1           | 0  | 1   | 0  | 0   | 0   | 0           | 0                | 0           | x                                                                                                                   | x    | x    | x   | x    | x    | x    | x           | 0           |

| S<br>L<br>A<br>V<br>E      |       |             |    |     |    |     |     |             |                  | A<br>C<br>K |                                                                                                                     |      |      |     |      |      |      |             | A<br>C<br>K |

|                            |       |             |    |     |    | •   |     |             | •                |             |                                                                                                                     |      |      |     |      |      | •    |             |             |

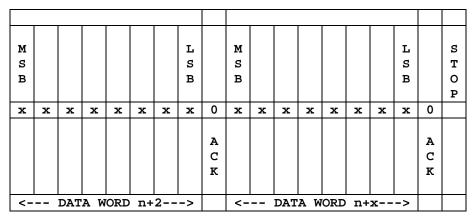

**Figure 6: Module Sequential Write Operation**

# 1.3.5.4.2 Acknowledge Polling

Once the module internally timed write cycle has begun (and inputs are being ignored on the bus) acknowledge polling can be used to determine when the write operation is complete. This involves sending a START condition followed by the device address word. Only if the internal write cycle is complete shall the module respond with an acknowledge to subsequent commands, indicating read or write operations can continue.

# 1.3.6 Timing for Soft Control and Status Functions

Timing for module soft control, status functions, and squelch and disable timings can be found in the appropriate Module Hardware Specification.

## 1.4 Module State Machine

The purpose of the Module State Machine is twofold: to provide both a description of the bring-up process for the management interface as well as to identify the module-wide power mode. The State Machine is engaged after module insertion and power on. The Module State Machine is applicable to both modules and cable assemblies, whether passive or active and is pictured in Figure 7. This common management interface specification is designed to be applied to multiple form factors. Therefore, actions and properties are described using generic terms instead of using application-specific signal names. Refer to Appendix A - Form Factor Signal Names for the association between generic descriptors in this section and application-specific signal names.

#### Module state machine

Figure 7: Module State Machine

The Module State Machine describes module-wide behaviors and properties. For data path-specific behaviors and properties, refer to the Data Path State Machine in Section 1.5.3.

States with a rectangular outline are host control states, where the module is waiting for host-initiated actions, either through the memory map or through a hardware signal. The duration of host control states is unbounded.

#### Common management specification Rev 3.0

States with an oval outline are transient states where the module is in control of initialization activities. These module control states have an implementation-dependent duration. Dynamic register content is unreliable during module control states.

Table 1 and Table 2 provide a summary of the high-level behaviors and properties of each module state for passive copper cable assembly and active module implementations, respectively. Implementers of passive copper cable assemblies should note that this specification was designed to allow for flat-memory EEPROM implementations for that cable type. Active modules and active cable assemblies shall use the paged memory model. For all module types, refer to sections 1.4.3-1.4.9 for detailed requirements for each state.

Table 1- Passive copper cable assembly state behaviors

| State        | Power<br>Mode | Behavior in state                                 | Exit condition                                                                                                                        | Next state         | Required/<br>Optional |  |

|--------------|---------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--|

| Reset        | Low<br>Power  | Management interface in reset                     | Reset signal deasserted and power applied                                                                                             | MgmtInit           | Optional              |  |

| MgmtInit     | Low<br>Power  | Management interface powering up and initializing | Module Management Interface ready AND Interrupt signal asserted OR t_init timeout. (See Hardware Specification) Reset signal asserted | ModuleLowPwr Reset | ewr Required          |  |

| ModuleLowPwr | Low<br>Power  | Management interface available                    | Reset signal asserted                                                                                                                 | Reset              | Required              |  |

| ModulePwrUp  |               | This state is not app                             | plicable to passive copper cable assemblies                                                                                           |                    |                       |  |

| ModuleReady  |               | This state is not app                             | clicable to passive copper cable assemblies                                                                                           |                    |                       |  |

| ModulePwrDn  |               | This state is not app                             | licable to passive copper cable assemblies                                                                                            |                    |                       |  |

| Fault        |               | This state is not app                             | licable to passive copp                                                                                                               | er cable assemi    | blies                 |  |

Table 2- Active module state behaviors

| State                                                                                             | Power<br>Mode                                                                                         | Behavior in state                                        | Exit condition                                                                                      | Next state        | Required/<br>Optional |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------|-----------------------|

| Reset                                                                                             | Low<br>Power                                                                                          | Management interface and all module electronics in reset | Reset signal deasserted and power applied                                                           | MgmtInit          | Required              |

| MgmtInit Low Power interface powering and initializing Interface ready (t_init timeout) (Hardware |                                                                                                       | Interface ready OR t_init timeout) (See                  | ModuleLowPwr                                                                                        | Required          |                       |

|                                                                                                   |                                                                                                       |                                                          | Hardware Init mode AND (Module Mgmt Interface ready OR t_init timeout) (See Hardware Specification) | ModulePwrUp       |                       |

|                                                                                                   |                                                                                                       |                                                          | Reset signal asserted Fault condition detected                                                      | Reset<br>Fault    | _                     |

| ModuleLowPwr                                                                                      | ModuleLowPwr Low Management Host requests an action that requires available, host may High Power mode |                                                          | action that requires                                                                                | ModulePwrUp Reset | Required              |

|                                                                                                   |                                                                                                       |                                                          | Fault condition detected                                                                            | Fault             | -                     |

| ModulePwrUp                                                                                       | High<br>Power                                                                                         | Module transitioning to                                  | Power up activities are complete                                                                    | ModuleReady       | Required              |

|                                                                                                   |                                                                                                       | high power mode                                          | Host requests module return to Low Power mode                                                       | ModulePwrDn       |                       |

|                                                                                                   |                                                                                                       |                                                          | Reset signal asserted Fault condition detected                                                      | Reset<br>Fault    |                       |

| Power consuming p                                                                                 |                                                                                                       | Module may be consuming power up to the level            | Host requests module return to Low Power mode                                                       | ModulePwrDn       | Required              |

|                                                                                                   |                                                                                                       | defined in the fields in Table 30                        | Reset signal asserted Fault condition detected                                                      | Reset<br>Fault    | _                     |

| ModulePwrDn High Module Module has return to Low Power module                                     |                                                                                                       | Module has returned to Low Power mode                    | ModuleLowPwr                                                                                        | Required          |                       |

|                                                                                                   |                                                                                                       | low power mode                                           | Reset signal asserted Fault condition detected                                                      | Reset<br>Fault    | -                     |

| Fault                                                                                             | Low<br>Power                                                                                          | Module is waiting for host action                        | Module power down Reset signal asserted                                                             | N/A<br>Reset      | Optional              |

Certain Module State Machine state transitions shall cause the Module State Changed flag to be set, while other transitions shall not set this flag. In general, module-initiated state transitions result in the Module State Changed flag being set. Table 3 below defines the appropriate flag behavior for each valid state transition.

**Table 3- Module State Changed flag behaviors**

| Prior state  | Next state   | Causes Module State<br>Changed flag to be<br>set? |

|--------------|--------------|---------------------------------------------------|

| Reset        | MgmtInit     | No                                                |

| Any state    | Reset        | No                                                |

| Any state    | Fault        | Yes                                               |

| MgmtInit     | ModuleLowPwr | Yes                                               |

| MgmtInit     | ModulePwrUp  | No                                                |

| ModuleLowPwr | ModulePwrUp  | No                                                |

| ModulePwrUp  | ModuleReady  | Yes                                               |

| ModulePwrUp  | ModulePwrDn  | No                                                |

| ModuleReady  | ModulePwrDn  | No                                                |

| ModulePwrDn  | ModuleLowPwr | Yes                                               |

## 1.4.1 Module Init Modes

Under normal circumstances, modules are expected to power up into the ModuleLowPwr state, to allow host management software to configure the module properties prior to operation. This software-controlled power-up behavior is called Software Init mode in this specification. Some module form factors may provide an alternative Hardware Init mode (see Appendix A - Form Factor Signal Names), where the module proceeds to the ModulePwrUp state to power up the default Application(s) data path(s). The support of hardware input signal-selectable Init mode is form factor dependent, but is not required for this specification. When not implemented, the module shall power up according to Software Init mode procedures, as described in this document. The module shall only observe the state of the Init mode signal during the MgmtInit state. Any host changes to the Init mode signal that occur after MgmtInit will not be applied until the module is reset or power cycled. Init mode is not applicable to passive copper cable assemblies.

When booting in Hardware Init mode, the module shall utilize power-on defaults for all data path configuration settings, including Application Select.

#### 1.4.2 Module Power Mode and Module and Data Path State Machine interactions

The module power mode may be used by the host to limit module power consumption to one of two thresholds — Low Power mode or High Power mode. When in Low Power mode, the maximum power consumption of the module must remain below a form factor defined maximum. Passive copper cable assemblies are in Low Power mode at all times and are fully functional. Active module functionality when in Low Power mode is limited to host-to-module interactions over the management interface. All modules shall initially power up in Low Power mode, unless booting in Hardware Init mode. When in High Power mode, active modules may be fully functional, depending on configuration settings, and the maximum power consumption of the module shall be limited to the advertised Module Power Class (Table 30).

The module power mode is dependent on the state of the data paths in the module. The Module State Machine reflects the module power mode, as shown in Table 1 and Table 2. As soon as data path power up is initiated on one or more data paths, the module shall transition to High Power mode. During this power up process, the Data Path State Machine is in the DataPathInit state and the Module State Machine is in ModulePwrUp. Once power up is complete on all requested lanes, the Data Path State Machine and Module State Machines shall transition to DataPathActivated and ModuleReady, respectively. Refer to the Data Path State Machine in Section 1.5.3 for details regarding Data Path State behaviors. Implementers should note that it is theoretically possible to create an active module whose maximum power dissipation is below the Low Power Mode threshold, even when fully functional. To maintain consistency for host firmware implementations, such

modules shall continue to follow the rules set forth in this section, requiring the host to explicitly request Data Path power up and down through the DataPathPwrUp bits and following the module state transitions initiated by host actions.

The maximum High Power mode power consumption for the module is identified by the module power advertising fields in Table 30. Once the module is in High Power mode, it shall remain in High Power mode until a Fault occurs or until explicitly directed by the host to transition to Low Power mode, by the host setting the ForceLowPwr bit in the memory map (Table 23) or asserting the LowPwr signal. Implementation of the LowPwr signal is optional and form factor dependent (see Appendix A - Form Factor Signal Names).

Module implementers should note that the host may request power up or power down of module data paths during normal operation but the module may remain in High Power mode, even if all data paths are powered down individually. The requirement of exclusive ForceLowPwr bit/LowPwr signal control for entry into Low Power mode is provided to allow faster re-power up of data paths than would be possible if the module returned to Low Power mode automatically when all data paths are returned to the "DataPathDeaactivated" state.

When the host requests a return to Low Power mode and the module state is in ModulePwrUp or ModuleReady, the Data Path State Machines for all data paths become dependent on the Module State Machine. The Module State Machine shall transition to ModulePwrDn and all Data Path State Machines that are not already in DataPathDeactivated shall transition to DataPathDeinit. This transition shall occur even if the module is booting in Hardware Init Mode or the Data Path state is in DataPathInit. When all data paths are powered down and the module has returned to Low Power mode, the Module State Machine and Data Path State Machines shall transition to ModuleLowPwr and DataPathDeactivated, respectively.

If the host requests a transition to Low Power Mode while the module is already in Low Power Mode, the module shall remain in Low Power Mode until this request is cleared. If the module is booting in Hardware Init Mode and the host sets the ForceLowPwr bit or asserts the LowPwr signal during MgmtInit, the module shall follow the initialization activities associated with Software Init Mode.

#### 1.4.3 Reset State

A low level on the Reset signal for longer than the minimum reset pulse length initiates a complete module reset. Refer to form factor-specific documentation for the minimum reset pulse duration. A reset can also be initiated through software using the Software Reset bit (Table 23). A software reset can only trigger a transient reset after which the module will enter MgmtInit. The Reset state shall be entered from any state by assertion of the Reset signal. The shutdown procedure used by the module for a reset event is implementation dependent.

For passive copper cables, assertion of the Reset signal may optionally hold the EEPROM in reset, however the data path shall remain active. When an active module enters the Reset state, all Data Path States shall transition immediately to the DataPathDeactivated state. Refer to section 1.5.3 for Data Path State behaviors. All lasers and module electronics shall be placed in reset upon entry into the reset state for the duration of the state.

The module shall remain in Low Power mode throughout the Reset state. All interrupts shall be suppressed while the module is in the Reset state.

Management interface transactions initiated by the host during the Reset state may be ignored by the module. Note: While the Reset signal is asserted, the management interface may be held in reset and may not respond (NAK).

After de-assertion of the Reset signal, the module may not respond until the MgmtInit state is complete. The Reset state can only be exited by deassertion of the Reset signal and application of power. Upon exit from the Reset state, the module shall enter the MgmtInit state.

## 1.4.4 MgmtInit State

The MgmtInit state is a module control state that is entered any time the module is brought out of the Reset state, (either hardware or software reset). The MgmtInit state is applicable to both active modules and passive copper cable assemblies.

During this state, the module shall configure the memory map and initialize the management interface for access by the host. The module may perform limited power-up of the high-speed data path circuitry, however the module shall remain in Low Power Mode throughout this state. For active modules, all Data Path States shall remain in DataPathDeactivated throughout MgmtInit. The module may ignore all TWI transactions while in the MgmtInit state.

Interrupt flag conformance in the MgmtInit state is defined in Section 1.6.1. All disallowed interrupt flags shall not be set during MgmtInit.

Before the module exits the MgmtInit state, all memory map register locations shall be set to their power-on defaults. In Hardware Init mode, power-up defaults may include DataPathPwrUp bits. The module shall have completed MgmtInit within the module form-factor dependent management interface initialization time, defined as the time from power on (defined as the instant when supply voltages reach and remain at or above the minimum level specified in the form factor-dependent specification), hot plug, or the rising edge of the Reset signal until the module has configured the memory map to default conditions and activated the management interface.

Upon completion of MgmtInit, the next state depends on the Init mode of the module. If the module is booting in Software Init mode, the next state is ModuleLowPwr. If the module is booting in Hardware Init mode, the next state is ModulePwrUp.

### 1.4.5 ModuleLowPwr State

The ModuleLowPwr state is a host control state, where the management interface is fully initialized and operational and the device is in Low Power mode. During this state, the host may configure the module using the management interface and memory map. Some examples of configuration activities include reading the ID and device property fields, setting CDR and other lane attributes and configuration of monitor masks. Details of host-module interactions in the ModuleLowPwr state are implementation dependent and are outside the scope of this specification.

Upon entry into the ModuleLowPwr state, the module shall set the Module State register (Table 18) to the ModuleLowPwr state and set the Module State Changed interrupt flag (Table 21). The module shall not clear any interrupt flags on the state change. Interrupt flags are only cleared when the host reads the flag. Host implementers should note that the host must clear the ForceLowPwr bit (if set) (Table 23) before setting DataPathPwrUp to exit the ModuleLowPwr state (Table 53).

Interrupt flag conformance in the ModuleLowPwr state is defined in Section 1.6.1. All disallowed interrupt flags shall not be set during ModuleLowPwr.

When the host has completed module configuration, the host may initialize one or more data paths by setting the applicable bits in the DataPathPwrUp register (Table 53) in the

memory map. Refer to the Data Path State Machine section 1.5.3 for data path control and attribute details.

As soon as the host sets any bit in the DataPathPwrUp register, the module state shall transition to ModulePwrUp. Implementers should note that modules in ModuleLowPwr shall ignore the InitMode signal.

#### 1.4.6 ModulePwrUp state

The ModulePwrUp state is a module control state used to inform the host that one or more data paths is in the process of powering up to full power operation.

Entry into ModulePwrUp can occur from ModuleLowPwr, when the host sets one or more of the DataPathPwrUp bits (Table 53), or from MgmtInit if the module is in Hardware Init mode. In ModulePwrUp the module advances the Data Path State Machines, where the associated DataPathPwrUp bits are 1, to DataPathInit. Implementers should note that modules in ModulePwrUp shall ignore the InitMode signal. Upon entry into ModulePwrUp, the module shall set the Module State register (Table 18) to the ModulePwrUp state.

The module may be in High Power mode at any time during the ModulePwrUp state.