IA Title: Common Electrical I/O (CEI) - Electrical and Jitter Interoperability agreements for 6G+ bps, 11G+ bps, 25G+ bps, 56G+ bps and 112G+ bps I/O

**IA # OIF-CEI-05.0**

May 5, 2022

Implementation Agreement created and approved by the Optical Internetworking Forum www.oiforum.com

The OIF is an international non profit organization with over 100 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements.

With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with CFP-MSA, COBO, EA, ETSI NFV, IEEE 802.3, IETF, INCITS T11, ITU SG-15, MEF, ONF.

For additional information contact:

The Optical Internetworking Forum,

5177 Brandin Ct,

Fremont, CA 94538 USA

+1.510.492.4040 F info@oiforum.com

www.oiforum.com

Implementation Agreement OIF-CEI-05.0

Implementation Agreement: OIF-CEI-05.0

Working Group: Physical and Link Layer

Title: Common Electrical I/O (CEI) - Electrical and Jitter

Interoperability agreements for 6G+ bps, 11G+ bps, 25G+ bps,

56G+ bps and 112G+ bps I/O

| $\sim$ |       |

|--------|-------|

| Sou    | rca.  |

| OUU    | I UE. |

| 01.0 | Graeme Boyd                                                                                                                                         | Henrik Johansen                                                                                                                                               | Anthony Sanders                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 02.0 | Peter Dartnell                                                                                                                                      | Mike Lerer<br>PLL Chair                                                                                                                                       |                                                                                         |

| 03.0 | lain Robertson                                                                                                                                      | Klaus-Holger Otto                                                                                                                                             | David R. Stauffer, Ph. D.                                                               |

| 03.1 | Klaus-Holger Otto                                                                                                                                   | Tom Palkert                                                                                                                                                   | David R. Stauffer, Ph. D. PLL Chair                                                     |

| 04.0 | Klaus-Holger Otto                                                                                                                                   | David R. Stauffer, Ph. D. PLL Chair                                                                                                                           | Edward Frlan<br>TC Vice Chair                                                           |

| 05.0 | Klaus-Holger Otto TC Chair Nokia Thurn-und-Taxis-Str. 10/2 90411 Nuremberg Germany Phone: +49 911 526 3594 Klaus-Holger.Otto@nokia.com Edward Frlan | David R. Stauffer, Ph. D. PLL Chair Kandou Bus, S.A. EPFL Innovation Quartier Building I, 1015 Lausanne Switzerland Phone: +1 (802) 316-0808 david@kandou.com | Dr. Mike Peng Li Intel Corporation  USA Phone: +1 (408)-544-8312 peng.mike.li@intel.com |

|      | Semtech  Canada Phone: +1 613-416-1343 <u>EFrlan@semtech.com</u>                                                                                    |                                                                                                                                                               |                                                                                         |

5

18

19

20

13

26

27

33 34

DATE:

May 5, 2022

## ABSTRACT:

This document is the CEI implementation agreement, which specifies the transmitter. receiver and interconnect channel associated with 6G+ bps, 11G+ bps, 25G+ bps, 56G+ bps and 112G+ bps interfaces for application in high speed backplanes, chip to chip interconnect and optical modules. Also included is the Jitter definition and measurement methodologies associated with CEI interfaces.

Notice: This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

### © 2022 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIÉD, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

## 0 Document Structure and Contents

Implementation Agreement OIF-CEI-05.0

# 0.1 Revision History

The OIF document 2003.104 was the working document used for the development of the CEI-6G-SR, CEI-6G-LR, CEI-11G-SR interfaces and the jitter methodology. The history of this document is detailed in the table below:

| Revision        | Date               | Description                                                                                                                                                                                                                                      |

|-----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2003.104.00 | 28th March 2003,   | Draft 1.0. Compiled from baseline documents oif2002.605.03 (clause 0, 1), OIF2002.536.06 (clause 2), oif2002.520.02 (clauses 4, 5), OIF2002.506.02 (clause 6)                                                                                    |

| OIF 2003.104.01 | 3rd May 2003       | Draft 2.0. Contains changes as result from comments received from Draft 1.0. Section added in Clause 6 relating to transparent application, derived from XFP specification. Parameters added re DC coupling option, derived from OIF2003.129     |

| OIF 2003.104.02 | 24th May 2003      | Draft 3.0. Updated to include approved changes from the OIF Plenary meeting in Scottsdale, 6-8 May 2003                                                                                                                                          |

| OIF 2003.104.03 | 2nd October 2003   | Draft 4.0. Updated to include changes as results of comment resolution from CEI Straw ballot (ballot#41), approved at the Ottawa meeting July 2003                                                                                               |

| OIF 2003.104.04 | 17th November 2003 | Draft 4.1. As draft 4.0 but including changes approved at the Berlin interim/plenary meetings 13 - 16 October 2003. These changes are summarized in OIF2003.326.03.                                                                              |

| OIF2003.104.05  | 10th February 2004 | Draft 5.0. Updated to include changes as results of comment resolution from the second CEI Straw ballot (ballot#49), approved at the San Diego meeting January 2004                                                                              |

| OIF2003.104.06  | 5th May 2004       | Draft 6.0. Updated to include changes as result of comment resolution from 3rd Straw ballot (ballot no 52), as approved at the Orlando Interim meeting March 15th 2004.                                                                          |

| OIF2003.104.07  | 14th July 2004     | Draft 7.0. As Draft 6.0, but updated to include changes approved at the Budapest Plenary meeting. Clause 2 reconstructed and SXI-5 and TFI-5 interfaces described as new clauses 4 and 5. Previous clauses 4,5,6 are renumbered as clauses 6,7,8 |

| OIF2003.104.08  | 26th August 2004   | Clause 8 modified to include changes agreed at the Hawaii Plenary meeting, to address discrepancies between CEI and XFP specifications.                                                                                                          |

| OIF2003.104.09  | 20th October 2004  | Draft 9.0. Updated to include changes as result of comment resolution from 4th Straw ballot (ballot no 55),                                                                                                                                      |

| OIF2003.104.10  | 8th November 2004  | Draft 10.0. As draft 9.0 with specific reference to version no of State Eye scripts in section 2.C.5 removed.                                                                                                                                    |

This revision was published as OIF-CEI-01.00 in December 2004.

The OIF document 2003.253 was the working document used for the development of the CEI-11G-MR and CEI-11G-LR interfaces. The history of this document is detailed in the table below:

| Revision        | Date              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2003.253.00 | 20th July 2003,   | Draft 1.0. Compiled from baseline document oif2002.127.0 with changes and modifications from Scottsdale motions                                                                                                                                                                                                                                                                                                                                                       |

| OIF 2003.253.01 | 5th October 2003  | Draft 1.1. adding changes and modifications from the July 2003 meeting in Ottawa.  - New entries for table 1-1 moved to OIF2003.104.  - Removed figure 1-1, table 1-2 and sections 1.8 and 3.2.10.  - Moved appendix 3B to OIF2003.104  - Changed 7.2.8, 8 Taps down to 4 Taps  - Changed 7.1 to required BER of 1e-15                                                                                                                                                |

| OIF 2003.253.02 | 9th November 2003 | Draft 2.0. adding changes and modifications from the October 2003 meeting in Berlin.                                                                                                                                                                                                                                                                                                                                                                                  |

| OIF2003.253.03  | 2nd February 2004 | Draft 2.1 resolving comments from Straw ballot #50, motions and resolutions as agreed in the San Diego 2004 meeting. Corrections include:  - DC coupling introduced with VTT = 1.2V  - Channel compliance, section 7.2.7 - with introduction of reference transmitter and -receiver.  - Changes in transmit amplitude to 1200mVppd max  Comment resolution spread sheet, OIF2004.054.03  Clause 7 Editors report, OIF2004.053.01  PLL Meeting motions: OIF2004.076.00 |

| OIF2003.253.04  | 3rd May 2004      | Draft 2.2 resolving comments from straw ballot 53 and orlando interim meeting, March 15th. Corrections include  - DC coupling editorials  - Tap weight clarification  - T_Y1 = 400 mVpp, T_Y2 = 600mVpp  - driver and receiver absolute min and max voltages  - Return loss alignment to 6G-LR                                                                                                                                                                        |

| OIF2003.252.05  | 6 September 2004  | Draft 2.3 including motions from Budapest and Hawaii meetings:  - Changed clause no from 7 to 9  - Changed values in Table 9-1 and 9-8d  - Changed reference receiver B definitions  - Added appendix B, the StatEye.org template.                                                                                                                                                                                                                                    |

| OIF2003.253.06  | 6 December 2004   | Draft 3.0 including the motions from the Alexandria meeting, October 26-28 - Added CEI-11G-MR - Further specification of Reference Receiver B - StatEye templates for -LR Ref Receiver A and B and for -MR                                                                                                                                                                                                                                                            |

| OIF2003.253.06  | 25 January 2005   | Draft 3.1 includes corrections to table 9.11 following discussions and motion from the Dallas meeting, 18-20 January 2005.  Source documents uploaded as OIF2005.090.00                                                                                                                                                                                                                                                                                               |

This revision was published as OIF-CEI-02.00 in February 2005.

The OIF document 2011.004 was the working document used for the development of maintenance updates to OIF-CEI-02.00. The comment resolution for this update is contained in 2011.121. These updates were published as part of OIF-CEI-03.00 in August 2011.

Implementation Agreement OIF-CEI-05.0

The OIF document 2008.029 was the working document used for the development of the CEI-28G-SR interface defined in clause 10. The history of this document is detailed in the table below:

| Revision        | Date                          | Description                                                                                                                                                                                                                               |

|-----------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2008.029.03 | 28th July 2008,               | Document taken over from Beth Donnay                                                                                                                                                                                                      |

| OIF 2008.029.04 | 23rd April 2009               | Inserted text for all tbd locations according to work session results of Q2/09 meeting in Boston                                                                                                                                          |

| OIF 2008.029.05 | 23rd April 2009               | Finalized text proposal after continued discussion in Q2/09 meeting in Boston. Text proposal sent to Straw Ballot in Boston                                                                                                               |

| OIF 2008.029.06 | 23rd July 2009                | oif2009.129.02: Comment resolution according CEI-28-SR/25-LR Editors Report Finalized text proposal after continued discussion in Q3/09 meeting in Vancouver. Text proposal sent to Straw Ballot in Vancouver                             |

| OIF 2008.029.07 | 15th October 2009             | oif2009.280.03: Comment Resolution Worksheet for CEI-28-SR Finalized text proposal after continued discussion in Q4/09 meeting in Lannion. Text proposal sent to Straw Ballot in Lannion and sent as liaison to IEEE 802.3ba for comments |

| OIF 2008.029.08 | 21st May 2010                 | oif2009.408.01: Comment Resolution Worksheet for CEI-28-SR Finalized text proposal after continued discussion in Q2/10 meeting in Hong Kong. Text proposal sent to Straw Ballot in electronic motion after Hong Kong meeting.             |

| OIF 2008.029.09 | 25th August 2010              | oif2010.239.01: Comment Resolution Worksheet for CEI-28-SR Finalized text proposal after continued discussion in Q3/10 meeting in Baltimore. Text proposal sent to Straw Ballot in electronic motion after Baltimore meeting.             |

| OIF 2008.029.10 | 16th November 2010            | oif2010.337.02: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q4/10 meeting in Nuremberg. Text proposal sent to Straw Ballot in electronic motion after Nuremberg meeting              |

| OIF 2008.029.11 | 14th February 2011            | oif2010.452.01: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q1/11 meeting in Dallas. Text proposal sent to Straw Ballot in electronic motion after Dallas meeting                    |

| OIF 2008.029.12 | 7th April 2011                | oif2011.129.04: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q2/11 meeting in Glasgow. Text proposal sent to Straw Ballot during Glasgow meeting with option for Principal.           |

| OIF 2008.029.13 | OIF 2008.029.13 3rd June 2011 | oif2011.198.01: Comment Resolution Worksheet for CEI-25/28 Resolution of LSI, Qlogic Straw Ballot comments. Text proposal sent to another Straw Ballot in electronic motion.                                                              |

|                 |                               | oif2011.271.01: Comment Resolution Worksheet for CEI-25/28  Document sent to principal member ballot at Philadelphia meeting                                                                                                              |

The OIF document 2008.161 was the working document used for the development of the CEI-25G-LR interface defined in clause 11. The history of this document is detailed in the table below:

| Revision        | Date               | Description                                                                                                                                                                                                                                                                                              |

|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2008.161.03 | 28th July 2008,    | Document taken over from Beth Donnay                                                                                                                                                                                                                                                                     |

| OIF 2008.161.04 | 23rd April 2009    | Inserted text for all tbd locations according to work session results of Q2/09 meeting in Boston                                                                                                                                                                                                         |

| OIF 2008.161.05 | 23rd April 2009    | Finalized text proposal after continued discussion in Q2/09 meeting in Boston. Text proposal sent to Straw Ballot in Boston                                                                                                                                                                              |

| OIF 2008.161.06 | 23rd July 2009     | oif2009.129.02: Comment resolution according CEI-28-SR/25-LR Editors Report Finalized text proposal after continued discussion in Q3/09 meeting in Vancouver. Text proposal sent to Straw Ballot in Vancouver                                                                                            |

| OIF 2008.161.07 | 15th October 2009  | oif2009.281.02: Comment Resolution Worksheet for CEI-25-LR Finalized text proposal after continued discussion in Q4/09 meeting in Lannion. Text proposal sent to Straw Ballot in Lannion and sent as liaison to IEEE 802.3ba for comments                                                                |

| OIF 2008.161.08 | 21st May 2010      | oif2009.409.01: Comment Resolution Worksheet for CEI-25-LR Finalized text proposal after continued discussion in Q2/10 meeting in Hong Kong. Text proposal sent to Straw Ballot in electronic motion after Hong Kong meeting.                                                                            |

| OIF 2008.161.09 | 25th August 2010   | oif2010.240.01: Comment Resolution Worksheet for CEI-25-LR Finalized text proposal after continued discussion in Q3/10 meeting in Baltimore. Text proposal sent to Straw Ballot in electronic motion after Baltimore meeting.                                                                            |

| OIF 2008.161.10 | 16th November 2010 | oif2010.337.02: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q4/10 meeting in Nuremberg. Text proposal sent to Straw Ballot in electronic motion after Nuremberg meeting                                                                             |

| OIF 2008.161.11 | 14th February 2011 | oif2010.452.01: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q1/11 meeting in Dallas. Text proposal sent to Straw Ballot in electronic motion after Dallas meeting                                                                                   |

| OIF 2008.161.12 | 7th April 2011     | oif2011.129.04: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q2/11 meeting in Glasgow. Text proposal sent to Straw Ballot during Glasgow meeting with option for Principal.                                                                          |

| OIF 2008.161.13 | 3rd June 2011      | oif2011.198.01: Comment Resolution Worksheet for CEI-25/28 Resolution of LSI, Qlogic Straw Ballot comments. Text proposal sent to another Straw Ballot in electronic motion. oif2011.271.01: Comment Resolution Worksheet for CEI-25/28 Document sent to principal member ballot at Philadelphia meeting |

The OIF document 2010.189 was the working document used for the development of the Test Methodologies for CEI-28G-SR and CEI-25G-LR defined in clause 12. The history of this document is detailed in the table below:

Implementation Agreement OIF-CEI-05.0

| Revision        | Date               | Description                                                                                                                                                                                                                     |

|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2010.189.00 | 12th May 2010      | Separate Clause extracted for common 'TX Jitter and Channel Compliance Methodologies for CEI-28G-SR and CEI-25G-LR' in Q2/10 meeting in Hong Kong.                                                                              |

| OIF 2010.189.01 | 12th May 2010      | Modifications during Hong Kong meeting                                                                                                                                                                                          |

| OIF 2010.189.02 | 21st May 2010      | Editorial changes of PLL chair, see change bars Text proposal sent to Straw Ballot in electronic motion after Hong Kong meeting.                                                                                                |

| OIF 2010.189.03 | 25th August 2010   | oif2010.241.01: Comment Resolution Worksheet for Clause 12 Finalized text proposal after continued discussion in Q3/10 meeting in Baltimore. Text proposal sent to Straw Ballot in electronic motion after Baltimore meeting.   |

| OIF 2010.189.04 | 16th November 2010 | oif2010.337.02: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q4/10 meeting in Nuremberg. Text proposal sent to Straw Ballot in electronic motion after Nuremberg meeting    |

| OIF 2010.189.05 | 14th February 2011 | oif2010.452.01: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q1/11 meeting in Dallas. Text proposal sent to Straw Ballot in electronic motion after Dallas meeting          |

| OIF 2010.189.06 | 7th April 2011     | oif2011.129.04: Comment Resolution Worksheet for CEI-25/28 Finalized text proposal after continued discussion in Q2/11 meeting in Glasgow. Text proposal sent to Straw Ballot during Glasgow meeting with option for Principal. |

| OIF 2010.189.07 | 3rd June 2011      | oif2011.198.01: Comment Resolution Worksheet for CEI-25/28<br>Resolution of LSI, Qlogic Straw Ballot comments. Text proposal sent to<br>another Straw Ballot in electronic motion.                                              |

|                 |                    | oif2011.271.01: Comment Resolution Worksheet for CEI-25/28  Document sent to principal member ballot at Philadelphia meeting                                                                                                    |

The combined revision including changes of above documents was published as OIF-CEI-03.00 in September 2011.

The OIF document oif2013.329 was the working document used for the development of maintenance updates to OIF-CEI-03.00. The comment resolution for this update is contained in oif2014.051. These updates were published as part of OIF-CEI-05.0 in October 2013.

The OIF document 2010 404 was the working document used for the development of

The OIF document 2010.404 was the working document used for the development of the CEI-28G-VSR interface defined in clause 13. The history of this document is detailed in the table below:

| Revision        | Date                | Description                                                                 |

|-----------------|---------------------|-----------------------------------------------------------------------------|

| OIF 2010.404.00 | 26th October 2010,  | Baseline text proposal                                                      |

| OIF 2010.404.01 | 28th October 2010,  | Updated baseline text proposal                                              |

| OIF 2010.404.02 | 26th May 2011       | Updated baseline text proposal                                              |

| OIF 2010.404.03 | 14th July 2011      | Updated baseline text proposal                                              |

| OIF 2010.404.04 | 27th July 2011      | oif2011.180.00: VSR change document                                         |

| OIF 2010.404.05 | 2nd December 2011   | oif2011.411.02: VSR editor report                                           |

| OIF 2010.404.06 | 12th March 2012     | oif2012.055.01: VSR editor report -05                                       |

| OIF 2010.404.07 | 14th May 2012       | oif2012.164.02: VSR rev6-0 editor recommendations                           |

| OIF 2010.404.08 | 18th October 2012   | oif2012.253.02: CEI-28G-VSR draft 7 comment summary                         |

| OIF 2010.404.09 | 6th February 2013   | oif2013.036.02: VSR editor report Jan 2013                                  |

| OIF 2010.404.10 | 21st May 2013       | oif2013.150.01: CEI-28G-VSR 9-0 comment summary with editor recommendations |

| OIF 2010.404.11 | 25th July 2013      | oif2013.255.02: CEI-28G-VSR rev10-0 editor report                           |

| OIF 2010.404.12 | 17th September 2013 | oif2013.317.00: Working document for CEI VSR draft 11-1                     |

| OIF 2010.404.13 | 18th September 2013 | Wrong file uploaded                                                         |

| OIF 2010.404.14 | 18th September 2013 | oif2013.380.01: CEI-28G-VSR 14-0 comments                                   |

| OIF 2010.404.15 | 30th October 2013   | oif2014.068.00: CEI-VSR rev 0-15 comments                                   |

The OIF document 2013.066 was the working document used for the development of the CEI-28G-MR interface defined in clause 14. The history of this document is detailed in the table below:

| Revision        | Date                | Description                                           |

|-----------------|---------------------|-------------------------------------------------------|

| OIF 2013.066.00 | 17th January 2013   | oif2013.037.01: MR editor report Jan 2013             |

| OIF 2013.066.01 | 21st May 2013       | oif2013.162.02: MR 1-0 comment resolution spreadsheet |

| OIF 2013.066.02 | 25th July 2013      | oif2013.254.03: CEI-28G-MR rev2-0 editors report      |

| OIF 2013.066.03 | 17th September 2013 | Final version                                         |

The combined revision including changes of above documents was published as OIF-CEI-03.01 in February 2014.

The OIF document oif2017.059 was the working document used for the development of maintenance updates to OIF-CEI-03.01 according worklist in oif2015.001.02. The comment resolution for this update is contained in oif2017.321. These updates were published as part of OIF-CEI-04.0 in December 2017.

The OIF document 2014.230 was the working document used for the development of the CEI-56G-VSR-PAM4 interface defined in clause 16. The history of this document is detailed in the table below:

Implementation Agreement OIF-CEI-05.0

| Revision        | Date       | Description                                                                                |

|-----------------|------------|--------------------------------------------------------------------------------------------|

| OIF 2014.230.00 | 07/21/2014 | Baseline Text Proposal                                                                     |

| OIF 2014.230.01 | 10/22/2014 | oif2014.372.00 CEI-56G-VSR-PAM4 Editor's report                                            |

| OIF 2014.230.02 | 02/06/2015 | oif2014.443.02 CEI-56G-VSR-PAM4 comments resolution spreadsheet                            |

| OIF 2014.230.03 | 05/08/2015 | oif2015.144.02 CEI-56G-VSR-PAM4 comment and resolution spreadsheet                         |

| OIF 2014.230.04 | 09/09/2015 |                                                                                            |

| OIF 2014.230.05 | 11/06/2015 | oif2015.492.01CEI-56G-VSR/XSR-PAM4 comment and resolution spreadsheets                     |

| OIF 2014.230.06 | 02/22/2016 | oif2016.004.04 CEI-56G-VSR/XSR-PAM4 comment and resolution spreadsheets                    |

| OIF 2014.230.07 | 06/10/2016 | oif2016.128.05 Prague CEI-56G-VSR/XSR-PAM4 comment and resolution spreadsheets             |

| OIF 2014.230.08 | 09/13/2016 | oif2016.252.04 Quebec City CEI-56G-VSR-PAM4 comment and resolution spreadsheet             |

| OIF 2014.230.09 | 11/18/2016 | oif2016.402.03 Auckland CEI-56G-VSR-PAM4 comment and resolution spreadsheet                |

| OIF 2014.230.10 | 02/17/2017 | oif2017.027.01 San Jose CEI-56G-VSR-PAM4 comment and resolution spreadsheet                |

| OIF 2014.230.11 | 06/06/2017 | oif2017.148.02 Ljub. CEI-56G-VSR-PAM4 comment and resolution spreadsheet                   |

| OIF 2014.230.12 | 09/25/2017 | oif2017.333.02 Halifax CEI-56G-VSR-PAM4 comment and resolution spreadsheet                 |

| OIF 2014.230.13 | 11/01/2017 | Final version: oif2017.492.01 Shanghai CEI-56G-VSR-PAM4 comment and resolution spreadsheet |

The OIF document 2014.245 was the working document used for the development of the CEI-56G-MR-PAM4 interface defined in clause 17. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                                                                             |

|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2014.245.00 | 07/21/2014 | Baseline Text Proposal                                                                                                                  |

| OIF 2014.245.01 | 10/22/2014 | oif2014.247.00 Method and Highlights for Creating a CEI-56G-MR Baseline Proposal                                                        |

| OIF 2014.245.02 | 03/08/2015 | oif2014.444.03 CEI-56G-MR comment and resolution spreadsheet                                                                            |

| OIF 2014.245.03 | 05/13/2015 | oif2015.198.02 Editor's initial responses to the comments received against CEI-56G-MR spec (OIF2014.245.02) ballot                      |

| OIF 2014.245.04 | 09/11/2015 | oif2015.358.02 CEI-56G-MR-PAM4 comment resolution spreadsheet - OIF Q3/2015 Meeting                                                     |

| OIF 2014.245.05 | 12/13/2015 | oif2015.504.02 Editor's initial responses to comments and resolutions against the CEI-56G-MR-PAM4 (i.e., oif2014.245.04.pdf) spec draft |

| OIF 2014.245.06 | 04/03/2016 | oif2016.060.02 Editor's initial responses to comments and resolutions against the CEI-56G-MR-PAM4 (i.e., oif2014.245.05.pdf) spec draft |

| OIF 2014.245.07 | 06/28/2016 | oif2016.194.03 Editor's initial responses to comments and resolutions                                                                   |

| OIF 2014.245.08 | 09/27/2016 | oif2016.331.02 Editor's Responses for Comment Resolution for CEI-56G-MR-PAM4 (oif2014.245.07)                                           |

| Revision        | Date       | Description                                                                                                                     |

|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| OIF 2014.245.09 | 12/12/2016 | oif2016.446.02 Editor's initial responses to CEI-56G-MR-PAM4 comments and resolutions                                           |

| OIF 2014.245.10 | 04/09/2017 | oif2017.082.02 Editor's responses to CEI-56G-MR-PAM4 comments and resolutions (Q1/2017)                                         |

| OIF 2014.245.11 | 06/27/2017 | oif2017.233.03 Editor's responses to CEI-56G-MR-PAM4 comments and resolutions (Q2/2017)                                         |

| OIF 2014.245.12 | 08/25/2017 | oif2017.419.02 Editor's responses to CEI-56G-MR-PAM4 comments and resolutions (Q3/2017)                                         |

| OIF 2014.245.13 | 11/01/2017 | Final version: oif2017.563.02 Worksheet with editor's comment&resolution pre-Q4/17 meeting for CEI-56G-MR-PAM4 (oif2014.245.12) |

The OIF document 2014.267 was the working document used for the development of the CEI-56G-USR-NRZ interface defined in clause 18. The history of this document is detailed in the table below:

| Revision        | Date         | Description                                                             |

|-----------------|--------------|-------------------------------------------------------------------------|

| OIF 2014.267.00 | 07/25/2014   | Baseline Text Proposal                                                  |

| OIF 2014.267.01 | 10/14/2014   | oif2014.304.00 CEI 56G USR Editorial Comments on oif2014.267.00         |

| OIF 2014.267.02 | 10/21/2014   | oif2014.369.00 Editors report for 56G-USR                               |

| OIF 2014.267.03 | 01/22/2015   | oif2015.002.03 CEI-56G-USR-NRZ comment and resolution spreadsheet       |

| OIF 2014.267.04 | 04/22/2015   | oif2015.103.02 CEI-56G-USR Version3 comment and resolution spreadsheet  |

| OIF 2014.267.05 | 07/29/2015 D | oif2015.254.01 CEI-56G-USR Version4 comment and resolution spreadsheet  |

| OIF 2014.267.06 | 11/05/2015   | oif2015.472.02 CEI-56G-USR-NRZ Comment Resolution                       |

| OIF 2014.267.07 | 01/27/2016   | oif2016.038.03 CEI-56G-USR-NRZ Comment Resolution                       |

| OIF 2014.267.08 | 05/10/2016   | oif2016.121.02 CEI-56G-USR-NRZ Comment Resolution 07                    |

| OIF 2014.267.09 | 08/10/2016   | oif2016.267.02 Comment resolution for CEI-56G-USR-NRZ 08                |

| OIF 2014.267.10 | 10/31/2016   | oif2016.363.03 Comment resolution for CEI-56G-USR-NRZ 09                |

| OIF 2014.267.11 | 01/17/2017   | Final Version: oif2016.485.01 Comment resolution for CEI-56G-USR-NRZ 10 |

The OIF document 2014.268 was the working document used for the development of the CEI-56G-XSR-NRZ interface defined in clause 19. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                |

|-----------------|------------|----------------------------------------------------------------------------|

| OIF 2014.268.00 | 07/25/2014 | Baseline Text Proposal                                                     |

| OIF 2014.268.01 | 10/14/2014 | oif2014.305.00 CEI 56G XSR Editorial Comments on oif2014.268.00            |

| OIF 2014.268.02 | 10/21/2014 | oif2014.370.00 Editors report for CEI-56G-XSR-NRZ                          |

| OIF 2014.268.03 | 01/22/2015 | oif2015.003.04 CEI-56G-XSR-NRZ comment and resolution spreadsheet          |

| OIF 2014.268.04 | 04/22/2015 | oif2015.102.02 CEI-56G-XSR-NRZ Version3 comment and resolution spreadsheet |

| OIF 2014.268.05 | 07/29/2015 | oif2015.255.01 CEI-56G-XSR-NRZ Version4 comment and resolution spreadsheet |

| OIF 2014.268.06 | 11/05/2015 | oif2015.476.02 CEI-56G-XSR-NRZ Comment Resolution                          |

| OIF 2014.268.07 | 01/27/2016 | oif2016.043.04 CEI-56G-XSR-NRZ Comment Resolution                          |

| OIF 2014.268.08 | 05/10/2016 | oif2016.123.02 CEI-56G-XSR-NRZ Comment Resolution 07                       |

| Revision        | Date       | Description                                                             |

|-----------------|------------|-------------------------------------------------------------------------|

| OIF 2014.268.09 | 08/10/2016 | oif2016.269.01 Comment resolution for CEI-56G-XSR-NRZ 08                |

| OIF 2014.268.10 | 10/31/2016 | oif2016.364.02 Comment resolution for CEI-56G-XSR-NRZ 09                |

| OIF 2014.268.11 | 01/17/2017 | Final Version: oif2016.486.01 Comment resolution for CEI-56G-XSR-NRZ 10 |

Implementation Agreement OIF-CEI-05.0

The OIF document 2014.380 was the working document used for the development of the CEI-56G-LR-PAM4 interface defined in clause 21. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                                                                             |

|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| OIF 2014.380.00 | 10/18/2014 | Baseline Text Proposal                                                                                                                  |

| OIF 2014.380.01 | 04/18/2015 | oif2014.381.03 Method and Highlights for Creating a PAM-4 Baseline Proposal for CEI-56G-LR                                              |

| OIF 2014.380.02 | 04/03/2016 | oif2015.505.01 Editor's initial responses to comments and resolutions against the CEI-56G-LR-PAM4 (i.e., oif2014.380.01.pdf) spec draft |

| OIF 2014.380.03 | 06/28/2016 | oif2016.205.02 Editor's initial responses to CEI-56G-LR-PAM4 comments and resolutions                                                   |

| OIF 2014.380.04 | 09/28/2016 | oif2016.334.03 Editor's Responses for Comment Resolution for CEI-56G-LR-PAM4 (oif2014.380.03)                                           |

| OIF 2014.380.05 | 12/12/2016 | oif2016.447.02 Editor's initial responses to CEI-56G-LR-PAM4 comments and resolutions (Q4/16)                                           |

| OIF 2014.380.06 | 04/09/2017 | oif2017.083.02 Editor's responses to CEI-56G-LR-PAM4 comments and resolutions (Q1/2017)                                                 |

| OIF 2014.380.07 | 06/27/2017 | oif2017.234.02 Editor's responses to CEI-56G-LR-PAM4 comments and resolutions (Q2/2017)                                                 |

| OIF 2014.380.08 | 08/25/2017 | oif2017.420.02 Editor's responses to CEI-56G-LR-PAM4 comments and resolutions (Q3/2017)                                                 |

| OIF 2014.380.09 | 11/01/2017 | Final version: oif2017.564.02 Worksheet with editor's comment&resolution pre Q4/17 meeting for CEI-56G-LR-PAM4 (oif2014.380.08)         |

The OIF document 2014.364 was the working document used for the development of the CEI-56G-LR-ENRZ interface defined in clause 22. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                         |

|-----------------|------------|-------------------------------------------------------------------------------------|

| OIF 2014.364.00 | 10/13/2014 | Baseline Text Proposal                                                              |

| OIF 2014.364.01 | 01/14/2015 | oif2015.046.00 CEI-56G-LR ENRZ Proposal Updates                                     |

| OIF 2014.364.02 | 04/12/2015 | oif2015.046.00 CEI-56G-LR ENRZ Proposal Updates                                     |

| OIF 2014.364.03 | 07/30/2015 | oif2015.341.00 CEI-56G-LR-ENRZ Proposed Updates to Baseline Text                    |

| OIF 2014.364.04 | 01/28/2016 | oif2015.440.01 CEI-56G-LR-ENRZ Comment Resolution 4Q2015                            |

| OIF 2014.364.05 | 05/12/2016 | Final version: oif2016.155.00 CEI-56G-LR-ENRZ Comment Resolution Spreadsheet 2Q2016 |

The OIF document oif2018.360 was the working document used for the development of maintenance updates to OIF-CEI-04.00 according worklists in oif2018.007.03 and oif2020.015.06. These updates were published as part of OIF-CEI-05.0 in February 2022.

The OIF document 2014.286.18 was the working document used for the development of the CEI-56G-XSR-PAM4 interface defined in clause 20. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                                 |

|-----------------|------------|---------------------------------------------------------------------------------------------|

| OIF 2014.286.00 | 07/30/2014 | Baseline Text Proposal                                                                      |

| OIF 2014.286.01 | 07/30/2014 | Baseline Text Proposal Update                                                               |

| OIF 2014.286.02 | 07/31/2014 | Baseline Text Proposal Update                                                               |

| OIF 2014.286.3  | 07/31/2014 | Baseline Text Proposal Update                                                               |

| OIF 2014.286.04 | 10/22/2014 | oif2014.340.00 updates to CEI-56G-XSR-PAM4 baseline                                         |

| OIF 2014.286.05 | 02/06/2015 | oif2015.021.02 CEI-56G-XSR-PAM4 comments resolution spreadsheet                             |

| OIF 2014.286.06 | 06/01/2015 | oif2015.143.01 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.07 | 09/09/2015 | oif2015.387.01 Working copy of CEI-56G-XSR-PAM4 (post-Ottawa meeting)                       |

| OIF 2014.286.08 | 11/19/2015 | oif2015.492.01 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.09 | 03/07/2016 | oif2016.004.04 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.10 | 06/15/2016 | oif2016.128.05 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.11 | 09/15/2016 | oif2016.252.04 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.12 | 11/21/2016 | oif2016.403.04 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.13 | 02/17/2017 | oif2017.028.01 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.14 | 06/06/2017 | oif2017.149.02 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.15 | 08/25/2017 | oif2017.334.02 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.16 | 11/01/2017 | oif2017.493.01 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.17 | 02/23/2018 | oif2017.611.04 CEI-56G-XSR-PAM4 comment and resolution spreadsheet                          |

| OIF 2014.286.18 | 04/25/2018 | Final version: oif2018.179.01 Nuremberg CEI-56G-XSR-PAM4 comment and resolution spreadsheet |

The OIF document 2017.171.08 was the working document used for the development of the CEI-112G-MCM-CNRZ interface defined in clause 23. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                |

|-----------------|------------|------------------------------------------------------------|

| OIF 2017.171.00 | 04/27/2017 | Baseline Text Proposal                                     |

| OIF 2017.171.01 | 05/09/2017 | Baseline Text Proposal Update                              |

| OIF 2017.171.02 | 07/15/2017 | Baseline Text Proposal Update                              |

| OIF 2017.171.03 | 11/01/2017 | Baseline Text Proposal Update                              |

| OIF 2017.171.04 | 04/25/2018 | oif2018.036.01 CEI-112G-MCM-CNRZ Comment Resolution 1Q2018 |

| OIF 2017.171.05 | 10/15/2018 | oif2018.285.00 CEI-112G-MCM-CNRZ Comment Resolution 3Q2018 |

| Revision        | Date       | Description                                                               |

|-----------------|------------|---------------------------------------------------------------------------|

| OIF 2017.171.06 | 10/31/2018 | oif2018.368.00 CEI-112G-MCM-CNRZ Proposed Updates to Baseline Text v4     |

| OIF 2017.171.07 | 02/21/2019 | oif2019.020.00 CEI-112G-MCM-CNRZ Comment Resolution 1Q2019                |

| OIF 2017.171.08 | 07/31/2019 | Final version: oif2019.209.00 CEI-112G-MCM-CNRZ Comment Resolution 3Q2019 |

Implementation Agreement OIF-CEI-05.0

The OIF document 2019.340.08 was the working document used for the development of the CEI-112G-MR-PAM4 interface defined in clause 26. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                       |

|-----------------|------------|-----------------------------------------------------------------------------------|

| OIF 2019.340.00 | 10/21/2019 | Baseline Text Proposal                                                            |

| OIF 2019.340.01 | 10/23/2019 | Baseline Text Proposal Update                                                     |

| OIF 2019.340.02 | 06/21/2020 | oif2020.185.02 Q2/20 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.03 | 09/17/2020 | oif2020.302.02 Q3/20 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.04 | 01/06/2021 | oif2020.445.02 Q4/20 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.05 | 02/25/2021 | oif2021.095.02 Q1/21 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.06 | 05/14/2021 | oif2021.279.02 Q2/21 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.07 | 08/06/2021 | oif2021.463.02 Q3/21 Comment Resolution Worksheet CEI-112G-MR-PAM4                |

| OIF 2019.340.08 | 11/05/2021 | Final version: oif2021.635.02 Q4/21 Comment Resolution Worksheet CEI-112G-MR-PAM4 |

The OIF document 2018.212.15 was the working document used for the development of the CEI-112G-LR-PAM4 interface defined in clause 27. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                       |

|-----------------|------------|-----------------------------------------------------------------------------------|

| OIF 2018.212.00 | 04/25/2018 | Baseline Text Proposal                                                            |

| OIF 2018.212.01 | 04/30/2018 | Baseline Text Proposal Update                                                     |

| OIF 2018.212.02 | 08/02/2018 | Baseline Text Proposal Update                                                     |

| OIF 2018.212.03 | 10/31/2018 | Baseline Text Proposal Update                                                     |

| OIF 2018.212.04 | 03/25/2019 | oif2019.074.02 Q1/19 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.05 | 07/01/2019 | oif2019.185.02 Q2/19 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.06 | 09/13/2019 | oif2019.268.02 Q3/19 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.07 | 12/10/2019 | oif2019.393.02 Q4/19 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.08 | 03/24/2020 | oif2020.084.01 Q1/20 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.09 | 06/21/2020 | oif2020.184.02 Q2/20 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.10 | 09/17/2020 | oif2020.299.02 Q3/20 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.11 | 01/06/2021 | oif2020.444.02 Q4/20 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.12 | 02/25/2021 | oif2021.096.02 Q1/21 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.13 | 05/14/2021 | oif2021.278.02 Q2/21 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.14 | 08/06/2021 | oif2021.462.02 Q3/21 Comment Resolution Worksheet CEI-112G-LR-PAM4                |

| OIF 2018.212.15 | 11/05/2021 | Final version: oif2021.634.02 Q4/21 Comment Resolution Worksheet CEI-112G-LR-PAM4 |

The OIF document 2019.065.12 was the working document used for the development of the CEI-112G-XSR-PAM4 interface defined in clause 24. The history of this document is detailed in the table below:

| Revision        | Date       | Description                                                                  |

|-----------------|------------|------------------------------------------------------------------------------|

| OIF 2019.065.00 | 02/19/2019 | Baseline Text Proposal                                                       |

| OIF 2019.065.01 | 05/11/2019 | Baseline Text Proposal Update                                                |

| OIF 2019.065.02 | 05/15/2019 | Baseline Text Proposal Update                                                |

| OIF 2019.065.03 | 12/16/2019 | oif2019.389.02 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.04 | 03/24/2020 | oif2020.078.01 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.05 | 06/21/2020 | oif2020.182.03 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.06 | 09/17/2020 | oif2020.282.03 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.07 | 01/06/2021 | oif2020.440.03 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.08 | 03/28/2021 | oif2021.094.02 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.09 | 06/07/2021 | oif2021.280.03 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.10 | 08/31/2021 | oif2021.464.02 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.11 | 11/05/2021 | oif2021.636.02 Comment Resolution Worksheet CEI-112G-XSR-PAM4                |

| OIF 2019.065.12 | 02/10/2022 | Final version: oif2022.064.02 Comment Resolution Worksheet CEI-112G-XSR-PAM4 |

## 0.2 Document Structure

Implementation Agreement OIF-CEI-05.0

The CEI document is created as a clause based document to allow for a successive completion of the document as clauses are added. This reflects the split project schedule where there are different schedules for completion different application specifications.

The first release of the document included all clauses common for the applications covered by the CEI project. These clauses were completed to cover the requirements of the included applications. Further common specifications may be included as new application clauses are added, resulting in an update of the common clauses. The process of creating the CEI document can be explained as follows:

- Prepare and complete all clauses necessary for the first release of the document, make it the master for future documents and submit it for its approval process (balloting cycles).

- 2. Follow on documents include new clauses for new functions and corrections and additions to all affected clauses of the Master document. Unchanged clauses from prior documents are not included, only deltas are listed (additions and deletions).

- 3. Once the Master document and following documents are approved it is an editorial task to merge the documents.

- 4. All requirements and specifications in the application specific clauses shall be referenced to the common clauses when appropriate.

- 5. Annexes and Appendices providing explanatory and informative text for a specific application shall be included in the corresponding clause and covered by the clause revision history. Information included in Annexes is normative with respect to the particular clause. Information included in Appendices is informative only with respect to the particular clause.

3 4

27

28

29

30

31

34

#### 0.3 List of companies belonging to the OIF when the document is approved

**Accton Technology Corporation ADVA Optical Networking** Advanced Fiber Resources (AFR) Advanced Micro Devices, Inc.

Alphawave IP Inc. Alibaba Amphenol Corp. Applied Optoelectronics, Inc.

Astera Labs Avar Labs 9 BitifEye Digital Test Solutions GmbH **Banias Labs**

10 Cadence Design Systems Broadcom Inc. 11 China Telecom CICT

12 Cisco Systems Ciena Corporation

13 Cornelis Networks, Inc. Commscope Connectivity Belgium BVBA 14

Corning Credo Semiconductor (HK) LTD 15 Dell, Inc. **DustPhotonics** 16 EFFECT Photonics B.V. **Eoptolink Technology**

17 ETRI

Epson Electronics America, Inc. 18 **EXFO**

Foxconn Interconnect Technology Ltd 19 **Fujikura** Fujitsu

20 Global Foundries Furukawa Electric Japan Global Unichip Corp (GUC) Google

22 Hakusan Inc Hewlett Packard Enterprise (HPE) 23 Hisense Broadband Multimedia Tech.Co. LTD Huawei Technologies Co., Ltd.

24 **IBM** Corporation I-Pex 25

Idea Sistemas Electronicos S.A. **II-VI** Incorporated 26

InnoLight Technology Limited Infinera Innolume GmbH Integrated Device Technology **IPG** Photonics Corporation Intel

Juniper Networks Kandou Bus

KDDI Research, Inc. Keysight Technologies, Inc. Kuaishou Technology Lumentum

32 Luminous Computing, Inc. Luxshare-ICT 33

**MACOM Technology Solutions** Marvell Semiconductor, Inc.

Maxim Integrated Inc. MaxLinear Inc. 35 Meta MediaTek

36 Microsoft Corporation Microchip Technology Incorporated 37

Mitsubishi Electric Corporation Molex 38 Multilane Inc. **NEC Corporation** 39

**NeoPhotonics** Nitto Denko Corporation 40 **NTT Corporation** Nokia 41

**NVIDIA** Corporation Nubis Communications, Inc. Open Silicon Inc. O-Net Communications (Shenzhen) Limited

43 Optomind Inc. Orange 44 PÉTRA Pointwo Technology 45

Ragile Networks, Inc. Quintessent Inc. 46 Rambus Inc. Ranovus

47 Retym Rockley Photonics 48

Rosenberger Hochfrequenztec. GmbH&Co.KG Samsung Electronics Co. Ltd. 49

Samtec Inc.

Senko Advanced Components

SiFotonics Technologies Co., Ltd.

Source Photonics, Inc.

Sumitomo Electric Industries, Ltd.

Synopsys, Inc.

Telefonica S.A.

US Conec

Wilder Technologies, LLC

ZTE Corporation

Semtech Canada Corporation

Sicoya GmbH

Socionext Inc.

Spirent Communications

Sumitomo Osaka Cement

TE Connectivity

TELUS Communications, Inc.

Viavi Solutions Deutschland GmbH

Yamaichi Electronics Ltd.

| 0 | Docum                                                                                                                       | ent Structure and Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                            |

|---|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 0.1 Re                                                                                                                      | vision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                            |

|   |                                                                                                                             | cument Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

|   |                                                                                                                             | of companies belonging to the OIF when the document is approved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

|   |                                                                                                                             | ntents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

|   |                                                                                                                             | of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

|   |                                                                                                                             | of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| 1 |                                                                                                                             | on electrical I/O project - Introduction, definitions and formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| • |                                                                                                                             | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|   |                                                                                                                             | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|   |                                                                                                                             | ectives and Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|   |                                                                                                                             | ectives and requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|   |                                                                                                                             | previations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

|   |                                                                                                                             | initions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

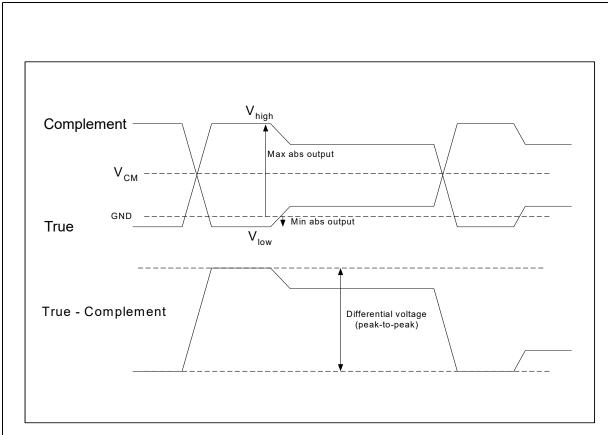

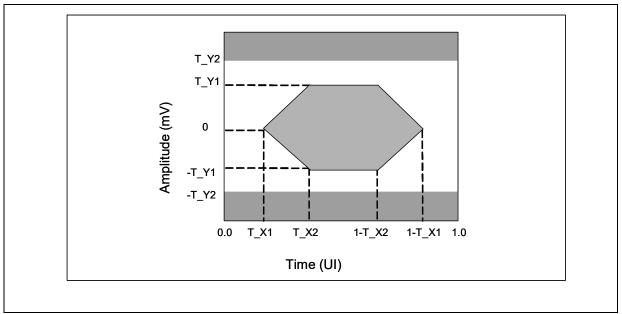

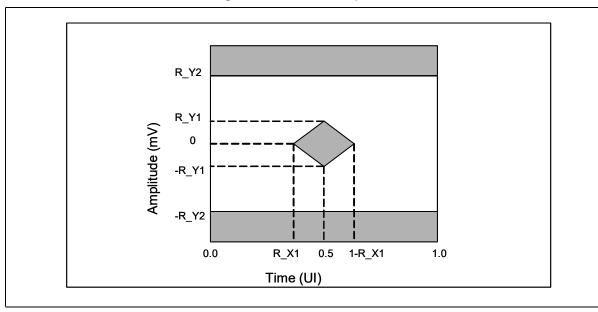

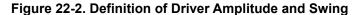

|   | 1.6.1                                                                                                                       | Definition of Amplitude and Swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

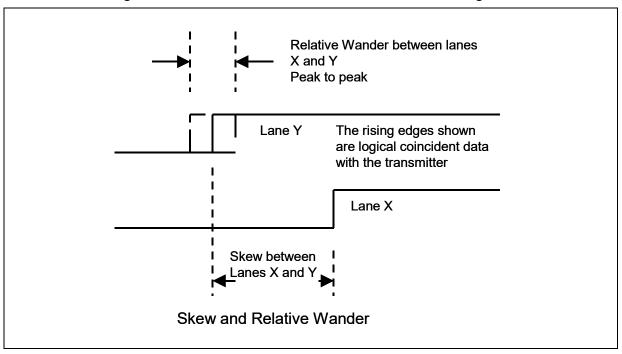

|   | 1.6.2                                                                                                                       | Definition of Skew and Relative wander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

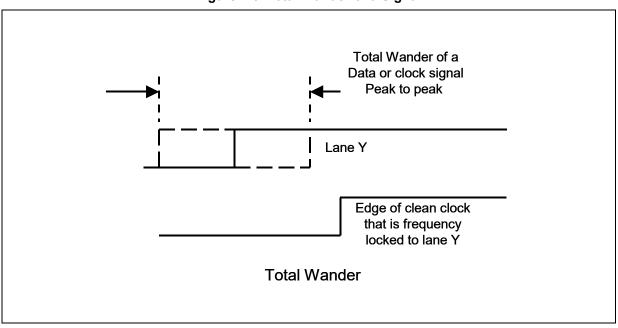

|   | 1.6.3                                                                                                                       | Definition of Total wander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |

|   |                                                                                                                             | ble Entries and Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |