# Implementation Agreement for Integrated Coherent Transmit-Receive Optical Sub Assembly

**OIF-IC-TROSA-01.0**

August 20, 2019

## Implementation Agreement created and approved OIF www.oiforum.com

The OIF is an international non-profit organization with over 100 member companies, including the world's leading carriers and vendors. Being an industry group uniting representatives of the data and optical worlds, OIF's purpose is to accelerate the deployment of interoperable, cost-effective and robust optical internetworks and their associated technologies. Optical internetworks are data networks composed of routers and data switches interconnected by optical networking elements. With the goal of promoting worldwide compatibility of optical internetworking products, the OIF actively supports and extends the work of national and international standards bodies. Working relationships or formal liaisons have been established with CFP-MSA, COBO, EA, ETSI NFV, IEEE 802.3, IETF, INCITS T11, ITU SG-15, MEF, ONF.

For additional information contact:

OIF

5177 Brandin Ct, Fremont, CA 94538 510-492-4040 ☐ info@oiforum.com

www.oiforum.com

**Working Group: PLL-OPTICS**

TITLE: IC-TROSA

SOURCE: TECHNICAL EDITOR

Scott Grindstaff

ADVA Optical Networking, NA Inc. 5775 Peachtree Industrial Boulevard

Norcross, Georgia USA 30092 Phone: +1 678 728 8723

Email: sgrindstaff@advaoptical.com

**WORKING GROUP CHAIR**

David R. Stauffer, Ph.D. Kandou Bus, S.A.

EPFL Innovation Park Bldg. I 1015 Lausanne Switzerland Phone: +1 802 316 0808 Email: david@kandou.com

**WORKING GROUP VICE CHAIR**

**Karl Gass**

Phone: +1 505 301 1511

Email: iamthedonutking@mac.com

ABSTRACT: This document details an Implementation Agreement for an Integrated Coherent Transmit-Receive Optical Sub Assembly (IC-TROSA) targeting modulation and data-rate agnostic coherent applications having nominal symbol rates up to 64Gbaud.

**Notice:** This Technical Document has been created by the Optical Internetworking Forum (OIF). This document is offered to the OIF Membership solely as a basis for agreement and is not a binding proposal on the companies listed as resources above. The OIF reserves the rights to at any time to add, amend, or withdraw statements contained herein. Nothing in this document is in any way binding on the OIF or any of its members.

The user's attention is called to the possibility that implementation of the OIF implementation agreement contained herein may require the use of inventions covered by the patent rights held by third parties. By publication of this OIF implementation agreement, the OIF makes no representation or warranty whatsoever, whether expressed or implied, that implementation of the specification will not infringe any third party rights, nor does the OIF make any representation or warranty whatsoever, whether expressed or implied, with respect to any claim that has been or may be asserted by any third party, the validity of any patent rights related to any such claim, or the extent to which a license to use any such rights may or may not be available or the terms hereof.

#### Copyright © 2019 Optical Internetworking Forum

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published and distributed, in whole or in part, without restriction other than the following, (1) the above copyright notice and this paragraph must be included on all such copies and derivative works, and (2) this document itself may not be modified in any way, such as by removing the copyright notice or references to the OIF, except as needed for the purpose of developing OIF Implementation Agreements.

By downloading, copying, or using this document in any manner, the user consents to the terms and conditions of this notice. Unless the terms and conditions of this notice are breached by the user, the limited permissions granted above are perpetual and will not be revoked by the OIF or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis and THE OIF DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY WARRANTY THAT THE USE OF THE INFORMATION HEREIN WILL NOT INFRINGE ANY RIGHTS OR ANY IMPLIED WARRANTIES OF MERCHANTABILITY, TITLE OR FITNESS FOR A PARTICULAR PURPOSE.

### **Table of Contents**

| TABL | LE OF C          | ONTENTS                                                           | 5  |

|------|------------------|-------------------------------------------------------------------|----|

| LIST | OF FIG           | URES                                                              | 7  |

| LIST | OF TAB           | ELES                                                              | 8  |

| DOC  | UMENT            | r revision history                                                | 9  |

| 1.   | Int              | roduction                                                         | 10 |

| 2.   | Fui              | nctionality                                                       | 11 |

|      | 2.1.             | Electro-Optic Architecture                                        | 11 |

|      | 2.2.             | Control and Monitoring Architecture                               | 16 |

| 3.   | Po               | wer Supply Architecture                                           | 17 |

|      | 3.1.             | Overview                                                          | 17 |

|      | 3.2.             | Primary Supply (P0)                                               | 18 |

|      | 3.3.             | Secondary Supplies (P1, P2, P3, P4, P5, P6)                       |    |

|      | 3.4.             | Low Power Mode                                                    |    |

| 4.   | Hig              | th Speed Electrical Interface                                     |    |

|      | 4.1.             | Common Features                                                   |    |

|      | 4.2.             | Allowable RF Channel Mappings                                     |    |

|      | 4.3.             | High Speed Electrical Interface for Type-1 Form Factor            |    |

|      | 4.4.             | High Speed Electrical Interface for Type-2 Mechanical Form Factor |    |

| 5.   |                  | dicated Alarm & Control I/Os                                      |    |

|      | 5.1.             | Common Alarm & Control I/Os                                       |    |

|      | 5.2.             | Type-1 Alarm & Control I/O Configuration                          |    |

|      | 5.3.             | Type-2 Alarm & Control I/O Configuration                          |    |

|      | 5.4.             | Alarm & Control Detailed Descriptions                             |    |

|      | 5.4.1.           | -= ',                                                             |    |

|      | 5.4.2.           | RESET                                                             |    |

|      | 5.4.3.           |                                                                   |    |

|      | 5.4.4.<br>5.4.5. |                                                                   |    |

|      | 5.4.5.<br>5.4.6. | _ :                                                               |    |

|      | 5.4.7.           |                                                                   |    |

|      | 5.4.8.           |                                                                   |    |

|      | 5.5.             | Alarm & Control I/O Electrical Requirements                       |    |

|      | 5.6.             | Alarm & Control I/O Timing Requirements                           |    |

| 6    |                  | w Speed Electrical Interface                                      |    |

| 0.   |                  | Low Speed Electrical Interface for Type-1 Form Factor             |    |

|      | 6.2.             | Low Speed Electrical Interface for Type-2                         |    |

|      | 6.3.             | Low Speed Connector Pin Sequence                                  |    |

| 7.   |                  | vironmental and Operating Characteristics                         |    |

| 8.   |                  | ctro-Optical Characteristics                                      |    |

|      | 8.1.             | Laser Electro-Optic Characteristics (Type-2 Only)                 |    |

|      | 8.2.             | Transmitter Electro-Optic Characteristics                         |    |

|      | 8.3.             | Receiver Electro-Optical Characteristics                          |    |

|      | 8.4.             | RF Frequency Response                                             |    |

| 9.   | Me               | echanical Specifications                                          |    |

|      | 9.1.             | General Overview and Fiber Types                                  | 56 |

|      | 9.2.             | Type-1 Mechanical Form Factor                                     |    |

|      | 9.3.             | Type-2 Mechanical Form Factor                                     | 60 |

| 10   | O. Pad           | ckaging and Mounting                                              | 63 |

|      | 10.1.            | Type-1                                                            | 63 |

| www  | w.oifor          | rum.com                                                           | 5  |

#### OIF-IC-TROSA-01.0

| 10  | ).1.1.         | Packaging, Storage, and Pre-Solder Preparation                      | 63  |

|-----|----------------|---------------------------------------------------------------------|-----|

| 10  | ).1.1.1.       | Normative Requirement                                               | 63  |

| 10  | ).1.1.2.       | Informative Recommendation                                          | 63  |

| 10  | ).1.2.         | Solder Reflow Design Reliability                                    | 63  |

| 10  | ).1.3.         | Type-1 Host Board Landing Pattern                                   | 64  |

| 10  | ).1.4.         | Type-1 Mechanical Mounting Option                                   | 65  |

| 10  | ).2.           | Type-2                                                              | 67  |

| 10  | ).2.1.         | Type-2 High Speed I/O Landing Pattern                               | 67  |

| 11. | Manag          | ement Interface                                                     | 68  |

| 11  | L. <b>1</b> .  | Management Interface Overview                                       | 68  |

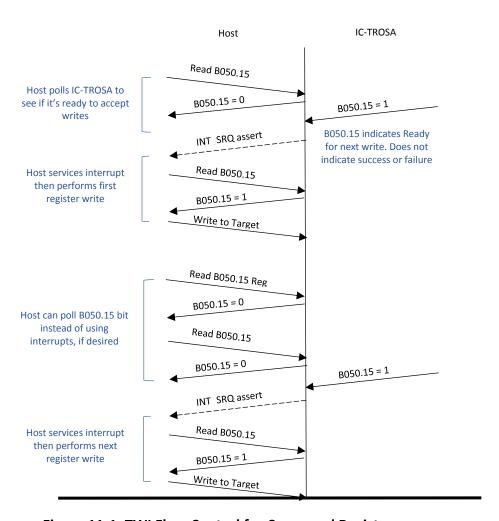

| 11  | L. <b>2</b> .  | TWI Protocol Definitions                                            | 69  |

| 11  | L.3.           | TWI Flow Control                                                    | 69  |

| 11  | L. <b>4</b> .  | Framing & Addressing                                                | 71  |

| 11  | L. <b>5</b> .  | Digital Communications Hardware Interface                           |     |

| 11  | l.5.1.         | Communications Interface Voltage and Timing Specifications          | 75  |

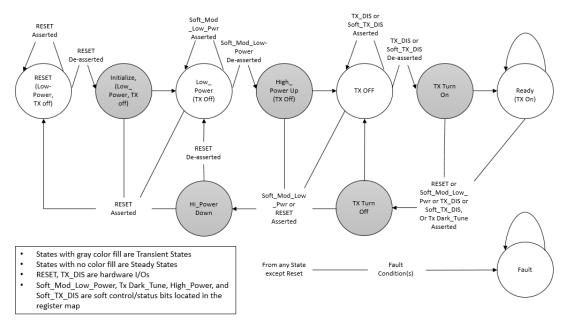

| 11  | L.6.           | State Machine                                                       | 79  |

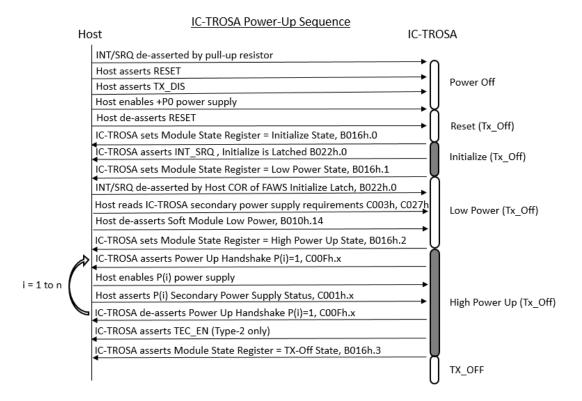

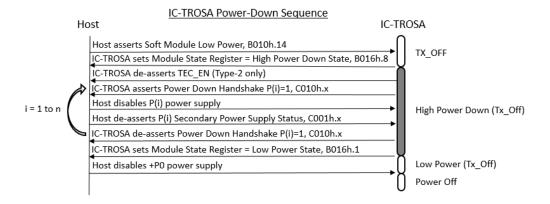

| 11  | L. <b>7</b> .  | Module Power Up/Down                                                |     |

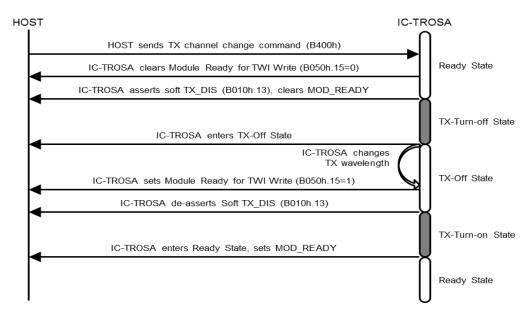

| 11  | L. <b>8.</b>   | Type-2 Tx Channel Tuning                                            |     |

| 11  | .8.1.          | Changing Tx Channel on Defined Grid ("Dark Tuning")                 | 80  |

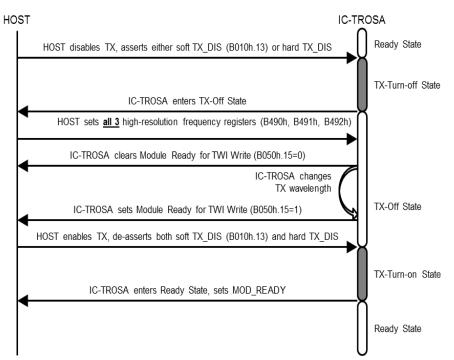

| 11  | .8.2.          | Changing Tx Channel Using High Resolution Tuning Registers          | 81  |

| 11  | L.9.           | Type-1 Tx_Turn_On                                                   | 82  |

| 11  | L. <b>10</b> . | Behavior of FAWS in IC-TROSA Module States                          |     |

| 11  | L. <b>11</b> . | Firmware Upgrades                                                   | 83  |

| 11  | .11.1.         | Firmware Upgrade Procedure                                          |     |

| 11  | .12.           | IC-TROSA Register Map                                               | 85  |

| 12. | Refere         | nces                                                                | 166 |

| 12  | 2.1.1.         | Normative references                                                | 166 |

| 12  | 2.1.2.         | Informative references                                              | 167 |

| 13. | Appen          | dix A: Glossary                                                     | 167 |

| 14. | Appen          | dix B: Additional Electro-Optical Characteristics (Informative)     | 168 |

| 15. | Appen          | dix C: Open issues / current work items                             | 168 |

| 16. | Appen          | dix D: List of companies belonging to OIF when document is approved | 168 |

#### OIF-IC-TROSA-01.0

## **List of Figures**

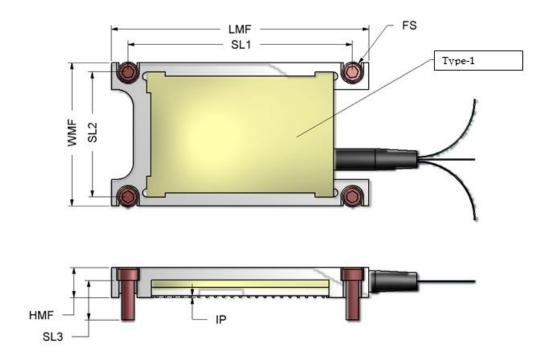

| Figure 1-1: Type-1 IC-TROSA                                                                   | 10 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 1-2: Type-2 IC-TROSA                                                                   | 10 |

| Figure 2-1: IC-TROSA Electro-Optic Functional Reference Diagram Including Optional Components | 13 |

| Figure 2-2: Coherent Detection I-Q Phase Relationship                                         | 14 |

| Figure 2-3: Type-1 Control & Monitoring Functional Diagram                                    | 16 |

| Figure 2-4: Type-2 Control & Monitoring Functional Diagram                                    |    |

| Figure 4-1: TX and RX RF Channel Mappings on the Electrical Interface                         | 21 |

| Figure 4-2: Type-1 Electrical Contact Map. Bottom View                                        | 22 |

| Figure 4-3: Type-2 High Speed Flex Interface Top View                                         | 23 |

| Figure 5-1: Type-1 Alarm & Control I/O Hardware Configuration                                 | 26 |

| Figure 5-2: Type-2 Alarm & Control I/O Hardware Configuration                                 |    |

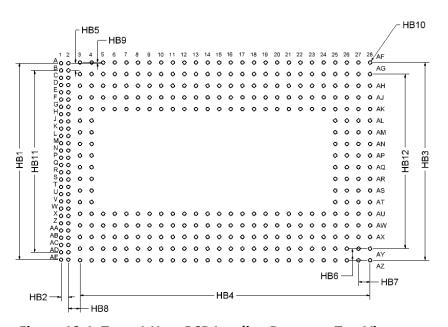

| Figure 6-1: Type-1 I/O Contact Map (Package Bottom View)                                      | 32 |

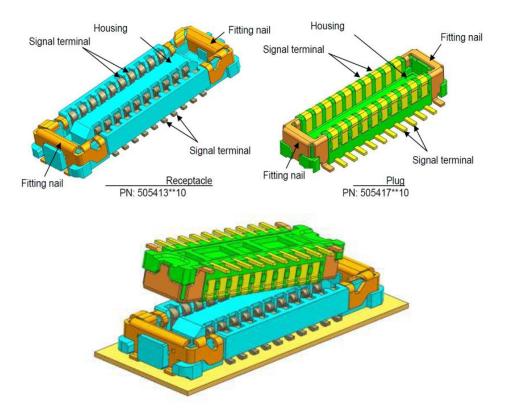

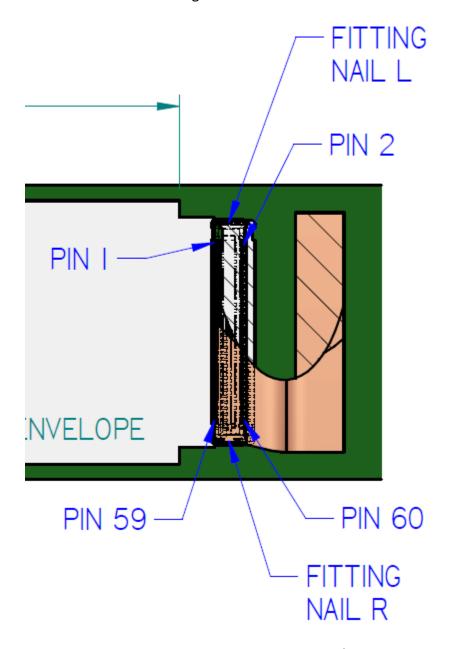

| Figure 6-2: Type-2 Low Speed SMT Connector                                                    | 43 |

| Figure 6-3: Type-2 Low Speed Host Connector Pin Designations (Top View of Package)            | 45 |

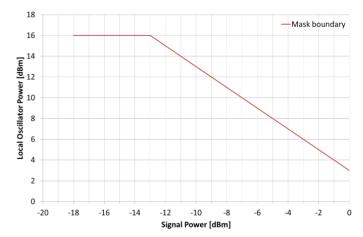

| Figure 8-1: Informative Example: Recommended Maximum LO Power Versus RX Signal Power          |    |

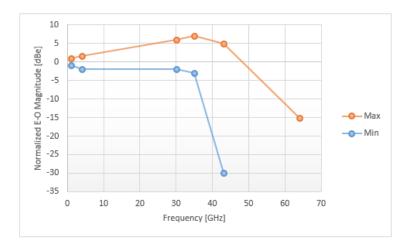

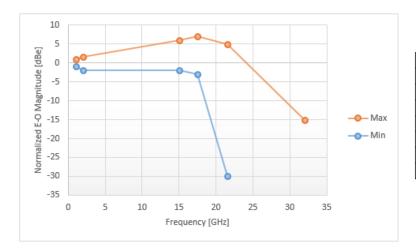

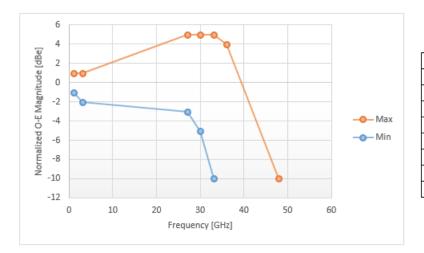

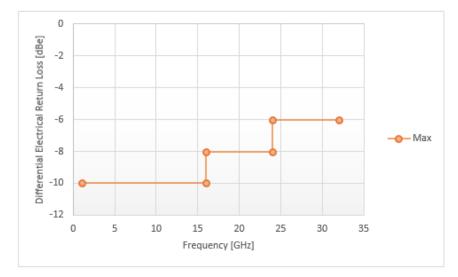

| Figure 8-2: TX Class 40, Differential S21                                                     |    |

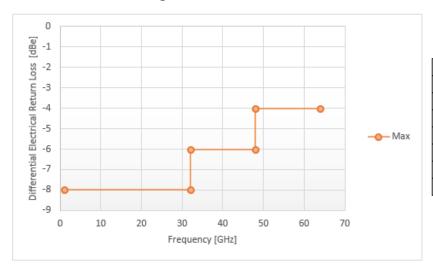

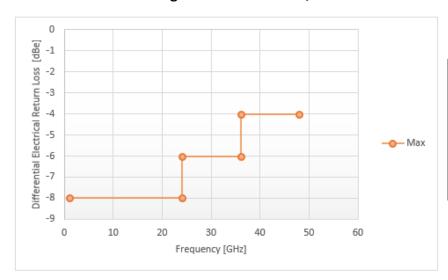

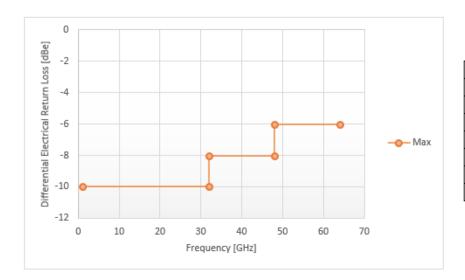

| Figure 8-3: TX Class 40, Differential S11                                                     | 51 |

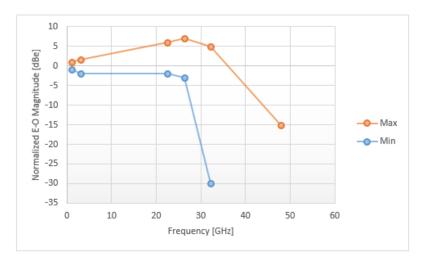

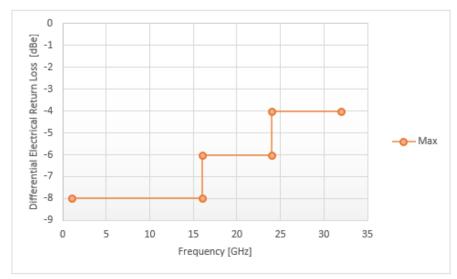

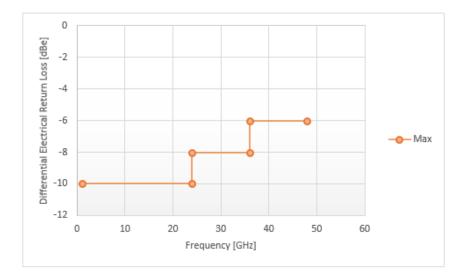

| Figure 8-4: TX Class 30, Differential S21                                                     | 52 |

| Figure 8-5: TX Class 30, Differential S11                                                     |    |

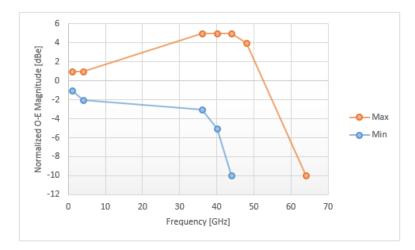

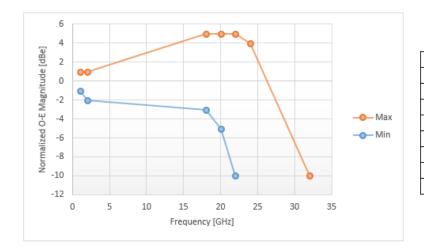

| Figure 8-6: TX Class 20, Differential S21                                                     |    |

| Figure 8-7: TX Class 20, Differential S11                                                     |    |

| Figure 8-8: RX Class 40, Differential S21                                                     | 54 |

| Figure 8-9: RX Class 40, Differential S22                                                     |    |

| Figure 8-10: RX Class 30, Differential S21                                                    |    |

| Figure 8-11: RX Class 30, Differential S22                                                    |    |

| Figure 8-12: RX Class 20, Differential S21                                                    |    |

| Figure 8-13: RX Class 20, Differential S22                                                    |    |

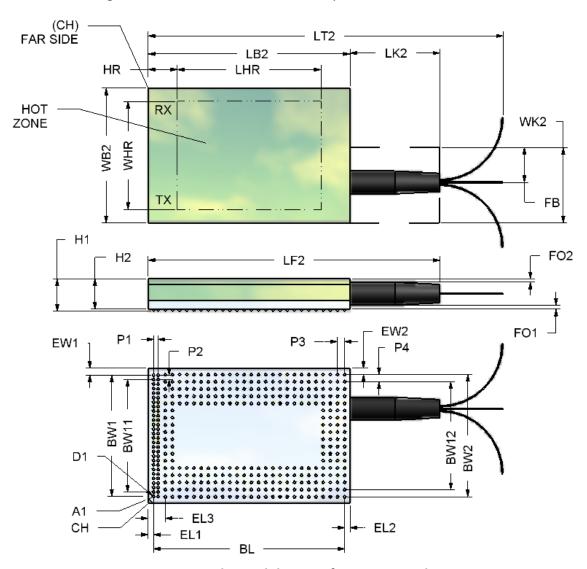

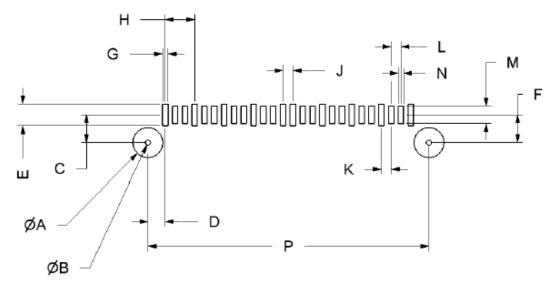

| Figure 9-1 Mechanical drawing for Type-1 package                                              |    |

| Figure 9-2: Type-2 Package with Fiber Interface and Low Speed Pin Mapping                     |    |

| Figure 9-3: Type-2 Package with LC Ferrules and Low Speed Pin Mapping                         |    |

| Figure 10-1: Type-1 Host PCB Landing Pattern – Top View                                       |    |

| Figure 10-2: Type-1 IC-TROSA with Optional Mechanical Mounting Hardware                       |    |

| Figure 10-3: Type-2 High Speed I/O Host Board Landing Pattern (Top View)                      |    |

| Figure 11-1: TWI Flow Control for Command Registers                                           |    |

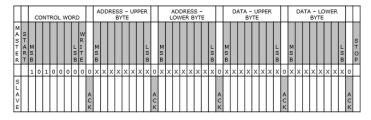

| Figure 11-2: TWI "Write" Data Frame                                                           |    |

| Figure 11-3: TWI "Sequential Write" Data Frame                                                |    |

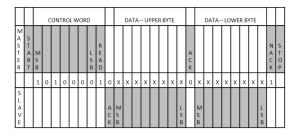

| Figure 11-4: TWI "Current Address Read" Data Frame                                            |    |

| Figure 11-5: TWI "Current Address Read" with Invalid Current Address                          |    |

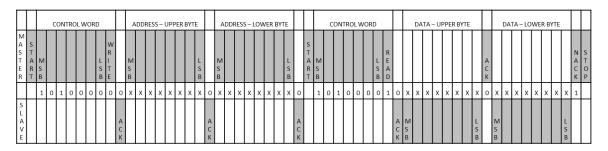

| Figure 11-6: TWI "Random Read" Data Frame                                                     |    |

| Figure 11-7: TWI "Random Read" with Invalid Address Sent                                      |    |

| Figure 11-8: TWI "Random Read" with Invalid Read Sequence                                     |    |

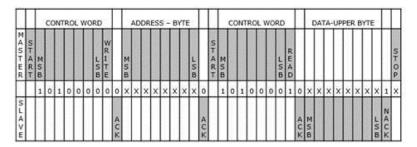

| Figure 11-9: TWI "Sequential Read" at Current Address                                         |    |

| Figure 11-10: TWI "Sequential Read" Starting with Random Read                                 |    |

| Figure 11-11: IC-TROSA State Machine                                                          |    |

| Figure 11-12: Power-Up Sequence                                                               |    |

| Figure 11-13: Power-Down Sequence                                                             |    |

| Figure 11-14: Tx Channel Change                                                               |    |

| Figure 11-15. Ty Wavelength Change Using High Resolution Tuning Registers                     | 82 |

#### OIF-IC-TROSA-01.0

### **List of Tables**

| Table 3-1: Power Supply Requirements                                     | 20  |

|--------------------------------------------------------------------------|-----|

| Table 4-1: High Speed Electrical Interface Common Features               | 21  |

| Table 4-2: Type-1 High Speed Electrical I/O Functional Map               | 23  |

| Table 5-1: Common Alarm & Control I/O Specification                      | 25  |

| Table 5-2: Alarm & Control I/O Electrical Requirements                   | 30  |

| Table 5-3: Alarm & Control I/O Timing Requirements                       | 31  |

| Table 6-1: Type-1 Low Speed I/O Contact Map                              | 33  |

| Table 6-2: Type-2 Low Speed Connector Specifications                     | 44  |

| Table 6-3: Type-2 Low Speed Electrical I/O Map <sup>1</sup>              | 46  |

| Table 7-1: Environmental & Operating Characteristics                     | 47  |

| Table 8-1: Laser Electro-Optic Characteristics (Type-2 only)             | 47  |

| Table 8-2: Transmitter Electro-Optic Characteristics                     | 48  |

| Table 8-3: Receiver Electro-Optic Characteristics                        | 49  |

| Table 9-1 Optical Fiber Interface Characteristics for Type-1 & Type-2    | 57  |

| Table 9-2: Type-1 Mechanical Dimensions                                  | 59  |

| Table 9-3: Type-2 Mechanical Dimensions                                  |     |

| Table 10-1: Type-1 Landing Pattern Dimensions                            | 65  |

| Table 10-2: Type-2 High Speed I/O Host Board Landing Pattern Dimensions  | 68  |

| Table 11-1: Two-Wire Electrical Characteristics [1]                      |     |

| Table 11-2: Two-Wire Interface Timing & RC Specifications <sup>[1]</sup> | 77  |

| Table 11-3: Behavior of FAWS TYPE in Different IC-TROSA States           | 83  |

| Table 11-4: IC-TROSA Register Map                                        | 85  |

| Table 14-1 Additional electro-optical characteristics (informative)      | 168 |

## **Document Revision History**

| Document          | Date            | Revisions/Comments       |

|-------------------|-----------------|--------------------------|

| OIF-IC-TROSA-01.0 | August 20, 2019 | Initial document release |

|                   |                 |                          |

|                   |                 |                          |

#### 1. Introduction

This document details an Implementation Agreement for an Integrated Coherent Transmit-Receive Optical Sub Assembly (IC-TROSA) targeting modulation and data-rate agnostic coherent applications having nominal symbol rates up to 64Gbaud. This IA aims to identify and specify the common features and properties of IC-TROSA to enable them to broadly meet the needs of current and future coherent systems.

The IC-TROSA Implementation Agreement defines the following: (1) Required functionality; (2) High speed electrical interfaces; (3) Low speed electrical interfaces; (4) Environmental and operating characteristics; (5) Electro-optical characteristics; (6) Mechanical requirements; (7) Management Interface. Additional informative electro-optical specifications are also included in Appendix B.

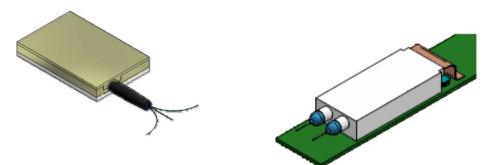

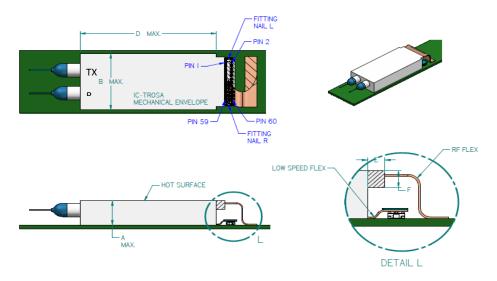

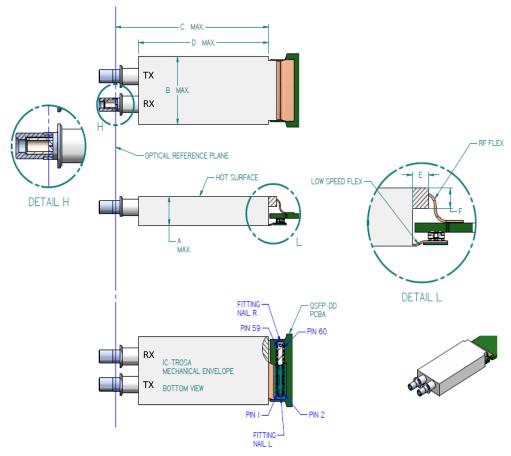

Two electro-mechanical form factors are defined within this IC-TROSA IA. Type-1 uses a surface mount (SMT) Ball Grid Array (BGA) configuration. The alternative electro-mechanical form factor Type-2 employs a mechanical enclosure utilizing separate flexible PCBs for low speed and RF I/O interfaces. Mechanical, electrical, and functional differences between the Type-1 and Type-2 form factors are highlighted where appropriate, otherwise common performance characteristics are required for the two form factors.

Figure 1-1: Type-1 IC-TROSA Figure 1-2: Type-2 IC-TROSA

The IA defines an IC-TROSA as a digitally controlled optical board mount module with integrated logic for purposes of optical configuration, stabilization, and monitoring. The IA further defines the management interface in terms of the communications hardware and management system software specifications. The IC-TROSA management interface specification is common to both Type-1 and Type-2 electro-mechanical form-factors with a few exceptions for laser control and some Alarm, Control, and I/Os as described within this IA.

The IA does not define the technologies used to implement the IA, nor the expected optical transmission performance of coherent systems using receivers conforming to the IA.

#### 2. Functionality

#### 2.1. Electro-Optic Architecture

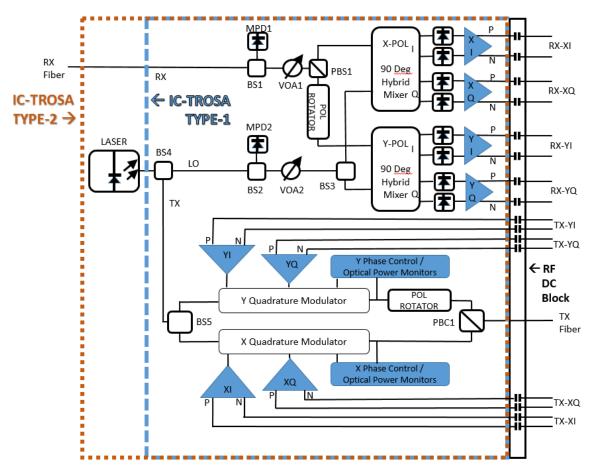

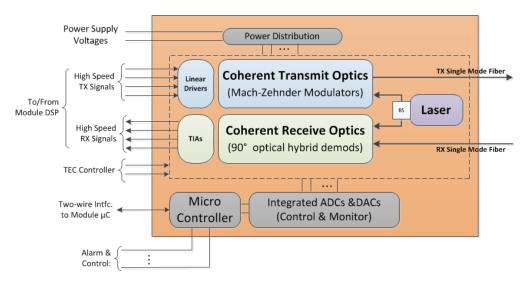

The required electro-optic functional blocks, as well as some optional functions, needed to implement a coherent transmitter, receiver, and laser (Type-2 only) are shown in Figure 2-1. An IC-TROSA that meets the objectives of the IA contains the functionality shown within the dashed line boxes in Figure 2-1 and the Control & Monitoring functionality as shown in Figure 2-3 or Figure 2-4 unless otherwise noted as optional.

An IC-TROSA shall provide at a minimum the following electro-optic functionality:

- A. A Receive (RX) signal input fiber that shall be Single Mode Fiber (SMF).

- B. Type-1 Package shall have a Laser Input fiber, split internally between Modulator and Local Oscillator (LO) functions. The Laser Input fiber shall be Polarization Maintaining Single Mode Fiber (PM-SMF).

- C. A Type-2 Package will not have a Laser Input fiber. The Laser function is integrated inside the Type-2 Package.

- D. A Transmit (TX) signal output fiber that shall be Single Mode Fiber (SMF)

- E. A polarization splitting element, separating the RX light into two orthogonal polarizations, with each polarization delivered to a 90 degree hybrid mixer.

- F. A polarization maintaining power splitter or polarization splitting element, splitting the local oscillator input power equally and delivering it to the two 90 degree hybrid mixers.

- G. Two (2) 90 degree hybrid mixers with differential optical outputs.

- H. Eight (8) photo-detectors comprised of 4 sets of differential detectors.

- I. Four (4) linear trans-impedance amplifiers providing differential RF output signals [RX-XI, RX-XQ, RX-YI, RX-YQ] from the receiver.

- J. A polarization maintaining power splitter or polarization splitting element, splitting the Laser input power equally and delivering it to the two pair of nested Mach-Zehnder modulators.

- K. Four (4) nested Mach-Zehnder modulators

- L. Four (4) linear high bandwidth modulator driver amplifiers with differential input signals [TX-XI, TX-XQ, TX-YI, TX-YQ] to the transmitter.

- M. An integrated control and Management Interface as described in Section 11.

- N. An IC-TROSA *may* also contain the following optical functionality:

- O. Optical power tap(s) and monitor photodiode(s) in the RX input path either before the polarization splitting element or in each path after the splitting element. This IA does not prohibit the use of additional taps and monitor photodiodes within the IC-TROSA for control, monitoring, or vendor specific functions.

- P. A variable optical attenuator in the Signal input path either before the polarization splitting element or in each path after the splitting element.

- Q. X (X-Pol) and Y (Y-Pol) indicate a pair of mutually orthogonal polarizations of any orientation, and I and Q are mutually orthogonal phase channels in each polarization. The IC-TROSA, therefore, has 4x polarization-phase differential RF input channels labeled as TX-XI, TX-XQ, TX-YI, TX-YQ for the transmitter and 4x polarization-phase differential RF output channels labeled as RX-XI, RX-XQ, RX-YI, RX-YQ from the receiver.

Figure 2-1: IC-TROSA Electro-Optic Functional Reference Diagram Including Optional Components

#### Notes:

- 1. DC blocking capacitors for high speed TX and RX data lines are optionally located inside or outside the package.

- 2. IC-TROSA Type-1 does not have an integrated Laser source.

- 3. VOAs and MPDs represent general power control functions with optional locations. Other VOA and MPD locations as well as additional VOAs and MPDs are acceptable.

- 4. The area enclosed by the long dashed lines indicate the Type-1 Package functionality.

- 5. The area enclosed by the short dashed lines indicate the Type-2 Package functionality.

- 6. The area enclosed by the solid lines indicate the DC blocking capacitors.

- 7. The SOAs in the TX path are optional.

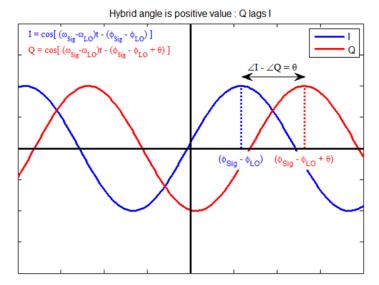

Figure 2-2: Coherent Detection I-Q Phase Relationship

The phase relationship between I and Q outputs is established by the heterodyne technique with the frequency of the Signal input to the receiver greater than the frequency of the LO input. Under this condition, when the I and Q output waveforms are observed in the time domain, the Q channel lags the I Channel by nominally +90 degrees, as shown in Figure 2-2.

Channel outputs 'p' and 'n' are the complementary outputs for each polarization-phase channel and are defined such that the output voltage for 'p' increases as the RX and Local Oscillator approach the in-phase condition to form constructive interference, and the output voltage for 'n' decreases under the same conditions.

The TIAs in the receiver function enable multiple signal monitors and control methods. The most notable TIA control selection is between automatic or manual gain control operating mode (AGC or MGC). TIAs can support: AGC only, MGC only, or both. All are valid implementations. The TIAs may also facilitate a bandwidth equalization function and provide various input signal strength and/or output level monitors (PI). In the AGC operating mode there is a RF output level adjust control (Output Adjust, OA) available and in the MGC operating mode an external signal (Gain Adjust, GA) is used to control the gain of each differential amplifier.

The IC-TROSA also comprises a modulation function employing a Polarization Multiplexed-Quadrature Modulator or PM-Q Modulator at the transmitter. Each quadrature modulator typically comprises of two inner nested Mach-Zehnder modulators with bias control, a 90° phase shifter in the outer modulator with phase control, and an output power monitoring output. Any implementation or technology choices may be used to realize this basic functionality. This modulator function also includes linear RF driver

amplifiers for each of the four modulator stages TX-XI, TX-XQ, TX-YI, TX-YQ as shown in Figure 2-1.

The optical power from a narrow line width laser source is divided into two parts with a beam splitter (BS) and each part is independently modulated by a quadrature modulator. The Y modulator output has its polarization rotated 90° by the polarization rotator creating a polarization state orthogonal to the X modulator. The resulting X and Y modulated signals are then combined with a polarization beam combiner and output through an optical output ("TX") fiber. The power in each of the two polarizations is independently monitored with photodiodes.

As indicated in Figure 2-1, the PM-Q Modulator function includes the following basic components:

- a) One optical Laser Input fiber (internal laser in the case of Type-2 package)

- b) One optical power splitter

- c) Four linear modulator driver amplifiers

- d) Two independent quadrature modulators

- e) Two independent monitoring photodiodes

- f) One polarization multiplexer including polarization rotator and combiner

- g) One optical Transmit "TX" output

The following interfaces are specified for the PM-Q modulator function:

- a) One optical Transmit fiber (TX)

- b) Four high-speed data interfaces

- c) Four modulator bias control interfaces

- d) Two phase control interfaces

- e) Two power monitoring interfaces

The two polarized signal components in the output are referred to as "X" and "Y", and the quadrature modulators that encode information onto the polarization components are correspondingly referred to as X and Y modulators. Each quadrature modulator is driven by an "I" and a "Q" data signal. The four high-speed data interfaces are referred to as TX-XI, TX-XQ, TX-YI and TX-YQ.

Each of the four data modulators needs to be biased with a suitable DC voltage. This IA specifies biasing as being an IC-TROSA internal design function supporting both single-ended as well as push-pull biasing. No external bias contacts are provided. The I and Q phase offset is controlled via vendor proprietary internal control algorithms executed and monitored by the IC-TROSA micro controller. External phase control pins are not provided. The phase offset between I and Q in X and Y arms is controlled by phase control interfaces X Phase and Y Phase respectively.

I and Q are established by the heterodyne technique, with the frequency of the RX input to the receiver greater than the frequency of the LO input. The I and Q channel outputs are measured in the time domain.

Under these conditions the RX Q channel phase lags by nominally +90 degrees the RX I channel phase, as shown in Figure 2-2.

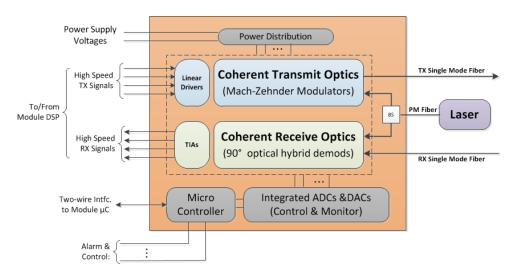

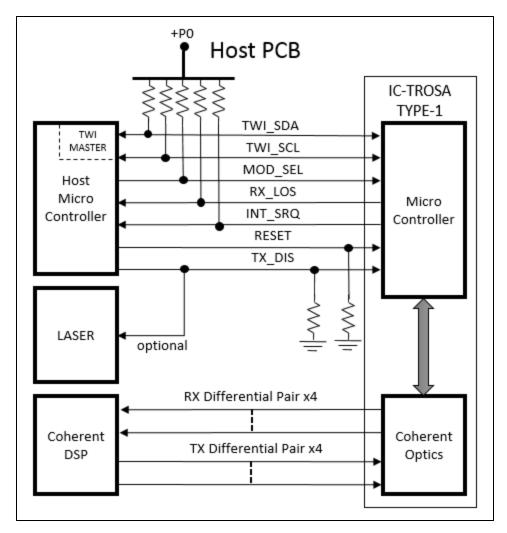

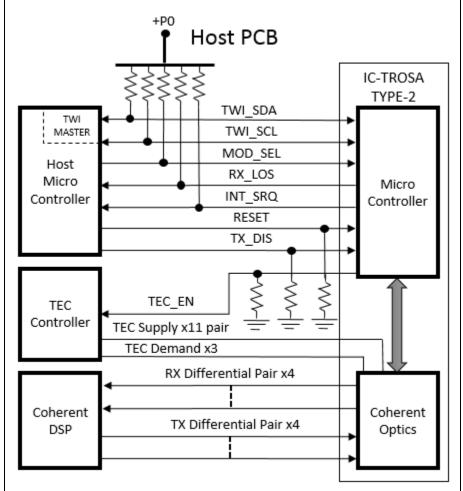

#### 2.2. Control and Monitoring Architecture

The control and monitoring functional blocks required to implement a Type-1 IC-TROSA are shown in Figure 2-3. The Type-2 configuration with integrated laser is shown in Figure 2-4. The primary interfaces are: power supplies, digital communications interface, dedicated alarm & control I/Os, high speed RF contacts for TX and RX I/Q data, and in case of Type-1 package an optical fiber interface to the laser. An IC-TROSA that meets the objectives of the IA contains the functionality shown within these two figures. The Type-2 IC-TROSA typically requires the use of one or more Thermo-Electric Coolers (TECs) inside the IC-TROSA package. In this case, the Type-2 requires one or more external TEC controller ICs located on the host PCB with several TEC power I/Os mating the TEC controller with the IC-TROSA. The IC-TROSA Alarm & Control I/Os provide a TEC\_EN function which may be used by the IC-TROSA's micro controller to enable or disable the external TEC Controllers. The I/Os required for TEC control are listed and described in detail in the Low Speed Electrical I/O and the Dedicated Alarm & Control I/O sections of this document.

Figure 2-3: Type-1 Control & Monitoring Functional Diagram

Figure 2-4: Type-2 Control & Monitoring Functional Diagram

#### 3. Power Supply Architecture

#### 3.1. Overview

Power supplies for the IC-TROSA are all located external to the IC-TROSA package and are described in

Table 3-1. Proper Initialization and Reset of an IC-TROSA requires the host board or module to have on/off control over all the IC-TROSA primary and secondary power supplies. By definition the IC-TROSA does not have the capability of enabling/disabling its own power supplies. Device initialization is described below.

The primary power supply (P0) is a nominal +3.3V DC supply. This primary supply is the first to be activated on the IC-TROSA for the purpose of initializing the IC-TROSA's internal micro controller, alarm and control logic, and management interface. IC-TROSA's highly integrated structure requires multiple vendor specific voltage levels. To achieve a multi-vendor implementation agreement, the IC-TROSA IA specifies a number of vendor defined power supplies. An implementation of IC-TROSA does not require the use of all these supplies. However, to ensure a host PCB is 100% compatible with all possible vendor implementations it may be required for the host PCB to have all supplies available. In addition to the single "Primary" power supply P0 the IC-TROSA requires multiple vendor defined "Secondary" power supplies (P1, P2, P3, P4, P5, and P6). Upon device start-up, the external host controller has the responsibility for querying the IC-TROSA, through the management interface, for the proper setting and sequencing of each secondary supply. The I/O mapping of all IC-TROSA power supplies are listed within the Low Speed Electrical Interface section of this document.

#### 3.2. Primary Supply (P0)

The primary power supply P0 is a nominal +3.3V DC "Narrow Range" supply as defined by JEDEC specification JESD8C.01 revision September 2007. This supply is the first to be activated on the IC-TROSA for the purpose of initializing the IC-TROSA's internal logic controller and management interface into the Low Power Mode.

#### 3.3. Secondary Supplies (P1, P2, P3, P4, P5, P6)

The several secondary supplies offer both positive and negative DC voltage ranges. The power supply turn-up sequencing is an important feature of the IC-TROSA to avoid potential damage to internal components. Vendor specific voltage level and sequencing information for the secondary supplies are contained within the C000h area of the management interface register map. Upon device start-up, after primary supply has been activated and stabilized, the host module micro controller has the responsibility of querying the IC-TROSA for secondary power supply information and applying to the IC-TROSA package the correct nominal voltage values and sequencing for each secondary supply. Therefore, vendors should avoid ganging the P0 primary supply contacts for high power functions such as TX and RX. Achieving low power mode requires secondary power supplies to be disabled without disabling P0 primary supply.

The "Voltage Range" in Table 3-1 are the specified ranges for the nominal voltages required to meet the intent of this IA. For Secondary supply specifications the IC-TROSA vendor shall provide the customer with a min, nominal, and max specification for each supply setting. A vendor seeking to be compliant with this IA is not required to use secondary supplies, but they are required to adhere to the allowable voltage ranges when they are utilized. Otherwise ganging of secondary supplies with other secondary supplies having same nominal voltage set points is allowed within this IA. However, to allow end users of an IC-TROSA to have a multi-vendor capability on the host design, the vendor should not require ganging of secondary power supplies on the host side. Secondary power supply ganging shall be achieved internal to the IC-TROSA.

| Package<br>Style | Style Specified Nominal |                  |      | age Rang | 1    |

|------------------|-------------------------|------------------|------|----------|------|

|                  |                         | Voltage<br>Range | Min  | Nom      | Max  |

|                  | P0+                     | +3.3 [2]         | 3.15 | 3.3      | 3.45 |

|                  | P1+                     | 0 to +12         | VS   | VS       | VS   |

|                  | P2-                     | 0 to -12         | VS   | VS       | VS   |

| Type-1           | P3+                     | 0 to +12         | VS   | VS       | S VS |

|                  | P4-                     | 0 to -12         | VS   | VS       | VS   |

|                  | P5+                     | 0 to +12         | VS   | VS       | VS   |

|                  | P6+                     | 0 to +12         | VS   | VS       | VS   |

|                  | P0+                     | +3.3             | 3.15 | 3.3      | 3.45 |

|                  | P1+                     | 0 to +12         | VS   | VS       | VS   |

|                  | P2-                     | 0 to -12         | VS   | VS       | VS   |

| Type-2           | P3+                     | 0 to +12         | VS   | VS       | VS   |

|                  | P4-                     | 0 to -12         | VS   | VS       | VS   |

|                  | P5+                     | 0 to +18         | VS   | VS       | VS   |

|                  | P6+                     | 0 to +12         | VS   | VS       | VS   |

**Table 3-1: Power Supply Requirements**

#### Notes:

- 1. VS = Vendor Specified voltage requirements

- 2. JEDEC "Narrow Range" specification JESD8C.01 revision September 2007

#### 3.4. Low Power Mode

IC-TROSA Low Power Mode is specifically defined as having only the Primary 3.3V supply (P0) enabled. The host application shall determine if the IC-TROSA low power state is sufficiently low power by reading register "Maximum Power Consumption in Low Power Mode" 801Eh. "Low Power Mode" is the default steady state for IC-TROSA after the "Initialize" transient state. Refer to the IC-TROSA State Machine as shown in Figure 11-11. Should the Low Power Mode not provide sufficiently low power for the host application, the host may completely power down IC-TROSA by disabling all primary and secondary supplies according to the vendor specified power down sequence. For details on initiating Low Power Mode from a high power state refer to Section 11.7 and command sequencing in Figure 11-13.

#### 4. High Speed Electrical Interface

#### 4.1. Common Features

The basic structure of the high speed interface is the same for both IC-TROSA package styles. Only the package contact styles differ. The common features are shown in Table 4-1.

Table 4-1: High Speed Electrical Interface Common Features

| Parameter             | Value                   | Notes                          |

|-----------------------|-------------------------|--------------------------------|

| Interface type        | Differential            |                                |

| Channel number        | 4 x TX                  | 26 total RF I/Os               |

| Chainlei number       | 4 x RX                  | including GNDs                 |

| Channel configuration | G-S-S-G                 |                                |

|                       |                         | DC blocking capacitor          |

|                       |                         | locations are vendor specific  |

| RF Coupling           | AC coupling             | and may be located internal or |

|                       |                         | external to the IC-TROSA       |

|                       |                         | package.                       |

| Line impedance        | 100 Ohm Differential    | Includes flex PCB for          |

| Line impedance        | 100 Ollili billerentiai | Type-2 packages                |

|                       | TX-XI                   |                                |

|                       | TX-XQ                   |                                |

|                       | TX-YI                   |                                |

|                       | TX-YQ                   |                                |

| Channel pin-out       |                         |                                |

|                       | RX-XI                   |                                |

|                       | RX-XQ                   |                                |

|                       | RX-YI                   |                                |

|                       | RX-YQ                   |                                |

| Differential pin-out  | Signal                  | Р                              |

| Differential pin-out  | Complimentary Signal    | N                              |

#### 4.2. Allowable RF Channel Mappings

IC-TROSA carries forward several optional RF channel mappings as defined in OIF-CFP2-ACO-01.0. All RF mappings shown in this IC-TROSA IA may be altered to adopt any of the allowable mappings in Figure 4-1.

| Mapping | X:Y | I,Q     | p/n             | Notes                             |

|---------|-----|---------|-----------------|-----------------------------------|

| [0,x,x] | X:Y |         |                 | Pol. <i>cannot</i> be interleaved |

| [1,x,x] | Y:X |         |                 |                                   |

| [x,0,x] |     | I,Q:I,Q |                 | Same across Pol.                  |

| [x,1,x] |     | Q,I:Q,I |                 |                                   |

| [x,2,x] |     | I,Q:Q,I |                 | Flip across Pol.                  |

| [x,3,x] |     | Q,l:I,Q |                 |                                   |

| [x,x,0] |     |         | p/n,p/n:p/n,p/n | Same across Pol. and I,Q          |

| [x,x,1] |     |         | n/p,n/p:n/p,n/p |                                   |

| [x,x,2] |     |         | p/n,p/n:n/p,n/p | Flip across Pol.                  |

| [x,x,3] |     |         | n/p,n/p:p/n,p/n |                                   |

| [x,x,4] |     |         | p/n,n/p:p/n,n/p | Flip across I,Q                   |

| [x,x,5] |     |         | n/p,p/n:n/p,p/n |                                   |

| [x,x,6] |     |         | p/n,n/p:n/p,p/n | Flip across Pol. and I,Q          |

| [x,x,7] |     |         | n/p,p/n:p/n,n/p |                                   |

Figure 4-1: TX and RX RF Channel Mappings on the Electrical Interface

Note: For more detailed description of Channel Mapping table refer to OIF-CFP2-ACO-01.0.

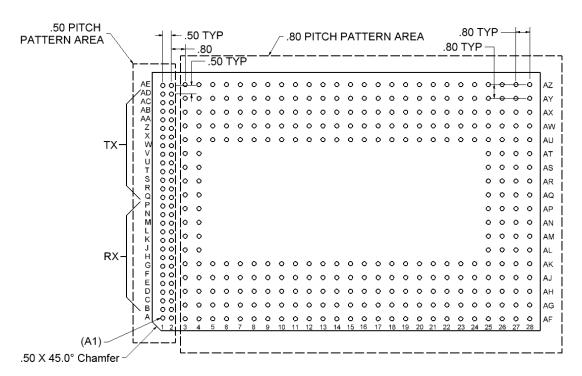

#### 4.3. High Speed Electrical Interface for Type-1 Form Factor

The high speed TX and RX electrical interfaces for a Type-1 IC-TROSA form-factor utilizes a 2D surface mount ball grid array in a G-S-S-G arrangement as shown in Figure 4-2. To reduce high speed channel skew between IC-TROSA and most common coherent DSP ball maps the TX and RX contacts are grouped in a single outer row. These high speed contacts are grouped by function and separated from the low speed contacts by a column of ground contacts to improve signal integrity. In order to keep IC-TROSA in the smallest possible form factor, the required RF DC decoupling capacitors for each of the high speed differential TX and RX data contacts are located outside the IC-TROSA on the host PCB for Type-1.

Figure 4-2: Type-1 Electrical Contact Map. Bottom View

| RX Contacts |            | Т    | X Contacts | Isolat | ion Grounds |

|-------------|------------|------|------------|--------|-------------|

| Ball        | Function   | Ball | Function   | Ball   | Function    |

| A1          | No Contact | Q1   | GND        | A2     | No Contact  |

| B1          | GND        | R1   | TX-YQn     | B2     | GND         |

| C1          | RX-YQn     | S1   | TX-YQp     | C2     | GND         |

| D1          | RX-YQp     | T1   | GND        | D2     | GND         |

| E1          | GND        | U1   | TX-YIn     | E2     | GND         |

| F1          | RX-YIn     | V1   | TX-YIp     | F2     | GND         |

| G1          | RX-YIp     | W1   | GND        | G2     | GND         |

| H1          | GND        | X1   | TX-XQn     | H2     | GND         |

| J1          | RX-XQn     | Z1   | TX-XQp     | J2     | GND         |

| K1          | RX-XQp     | AA1  | GND        | K2     | GND         |

| L1          | GND        | AB1  | TX-XIn     | L2     | GND         |

| M1          | RX-XIn     | AC1  | TX-XIp     | M2     | GND         |

| N1          | RX-XIp     | AD1  | GND        | N2     | GND         |

| P1          | GND        | AE1  | No Contact | P2     | GND         |

|             |            |      |            | Q2     | GND         |

|             |            |      |            | R2     | GND         |

|             |            |      |            | S2     | GND         |

|             |            |      |            | T2     | GND         |

|             |            |      |            | U2     | GND         |

|             |            |      |            | V2     | GND         |

|             |            |      |            | W2     | GND         |

|             |            |      |            | X2     | GND         |

|             |            |      |            | Z2     | GND         |

|             |            |      |            | AA2    | GND         |

|             |            |      |            | AB2    | GND         |

|             |            |      |            | AC2    | GND         |

|             |            |      |            | AD2    | GND         |

|             |            |      |            | AE2    | No Contact  |

Table 4-2: Type-1 High Speed Electrical I/O Functional Map

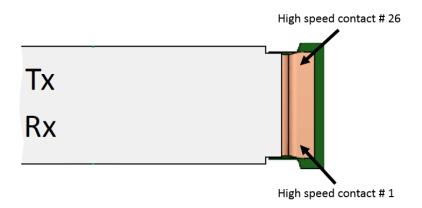

#### 4.4. High Speed Electrical Interface for Type-2 Mechanical Form Factor

The high speed electrical interface for the Type 2 form factor is realized using RF flexible PCB interfaces attached to the short side of the package body as shown in Figure 4-3 below. The opposite end of the RF flexible PCB interfaces are then used to connect the high speed signal lines to the host board. The flexible PCBs allow for a customized RF connection between a vendor-specific interface on the IC-TROSA package and a customer-specific interface on the host PCB.

Figure 4-3: Type-2 High Speed Flex Interface Top View

| RX           | Contacts | 1        | X Contacts |

|--------------|----------|----------|------------|

| Contact<br># | Function | Contact# | Function   |

| 1            | GND      | 14       | GND        |

| 2            | RX-YQn   | 15       | TX-YQn     |

| 3            | RX-YQp   | 16       | TX-YQp     |

| 4            | GND      | 17       | GND        |

| 5            | RX-YIn   | 18       | TX-YIn     |

| 6            | RX-YIp   | 19       | TX-YIp     |

| 7            | GND      | 20       | GND        |

| 8            | RX-XQn   | 21       | TX-XQn     |

| 9            | RX-XQp   | 22       | TX-XQp     |

| 10           | GND      | 23       | GND        |

| 11           | RX-XIn   | 24       | TX-XIn     |

| 12           | RX-XIp   | 25       | TX-XIp     |

| 13           | GND      | 26       | GND        |

Table 4-7: Type-2 High Speed Electrical I/O Map

#### 5. Dedicated Alarm & Control I/Os

#### 5.1. Common Alarm & Control I/Os

A few dedicated hardware I/Os are allocated to critical functions and are applicable to both Type-1 and Type-2 packages. These critical functions require dedicated hardware I/O due to their reliance on fast response time or fail-safe requirements. Fail-safe are those I/Os which bypass the control firmware and directly initiate certain hardware functions. The Common Alarm & Control I/Os for both Type-1 and Type-2 IC-TROSA are shown in Table 5-1. Logic levels and timing requirements for two-wire interface lines TWI SDA and TWI SCL are specified in section 11 of this IA.

Table 5-1: Common Alarm & Control I/O Specification

| Function                 | Type <sup>1</sup>  | Description                                                   | Applicable IC-<br>TROSA Form<br>Factor | Assertive<br>(Active)<br>Level |

|--------------------------|--------------------|---------------------------------------------------------------|----------------------------------------|--------------------------------|

| TWI_SDA                  | Bi-<br>directional | Two-wire Serial<br>Data                                       | Type 1 & 2                             |                                |

| TWI_SCL                  | Bi-<br>directional | Two-wire Serial<br>Clock from bus<br>Master                   | Type 1 & 2                             |                                |

| TEC_EN                   | Output             | Thermo-Electric<br>Cooler Enable                              | Type-2                                 | High                           |

| TECn_DMD<br>(TEC_DEMAND) | Analog<br>Output   | Thermo-Electric<br>Cooler current<br>demand control<br>signal | Type-2                                 | Analog                         |

| RESET                    | Input              | Reset controller                                              | Type 1 & 2                             | Low                            |

| TX_DIS                   | Input              | Transmit Disable                                              | Type-1 & 2                             | Low                            |

| RX_LOS                   | Output             | Receive Loss of<br>Signal                                     | Type 1 & 2                             | Low                            |

| INT_SRQ                  | Output             | Interrupt/Service<br>Request                                  | Type 1 & 2                             | Low                            |

| MOD_SEL                  | Input              | Module Select                                                 | Type 1 & 2                             | Low                            |

#### Note:

1. Input/output designations are from IC-TROSA perspective.

#### 5.2. Type-1 Alarm & Control I/O Configuration

Figure 5-1: Type-1 Alarm & Control I/O Hardware Configuration

## 5.3. Type-2 Alarm & Control I/O Configuration

Figure 5-2: Type-2 Alarm & Control I/O Hardware Configuration

#### 5.4. Alarm & Control Detailed Descriptions

#### 5.4.1. TEC EN (Thermo-Electric Cooler Enable)

TEC\_EN is an active high output control signal used only for a Type-2 IC-TROSA. It functions as an enable/disable control signal to one or more thermo-electric cooler controllers located external to the IC-TROSA. A high level on the TEC\_EN I/O will enable the TEC controller. A logical low on this I/O will disable the TEC controller and shut off all current to the IC-TROSA internal TECs. This control signal may be used to create a low power mode. The TEC\_EN I/O has a pull-down resistor to electrical ground. Upon start-up and/or RESET conditions, and prior to the IC-TROSA internal controller being fully ready, the IC-TROSA TEC\_EN I/O is held in a low state disabling all TEC controllers.

#### 5.4.2. RESET

RESET is an active low input control to the IC\_TROSA. It applies to both Type-1 and Type-2 package designs. The RESET I/O is used to reset the IC-TROSA internal logic controller and management interface. It is, in effect, a processor or controller reset only. RESET has a pull-down resistor to ground. Upon host module power-up, RESET effectively holds the IC-TROSA in RESET mode until the host controller sets RESET high enabling the IC-TROSA internal controller. After a RESET the IC-TROSA controller returns all IC-TROSA settings to the default state. Holding RESET low prevents the internal controller from performing its boot-up sequence. Reset events are recorded in "Initialize State Latch" B022h.0

#### 5.4.3. TECn DMD (Thermo-Electric Cooler Demand)

The TECn\_DMD I/O is an output from the IC-TROSA. It is intended to drive a power amplifier which supplies current back to the TEC in a closed loop temperature control scheme. The loop function and loop bandwidth control is most likely provided by the microprocessor in the IC-TROSA in the form of a PID (Proportional-Integral-Derivative) controller. Up to n=three TECn DMD terminals are provided for IC-TROSA applications requiring multiple temperature controlled zones.

The TEC DMD output has a voltage range from 0V to 2.5V full scale. It is intended to drive a high impedance (>5k ohms) input so that no further circuits are required to interface it to the control input of the power amplifier. The maximum current drawn from the TEC demand pin should be <5mA end-of-life, over temperature (EOLOT). The TEC Demand output is configured such that 0V represents maximum cooling of the TEC top plate. Then 2.5V represents maximum heating. The balance point, no heating or cooling, is set at 1.25V midrange. Using these voltages the circuits can be configured using readily available DAC and voltage reference circuits. The TEC DMD output signal should be monotonic with increasing input signal.

The TEC power amplifier is placed remotely to the IC-TROSA to avoid problems associated with noise in the case of a switching design or heatsinking in the case of a linear design. It should accept the TEC demand signal on a high impedance input pin and produce a proportional output suitable to drive the TEC. The TEC power amplifier may be a discrete circuit implementation or an integrated (e.g. components encapsulated in a sub-package) solution. In order to realize a practical circuit implementation the power amplifier may limit the maximum cool condition to a voltage slightly above OV (example: 100mV) to avoid any problems associated with noise. TEC power amplifier may be a noise source for the lasers. At present the TEC power amplifier noise requirement is not specified and is vendor dependent and the host shall provide a variable power supply that is as clean as possible.

#### 5.4.4. TX DIS (Transmit Disable)

TX\_DIS is an active low control I/O used to disable light transmission from the IC-TROSA TX port. TX\_DIS has a pull-down resistor to ground. During IC-TROSA power-up and RESET this TX\_DIS is held low effectively shutting down TX transmissions from the IC-TROSA TX port. TX\_DIS is an input I/O on both Type-1 and Type-2 packages. For Type-1 IC-TROSA it is optional to have the IC-TROSA control optical output power to the IC-TROSA TX port. In this case, the TX\_DIS line is not required to be tied to the Laser's TX\_DIS input, but the host must power up IC-TROSA before power-up & power-down of the laser. For a Type-2 IC-TROSA containing an integrated Laser, this I/O is an active low input control I/O from the host controller. A low state on the TX\_DIS line will disable transmissions through TX output port.

#### 5.4.5. RX LOS (Receive Loss of Signal)

RX\_LOS is an active low output I/O on both Type-1 and Type-2 IC-TROSA. RX\_LOS indicates a receiver loss of signal condition as defined by a user defined minimum receive power level stored in the management interface settings. RX\_LOS is pulled high to P0 primary supply by a pull-up resistor. A low level on RX\_LOS indicates the input receive signal is below the user defined threshold.

#### 5.4.6. INT SRQ (Interrupt / Service Request)

INT\_SRQ is an active low output I/O for both Type-1 and Type-2 IC-TROSA. INT\_SRQ is used by the IC-TROSA to indicate a fault or alarm condition to the host controller. A high level on INT\_SRQ indicates no alarm or fault present. A low level indicates the presence of a fault or alarm condition requiring the host to query the IC-TROSA management interface alarm registers to determine the source(s) of the status request. INT\_SRQ is pulled high by a pull-up resistor to PO primary power supply.

#### 5.4.7. MOD SEL (Module Select)

MOD\_SEL is an active low input control I/O to both Type-1 and Type-2 IC-TROSA. MOD\_SEL serves as a module select control to be used in conjunction with the Two-wire interface. MOD\_SEL allows multiple IC-TROSA modules to co-exist on a single two-wire interface bus under the control of a single host controller. MOD\_SEL has a pull-up resistor to the P0 primary power supply disabling two-wire communication responses from IC-TROSA until its internal controller has indicated a "Ready" status by setting INT\_SRQ low to indicate IC-TROSA has completed a power reset. With MOD\_SEL held high the IC-TROSA shall not respond to or acknowledge any Two-wire communications from the host controller. Also, MOD\_SEL shall not change during any Two-wire interface transaction.

#### 5.4.8. Implementing Monitor Tick Source in IC-TROSA

IC-TROSA does not have a dedicated hardware I/O for capturing PM Tick Source (Performance Monitor Tick Source) signals as described in CFP MSA Hardware Specification Revision 1.4. However, IC-TROSA does support CFP-MSA-Management Interface Specification 2.6 r06a registers used for Tick Source

configuration, timing, and latching and in addition it provides an "External Soft PM Interval Sync" bit within register CO2Eh bit 15 which can be asserted by the external application host controller through the IC-TROSA TWI. Additionally, a Vendor Specific hardware I/O may optionally be mapped to the "External Soft PM Interval Sync" bit in order to provide a PM Tick Source hardware input. This I/O mapping is an optional feature and the implementation is vendor specific. Mapping of Vendor Specific I/Os are located in the Vendor Specific area of the IC-TROSA register map.

#### 5.5. Alarm & Control I/O Electrical Requirements

Table 5-2: Alarm & Control I/O Electrical Requirements

| Function  | Logic    | Sym  | Vmin <sup>1</sup>         | Vmax <sup>1</sup>         | Condition                               |

|-----------|----------|------|---------------------------|---------------------------|-----------------------------------------|

| TECn_DMD  | Analog   |      | 0V                        | +2.5V                     | +1.25V is zero current demand reference |

|           |          |      |                           |                           | voltage                                 |

| TEC EN    | LVCMOS   |      |                           |                           | 4.7k-10k $\Omega$ Pull-down             |

|           |          |      |                           |                           | to GND                                  |

| RESET     | LVCMOS   |      |                           |                           | 4.7k-10k $\Omega$ Pull-down             |

| KESET     | LVCIVIOS | \/OI |                           | .0.21/                    | to GND                                  |

| TX DIS    | LVCMOS   | VOL  |                           | +0.2V                     | 4.7k-10k $\Omega$ Pull-down             |

| 17_013    | LVCIVIOS | VOH  | <sup>[2]</sup> P0min-0.2V |                           | to GND                                  |

| RX LOS    | LVCMOS   | VOH  | * POIIIII-0.2V            |                           | 4.7k-10k $\Omega$ Pull-up to            |

| KX_LO3    | LVCIVIOS | VIL  | -0.3V                     | +0.8V                     | +P0                                     |

| INT SRQ   | LVCMOS   | VIL  | -0.5 V                    | +0.6V                     | 4.7k-10k $\Omega$ Pull-up to            |

| IIVI_SKQ  | LVCIVIOS | VIH  | +2V                       | <sup>[2]</sup> P0max+0.3V | +P0                                     |

| MOD SEL   | LVCMOS   | **** | . = •                     | . 5                       | 4.7k-10k $\Omega$ Pull-up to            |

| IVIOD_SEL | LVCIVIOS |      |                           |                           | +P0                                     |

#### Notes:

- +3.3V LVCMOS logic levels from JEDEC specification JESD8C.01 revision September 2007

- 2. P0 is a reference to the IC-TROSA P0+ Power Supply used for all logic functions and communications.

#### 5.6. Alarm & Control I/O Timing Requirements

Table 5-3: Alarm & Control I/O Timing Requirements

| Function      | Symbol                                                                       | Min | Max           | Units      | Conditions                                 |

|---------------|------------------------------------------------------------------------------|-----|---------------|------------|--------------------------------------------|

| TWI_SDA       | See section 11 for TWI timing requirements                                   |     |               |            |                                            |

| TWI_SCL       |                                                                              | 9   | See section 1 | .1 for TWI | timing requirements                        |

| TEC EN Assert |                                                                              |     | 100           | ms         | Time from TEC_EN control bit assert to     |

| TEC_EN ASSERT |                                                                              |     |               |            | TEC_EN pin asserted                        |

| TEC_EN        |                                                                              |     | 100           | ms         | Time from TEC_EN control bit de-assert to  |

| De-assert     |                                                                              |     |               |            | TEC_EN pin de-assert                       |

| RESET         |                                                                              |     | 2.5           | sec        | Module Initialization time from RESET      |

| Assert        |                                                                              |     |               |            |                                            |

| RESET         |                                                                              |     |               |            | Not specified                              |

| De-assert     |                                                                              |     |               |            |                                            |

| TX_DIS        |                                                                              |     | 100           | μs         | Application specific                       |

| Assert        |                                                                              |     |               |            |                                            |

| TX_DIS        |                                                                              |     | 20            | ms         | Time from Tx Disable pin De-asserted until |

| De-assert     |                                                                              |     |               |            | IC-TROSA enters the Tx-Turn-on State       |

| RX_LOS        |                                                                              |     | 150           | ms         | Time from hardware RX_LOS pin asserted     |

| Assert        |                                                                              |     |               |            | to RX_LOS Pin State asserted.              |

| RX_LOS        |                                                                              |     | 150           | ms         | Time from hardware RX_LOS pin de-          |

| De-Assert     |                                                                              |     |               |            | asserted to RX_LOS Pin State de-asserted.  |

| INT_SRQ       |                                                                              |     | 150           | ms         | Time from any condition of FAWS            |

| Assert        |                                                                              |     |               |            | alarm/status state to INT_SRQ asserted.    |

| INT_SRQ       |                                                                              |     | 150           | ms         | Time from last FAWS condition cleared to   |

| De-assert     |                                                                              |     |               |            | INT_SRQ de-asserted.                       |

| MOD_SEL       | See Table 11-2 for MOD_SEL timing requirements related to operation with TWI |     |               |            |                                            |

#### 6. Low Speed Electrical Interface

#### 6.1. Low Speed Electrical Interface for Type-1 Form Factor

The low speed electrical connections for the Type-1 form factor are located on the bottom side of the package and form part of the 2D array of contacts as already shown in Figure 4-2. Note that for solder reflow mounting method the unused contacts on the interface are required to be present. Removing unused contacts may cause an imbalance in the package during the mounting process resulting in poor contact or misalignment. When using the solderless mechanical mounting method it is recommended to remove all unnecessary and unused contacts between the Type-1 IC-TROSA and the electrical interposer as the required compression force is directly proportional to the number of contacts.

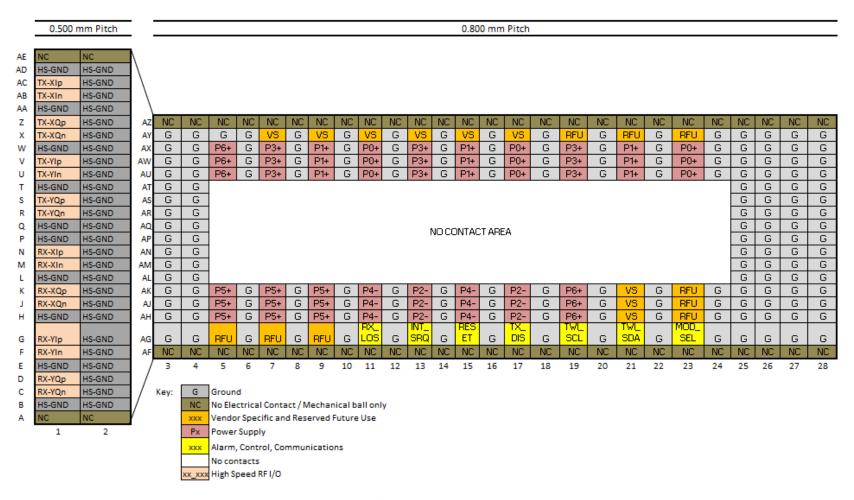

The electrical interface functionality is shown pictorially as a 2D ball map in Figure 6-1 and specified in Table 6-1.

Figure 6-1: Type-1 I/O Contact Map (Package Bottom View)

Table 6-1: Type-1 Low Speed I/O Contact Map

| Item # Contact Symbol Description |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                   | _                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                   |                                                                                                                             | Mech. contact/ no connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 1                                 |                                                                                                                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                   |                                                                                                                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1                                 | GND                                                                                                                         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                   | GND                                                                                                                         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1                                 |                                                                                                                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                   |                                                                                                                             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| AX3                               | GND                                                                                                                         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |