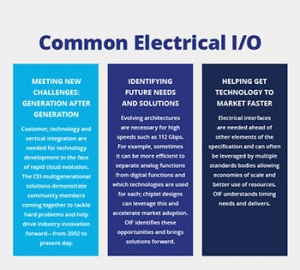

OIF has led the industry for the past 25 years in the development and publication of next generation electrical definitions for transmitters, receivers and channels to enable interoperable electrical links for chip to chip, chip to optical, line card to line card and equipment to equipment applications.

OIF recently published 112Gbps specifications for die to die, chip to chip, chip to module, medium reach chip to chip and long reach chip to chip also known as backplane.

Click here for CEI-224G project information.

Common Electrical I/O – 112G-Linear Project

A linear Chip-to-Optical Engine interface is needed to enable low power, low cost, small form factor 112G serial optical modules in Co-Packaged Optics, Near Package Optics (NPO) and server/GPU applications. This new project will facilitate increased bandwidth and reduced power of switch ports using co-packaged and closely packaged optical modules.

Demos

- 2022 PLL Interoperability Demo at OFC

- 2019 PLL Interoperability Demo at OFC

- 2018 PLL Interoperability Dem

Press Releases

- September 5, 2024 – OIF Leads the Charge for Interoperability at ECOC 2024

- August 7, 2024 – OIF Champions Interoperability at ECOC 2024: 34 Member Companies to Showcase Solutions for Data Centers, AI/ML Technologies and Disaggregated Systems

- June 13, 2024 – OIF Q2 Technical and MA&E Committees Meeting Wraps with CEI-224G-Linear Project Launch, New CMIS White Papers and Requirements for Energy Efficient Interfaces

- March 6, 2024 – OIF to Take Center Stage at OFC 2024 with Groundbreaking Multi-Vendor Interoperability Demonstrations and Expert Panels

- February 7, 2024 – OIF to Showcase Interoperability at OFC 2024 with Nearly 50 Member Companies Collaborating to Address Unprecedented Demand for Next-Generation Network Solutions

- January 10, 2024 – OIF Experts to Provide Technology Updates on Power Consumption in Next Generation Optical AI Networking, Common Electrical I/O (CEI) Trends at DesignCon 2024

- September 20, 2023 – OIF Showcases Multi-vendor Interoperability at ECOC 2023: Demo Features Nearly 40 Companies Demonstrating Innovation Across 400ZR+, Co-Packaging, CEI-112G & CEI-224G and CMIS

- August 9, 2023 – OIF Achieves Milestone with Largest Ever Multi-Vendor Interoperability Demo at ECOC 2023, Featuring 39 Companies Accelerating Implementation of Next-Generation Capabilities

- February 22, 2023 – OIF Highlights 400ZR, Co-Packaging Architectures, CEI-112G & CEI-224G and CMIS Implementations Interoperability Among 30+ Global Companies; Hosts Special Anniversary Events at OFC 2023

- January 25, 2023 – OIF Hosts Largest Ever Multi-Vendor Interoperability Demonstration of the Solutions Accelerating Next-Generation Capabilities at OFC 2023; Celebrates 25 Years of Interoperability Work

- January 11, 2023 – OIF to Update Industry on Next-Generation Electrical and Optical Interface Projects, including 224 Gbps & Co-Packaging, at DesignCon 2023

- February 23, 2022 – OIF Members Demonstrate How Interoperability Accelerates Solutions for Today’s and Future Global Networks at OFC 2022

- August 27, 2021 – OIF Reveals New Common Electrical I/O Project to Strengthen an Open Ecosystem for Near Package Optics Architecture, Launches Management Track and Facebook joins Board of Directors at Q3 2021 Virtual Meeting

- June 7, 2021 – OIF Thought Leaders to Provide Updates on Co-Packaging, 400ZR, Electrical Data Rates and Transport SDN Projects at Global Conferences

- May 26, 2021 – OIF Reveals Three Innovative Projects – External Laser Small Form Factor Pluggable Module for Co-Packaged Optics, Artificial Intelligence for Enhanced Network Operations and CEI-112G-Linear – at Q2 2021 Virtual Meeting

- February 20, 2019 – OIF Members to Demonstrate Interoperability of Industry’s Hottest Technologies at OFC 2019

- June 12, 2018 – OIF Initiates New CEI-112G-XSR Project for D2D/D2OE Common Electrical Interface, Addresses Multiple Chip Integration

- Feb 21, 2018 – OIF Reveals OFC 2018 Interoperability Demo Plans

- Nov 29, 2017 – OIF Launches CEI-112G Projects, Forms Network Operator Working Group

Speaking

- DesignCon 2021 OIF Panel:“Interoperable Common Electrical I/O and Channel Standards – An OIF Perspective”

Tuesday, August 17, 2021 – 4:00-5:15 PDT

Moderator: Nathan Tracy, OIF VP of Marketing, TE Connectivity

Panelists: Pirooz Tooyserkani, Cisco (presenting for Gary Nicholl); Mike Li, OIF Board Member, Intel; Cathy Liu, Broadcom Inc.; Keysight Technologies (presented by Mike Li) - OFC 2021 OIF Panel: “Electrical Data Rates Keep Pushing Forward; An OIF Update”

Tuesday, June 08, 2021 – 11:00-12:00 PDT

Moderator: Nathan Tracy, OIF VP of Marketing, TE Connectivity

Panelists: David Stauffer, OIF Physical & Link Layer Working Group Chair, Kandou Bus SA; Gary Nicholl, OIF Secretary/Treasurer, Cisco; Cathy Liu, Broadcom Inc.; Mike Li, OIF Board Member, Intel and Thananya Baldwin, Keysight Technologies - DesignCon 2019 OIF Panel: “112Gbps Electrical Interfaces – An OIF update on CEI-112G”

Track: 08. Optimizing High-Speed Serial Design

Moderator: Nathan Tracy, OIF VP of Marketing, TE Connectivity

Panelists: Brian Holden, Kandou Bus; Cathy Liu, OIF Board Member, Broadcom Limited; Steve Sekel, OIF PLL Interoperability WG Chair, Keysight - NGON & DCI Europe 2018

- DesignCon 2018

Success Story

Fact Sheet

For more information, contact Dave Stauffer, Physical and Link Layer Working Group Chair at technicalquestions@oiforum.com.

For information on other OIF current projects, please see OIF Current Work

For public OIF Implementation Agreements, please see Implementation Agreements (IAs)